一种嵌入式FPGA存储电路及其控制方法

文献发布时间:2023-06-19 10:41:48

技术领域

本发明涉及存储器领域,尤指一种嵌入式FPGA存储电路及其控制方法。

背景技术

目前芯片集成的模块越来越多,并且种类不同,各个模块可能是模拟的,也可能是数字的,功率也有不同。FPGA(Field Programmable Gate Array,现场可编程逻辑门阵列)也加入到被集成的行列。FPGA具有可编程功能,可以大幅地提高芯片的性能。但是,它需用到大面积的存储器及逻辑单元,在设计上对成本,功耗,速度,稳定性都有非常高的要求。

发明内容

为了解决上述技术问题,本发明提供了一种嵌入式FPGA存储电路及其控制方法,降低FPGA中存储器及逻辑单元的功耗,提高FPGA中存储器及逻辑单元的稳定性。

为了达到本发明目的,本发明提供了一种嵌入式FPGA存储电路,包括:CMOS存储拓扑阵列、位线阵列和字线阵列,所述CMOS存储拓扑阵列包括M行×N列的存储器,所述位线阵列包括N个位线单元,字线阵列包括M个字线单元;每个字线单元控制一行存储器,每个位线单元控制一列存储器;

每个所述存储器包括相连的传输门和存储单元;

每个字线单元的字线P控制端与所在行的每个存储器的所述传输门的PMOS控制端相连;所述每个字线单元的字线N控制端与所在行的每个存储器的所述传输门的NMOS控制端相连;每个字线单元的本地线控制端与所在行的每个存储器的存储单元控制端相连;

每个位线单元的位线控制端与所在列的每个存储器的所述传输门的读写控制端相连。

优选地,所述字线单元包括:与非门、或非门、非门和与门;所述与非门的两个输入端分别连接字线控制端和字选择端;所述与非门的输出端作为字线N控制端;所述与非门的输出端经过非门的输出作为字线P控制端;所述与门的两个输入端分别连接字选择端和本地控制端;初始控制端与所述与门的输出端作为所述或非门的输入端;所述或非门的输出端作为本地线控制端。

优选地,所述传输门包括第一NMOS和第一PMOS,所述第一NMOS的源极与所述第一PMOS的源极相连作为写数据控制端;所述第一NMOS的栅极与所述第一PMOS的栅极其中一个连接第一电平,另一个连接第二电平,所述第一NMOS的漏极与所述第一PMOS的漏极作为读数据控制端;所述第一PMOS的栅极与对应的字线单元的字线P控制端相连;所述第一NMOS的栅极与所述字线单元的字线N控制端相连。

优选地,所述存储单元包括:第二PMOS、第三PMOS、第二NMOS和第三NMOS,所述第二PMOS的源极、第三PMOS的源极分别与对应的字线单元的本地线控制端相连,所述第二PMOS的漏极、第二NMOS的漏极、第三PMOS栅极与第三NMOS的栅极与所对应的传输门的写数据控制端相连,所述第二PMOS的栅极、第二NMOS的栅极、第三PMOS漏极与第三NMOS的漏极相连作为所述存储器的输出端;所述第二NMOS的源极和第三NMOS的源极接地。

优选地,所述位线单元包括第四PMOS,所述第四PMOS的栅极连接位冲电控制端,所述第四PMOS的源极作为读数据控制端;所述第四PMOS的漏极连接电源。

本发明还提供一种嵌入式FPGA存储电路的控制方法,包括:

当接收到对任一行存储器的写控制信号时,对应行的字线单元控制所对应的一行存储器的传输门导通,存储在每个位线单元中的数据通过传输门传输至对应的存储单元中;

当接收到对任一行存储器的读控制信号时,对应行的字线单元控制所对应的一行存储器的传输门导通,存储在对应的存储单元中的数据通过传输门传输至对应的位线单元中。

优选地,所述存储器的输出端将输出的数据传输至FPGA。

优选地,当接收到对任一行存储器的写控制信号时,通过字线单元的本地线控制端给位线单元的位冲电控制端充电。

优选地,所述位线单元的字线N控制端为高电平时,所述传输门导通,当位线单元的字线N控制端为低高电平时,所述传输门断开。

与现有技术相比,本发明提供的存储电路,低功耗,稳定性高。

本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在说明书、权利要求书以及附图中所特别指出的结构来实现和获得。

附图说明

附图用来提供对本发明技术方案的进一步理解,并且构成说明书的一部分,与本申请的实施例一起用于解释本发明的技术方案,并不构成对本发明技术方案的限制。

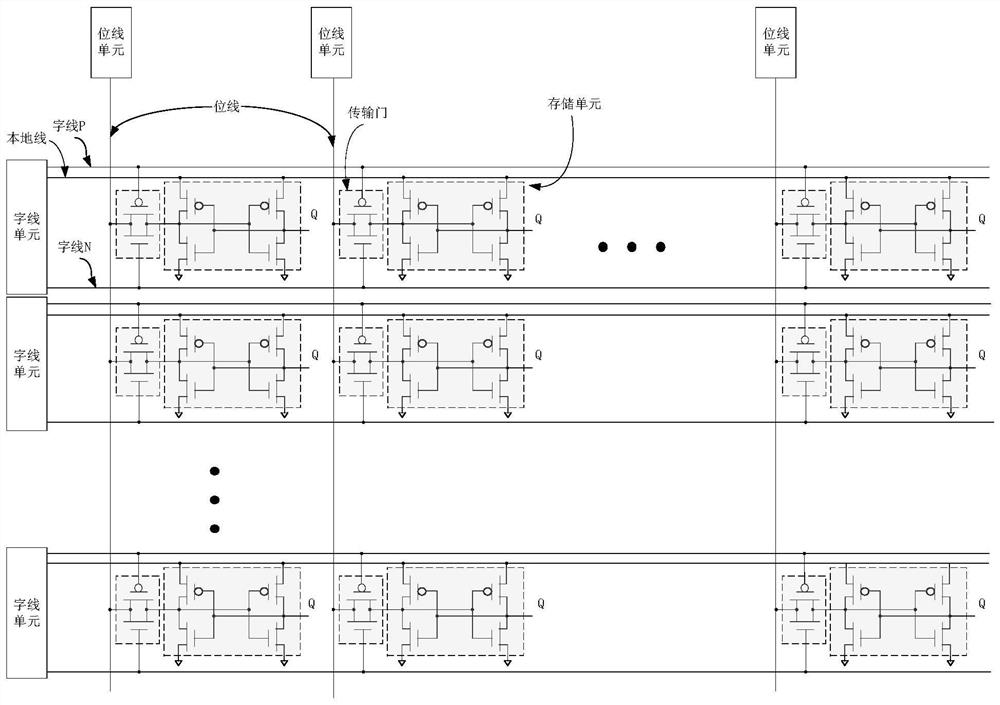

图1为本发明实施例的嵌入式FPGA存储电路的示意图;

图2为本发明实施例的字线单元逻辑原理图;

图3为本发明实施例的位线单元逻辑原理图;

图4为本发明实施例的存储单元逻辑原理图

图5为本发明实施例的写数据1的时序图;

图6为本发明实施例的写数据0的时序图;

图7为本发明实施例的读数据1的时序图;

图8为本发明实施例的读数据0的时序图;

图9为本发明实施例的初始操作的时序图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,下文中将结合附图对本发明的实施例进行详细说明。需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互任意组合。

在附图的流程图示出的步骤可以在诸如一组计算机可执行指令的计算机系统中执行。并且,虽然在流程图中示出了逻辑顺序,但是在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤。

如图1所示,本发明实施例提供一种嵌入式FPGA存储电路,包括:CMOS存储拓扑阵列、位线阵列和字线阵列,所述CMOS存储拓扑阵列包括M行×N列的存储器,所述位线阵列包括N个位线单元,字线阵列包括M个字线单元;每个字线单元控制一行存储器,每个位线单元控制一列存储器;

每个所述存储器包括相连的传输门和存储单元;

每个字线单元的字线P控制端与所在行的每个存储器的所述传输门的PMOS控制端相连;所述每个字线单元的字线N控制端与所在行的每个存储器的所述传输门的NMOS控制端相连;每个字线单元的本地线控制端与所在行的每个存储器的存储单元控制端相连;

每个位线单元的位线控制端与所在列的每个存储器的所述传输门的读写控制端相连。

如图1所示,本发明实施例采用M x N的CMOS存储的拓扑结构。这个拓扑结构中有Mx N个存储单元和M x N个传输门。每个存储单元可以存储0或1,Q是其输出端。输出端可以用来控制后级逻辑电路。每个存储单元通过传输门,位线单元和字线单元进行读写操作。存储器的读写操作总是按字来操作的。在N个字中,在一个时间中只有一个字可以做读或写操作。但存储单元的输出Q是总是有效输出,全时间驱动后级逻辑电路。这也是本发明实施例的存储电路与传统的存储器结构最主要的区别。

如图2所示,本发明实施例中,所述字线单元包括:与非门、或非门、非门和与门;所述与非门的两个输入端分别连接字线控制端和字选择端;所述与非门的输出端作为字线N控制端;所述与非门的输出端经过非门的输出作为字线P控制端;所述与门的两个输入端分别连接字选择端和本地控制端;初始控制端与所述与门的输出端作为所述或非门的输入端;所述或非门的输出端作为本地线控制端。

如图3所示,本发明实施例中,所述传输门包括第一NMOS(101)和第一PMOS(201),所述第一NMOS(101)的源极与所述第一PMOS(201)的源极相连作为写数据控制端;所述第一NMOS(101)的栅极与所述第一PMOS(201)的栅极其中一个连接第一电平,另一个连接第二电平,所述第一NMOS(101)的漏极与所述第一PMOS(201)的漏极作为读数据控制端;所述第一PMOS(201)的栅极与对应的字线单元的字线P控制端相连;所述第一NMOS(101)的栅极与所述字线单元的字线N控制端相连。

本发明实施例中,第一NMOS栅极和第一PMOS栅极一个是正逻辑,另一个是负逻辑,一个接到高,另一个接到低。

如图4所示,本发明实施例中,所述存储单元包括:第二PMOS(202)、第三PMOS(203)、第二NMOS(102)和第三NMOS(103),所述第二PMOS(202)的源极、第三PMOS(203)的源极分别与对应的字线单元的本地线控制端相连,所述第二PMOS(202)的漏极、第二NMOS(102)的漏极、第三PMOS(203)栅极与第三NMOS(103)的栅极与所对应的传输门的写数据控制端相连,所述第二PMOS(202)的栅极、第二NMOS(102)的栅极、第三PMOS(203)漏极与第三NMOS(103)的漏极相连作为所述存储器的输出端;所述第二NMOS(102)的源极和第三NMOS的源极接地。

本发明实施例中,存储单元是四管存储结构。它具有稳定的二元状态。在嵌入式FPGA存储中,存储单元可以直接用于输出驱动后级逻电点路。由于存储单元具有稳定性,需要通过位线阵列和字线阵列来控制它的写和读。本发明实施例采用拓扑结构的存储单元,以及对应的本地线,位线阵列和字线阵列进行读和写操作,以及相关的初始化操作。本发明实施例所有读和写操作都是通过位线阵列和字线阵列来进行的。一般有地址译码来产生字选择信号,一旦某个字线单元被选中后,这个字线单元对应的所有存储单元都会做同样的操作。读和写信号是通过位线单元读出或写入存储单元的。

如图3所示,本发明实施例中,所述位线单元包括第四PMOS(204),所述第四PMOS(204)的栅极连接位冲电控制端,所述第四PMOS(204)的源极作为读数据控制端;所述第四PMOS(204)的漏极连接电源。

本发明实施例还提供一种嵌入式FPGA存储电路的控制方法,包括:

当接收到对任一行存储器的写控制信号时,对应行的字线单元控制所对应的一行存储器的传输门导通,存储在每个位线单元中的数据通过传输门传输至对应的存储单元中;

当接收到对任一行存储器的读控制信号时,对应行的字线单元控制所对应的一行存储器的传输门导通,存储在对应的存储单元中的数据通过传输门传输至对应的位线单元中。

本发明实施例中,所述存储器的输出端将输出的数据传输至FPGA。

本发明实施例中,当接收到对任一行存储器的写控制信号时,通过字线单元的本地线控制端给位线单元的位冲电控制端充电。

本发明实施例中,所述位线单元的字线N控制端为高电平时,所述传输门导通,当位线单元的字线N控制端为低高电平时,所述传输门断开。

实施例一

如图5所示,本实施例说明写1操作的过程:

假设写1之前存储单元中的数据是0,往这个存储单元写1操做。时序图如图5所示。对字线写,字线控制必须为高(1),写控制N必须为高(1),写控制P必须为低(0),这样写数据可以传到存储单元。但存储单元是由很稳定的四管存储结构,本实施例能够保证由外面的传到存储单元的数据信号不足够强去反转内部的存储单元,必须通过本地控制加上时序来帮助完成这一步骤。具体步骤分为三步:1.本地控制为高(1),它实际的作用就是关掉本地线。当本地线关掉后,存储单元就会变得很弱,由外面传到存储单元的数据信号就足够强。2.本地控制为低(0),本地线开始上电后,内部的存储单元就会反转到同外部数据一样的状态。3.本地线稳定以后,完成写操作。

实施例二

如图6所示,本实施例说明写0操作的过程:

假设写0之前存储单元中的数据是1,往这个存储单元写0操做。时序图如图6所示。对字线选择,字线控制必须为高(1),写控制N必须为高(1),写控制P必须为低(0),这样写数据可以传到存储单元。但存储单元是由很稳定的四管存储结构,本实施例能够保证由外面的传到存储单元的数据信号不足够强去反转内部的存储单元,必须通过本地控制加上时序来帮助完成这一步骤。具体步骤分为三步:1.本地控制为高(1),它实际的作用就是关掉本地线。当本地线关掉后,存储单元就会变得很弱,由外面的传到存储单元的数据信号就足够强。2.本地控制为低(0),本地线开始上电后,内部的存储单元就会反转到同外部数据一样的状态。3.本地线稳定以后,完成写操作。

实施例三

如图7所示,本实施例说明读1操作的过程:

假设存储单元中的数据是1,读1操做。时序图如图7所示。对字线选择,字线控制必须为高(1),写控制N必须为高(0),写控制P必须为低(1),这样写数据就传不到内部。为了检测到内部存储单元的数据,必须对位线进行冲电。冲电以后的位线是高电平(1),但存储单元是由很稳定的四管存储结构,本实施例能够保证由外面的传到存储单元的数据信号不足够强去反转内部的存储单元。这样就可以用这一特性来检测存储单元的数据信号。具体步骤分为三步:1.冲电控制为高(1),它实际的作用就是对位线进行冲电。2.冲电控制为低(0)后,位线冲电结束,这时,位线电平为高(1)。由很稳定的四管存储结构和保证由外面的传到存储单元的数据信号不足够强去反转内部的存储单元。但冲电结束后,存储单元的数据信号就会影响到位线电平。由于时读1操作,存储单元的数据也是1,位线电平保持1。3.位线稳定以后,就可以完成读操作。

实施例四

如图8所示,本实施例说明读0操作的过程:

假设存储单元中的数据是0,读0操做。时序图如图8所示。对字线选择,字线控制必须为高(1),写控制N必须为低(0),写控制P必须为高(1),这样写数据就传不到内部。为了检测到内部存储单元的数据,必须对位线进行冲电。冲电以后的位线是高电平(1),但存储单元是由很稳定的四管存储结构,本实施例能够保证由外面的传到存储单元的数据信号不足够强去反转内部的存储单元。这样就可以用这一特性来检测存储单元的数据信号。具体步骤分为三步:1.冲电控制为高(1),它实际的作用就是对位线进行冲电。2.冲电控制为低(0)后,位线冲电结束,这时,位线电平为高(1)。由很稳定的四管存储结构和设计保证由外面的传到存储单元的数据信号不够足够强去反转内部的存储单元。但冲电结束后,存储单元的数据信号就会影响到位线电平。由于时读0操作,存储单元的数据也是0,位线电平就会逐渐地放电变成0。3.位线稳定以后,就可以完成读操作。

实施例五

如图9所示,本实施例说明初始操作的过程:

嵌入式FPGA的存储单元是直接控制后端的逻辑单元,而四管存储结构决定了它在初始上电以后,它的逻辑不是确定的。即它的初始值可能是高(1),也可能是低(0)。因而后端的逻辑单元也是不确定的。这可能造成功能上的限制,更有可能造成很大的启动电流,造成启动失败或损坏芯片。必须进行初始操作。初始控制是直接逻辑联系到系统复位。一但初始控制为高(1)时,所有字线选择,字线控制都为高,写控制N必须为高(1),写控制P必须为低(0),写数据都为低(0),(本实施例可以设定初始值),位冲电控制为低(0)。实际上强制所有存储单元写0。时序图如图9所示。

本领域普通技术人员可以理解,上文中所公开方法中的全部或某些步骤、系统、装置中的功能模块/单元可以被实施为软件、固件、硬件及其适当的组合。在硬件实施方式中,在以上描述中提及的功能模块/单元之间的划分不一定对应于物理组件的划分;例如,一个物理组件可以具有多个功能,或者一个功能或步骤可以由若干物理组件合作执行。某些组件或所有组件可以被实施为由处理器,如数字信号处理器或微处理器执行的软件,或者被实施为硬件,或者被实施为集成电路,如专用集成电路。这样的软件可以分布在计算机可读介质上,计算机可读介质可以包括计算机存储介质(或非暂时性介质)和通信介质(或暂时性介质)。如本领域普通技术人员公知的,术语计算机存储介质包括在用于存储信息(诸如计算机可读指令、数据结构、程序模块或其他数据)的任何方法或技术中实施的易失性和非易失性、可移除和不可移除介质。计算机存储介质包括但不限于RAM、ROM、EEPROM、闪存或其他存储器技术、CD-ROM、数字多功能盘(DVD)或其他光盘存储、磁盒、磁带、磁盘存储或其他磁存储装置、或者可以用于存储期望的信息并且可以被计算机访问的任何其他的介质。此外,本领域普通技术人员公知的是,通信介质通常包含计算机可读指令、数据结构、程序模块或者诸如载波或其他传输机制之类的调制数据信号中的其他数据,并且可包括任何信息递送介质。

- 一种嵌入式FPGA存储电路及其控制方法

- 嵌入式FPGA IP核顶层电路图自动生成方法、装置及存储介质