存储器器件及其形成方法和存储器单元

文献发布时间:2023-06-19 10:51:07

技术领域

本申请的实施例涉及存储器器件及其形成方法和存储器单元。

背景技术

存储器器件用于在半导体器件和系统中存储信息。非易失性存储器器件即使在断电后也能够保留数据。非易失性存储器器件的实例包括闪存、铁电随机存取存储器(FRAM)、磁随机存取存储器(MRAM)、电阻式随机存取存储器(RRAM)和相变存储器(PCM)。MRAM、RRAM、FRAM和PCM有时称为新兴存储器器件。

发明内容

本申请的一些实施例提供了一种存储器器件,包括:存储器单元阵列,具有以多个行和多个列布置的多个存储器单元,存储器单元的每行与字线相关联,存储器单元的每列与位线和源极线相关联,其中,每个存储器单元包括:存储器件,耦接至所述位线,所述存储器件响应于所述位线处的位线信号在第一电阻状态和第二电阻状态之间是可选择的;以及选择器件,与所述存储器器件串联连接并且耦接至所述源极线,所述选择器件配置为响应于所述字线处的字线信号提供至所述存储器器件的访问;字线驱动器,耦接至所述字线并且配置为生成所述字线信号;位线驱动器,耦接至所述位线并且配置为生成所述位线信号;其中,第一数量的所述源极线并联连接。

本申请的另一些实施例提供了一种形成存储器器件的方法,包括:提供以多个行和多个列布置的多个存储器单元,每个存储器单元具有串联连接的存储器器件和选择器件;提供多个字线,每个字线对应于所述多个行中的一个;提供多个位线,每个位线对应于所述多个列中的一个;提供多个源极线,每个源极线对应于所述多个列中的一个;以及并联连接所述第一数量的多个源极线。

本申请的又一些实施例提供了一种存储器单元,包括:存储器器件,响应于位线信号在第一电阻状态和第二电阻状态之间是可选择的;以及晶体管,与所述存储器器件串联连接,所述晶体管配置为响应于位于所述晶体管的栅极处的字线信号提供至所述存储器器件的访问;以及多个源极线,连接至所述晶体管,其中,所述多个源极线彼此并联连接。

附图说明

当结合附图进行阅读时,从以下详细描述可最佳理解本发明的各个方面。应该指出,根据工业中的标准实践,各个部件未按比例绘制。实际上,为了清楚的讨论,各个部件的尺寸可以任意地增大或减小。另外,附图示出为本发明的实施例的实例,而不旨在限制本发明。

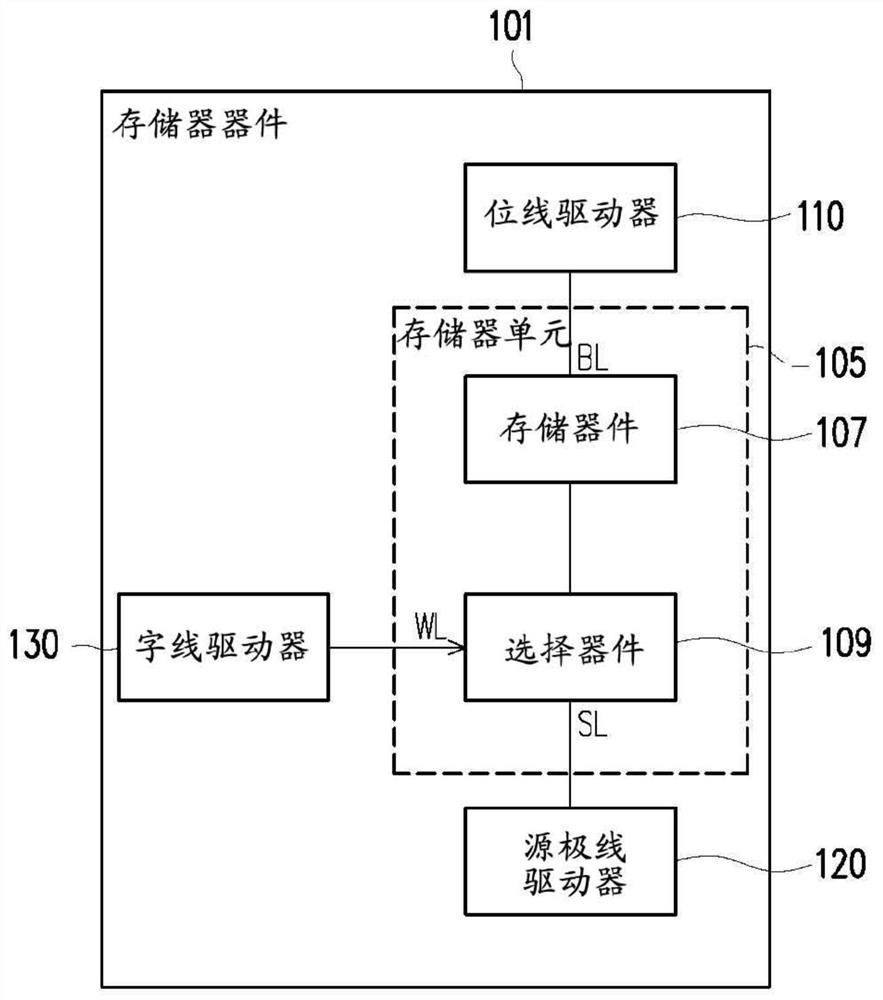

图1是示出根据一些实施例的示例性存储器器件的框图。

图2是示出根据一些实施例的图1的存储器单元的截面图。

图3是示出根据一些实施例的用于确定要并联连接的源极线金属轨道的数量的方法的流程图。

图4是示出根据一些实施例的并联连接的源极线金属轨道的结构图。

图5是示出根据一些实施例的并联连接的源极线金属轨道的结构图。

图6是示出根据一些实施例的并联连接的源极线金属轨道的结构图。

图7是示出根据一些实施例的并联连接的源极线金属轨道的结构图。

图8是示出根据一些实施例的方法的流程图。

具体实施方式

以下公开内容提供了许多用于实现所提供主题的不同特征的不同实施例或实例。下面描述了组件和布置的具体实例以简化本发明。当然,这些仅仅是实例,而不旨在限制本发明。例如,以下描述中,在第二部件上方或者上形成第一部件可以包括第一部件和第二部件直接接触形成的实施例,并且也可以包括在第一部件和第二部件之间可以形成额外的部件,从而使得第一部件和第二部件可以不直接接触的实施例。此外,本发明可在各个实例中重复参考标号和/或字符。该重复是为了简单和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

而且,为了便于描述,在此可以使用诸如“在…之下”、“在…下方”、“下部”、“在…之上”、“上部”等空间相对术语,以描述如图所示的一个元件或部件与另一个(或另一些)元件或部件的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的不同方位。器件可以以其他方式定向(旋转90度或在其他方位上),而本文使用的空间相对描述符可以同样地作出相应的解释。

在存储器器件中,运载源极线信号的底部金属轨道通常更薄,与运载位线信号的上部金属轨道相比具有更小的间距。因此,运载源极线信号的金属轨道比运载位线信号的金属轨道具有更高的薄膜电阻(即,电阻率除以膜厚度)。位线和源极线之间的不平衡导致对相同列中的存储器单元产生不同的读取电流。

根据本发明的一些方面,多个源极线金属轨道并联连接以减小薄膜电阻,从而改善位线和源极线之间的平衡。在一些实例中,并联连接的多个源极线金属轨道对应于存储器单元的不同的列。因此,当通过不同的字线信号选择位于相同列中的两个不同的存储器单元时,感测的读取电流彼此接近。可以基于位线金属轨道的薄膜电阻和源极线金属轨道的薄膜电阻确定要并联连接的源极线金属轨道的数量。

图1是示出根据一些实施例的示例性存储器器件101的框图。在所示的实例中,此外,示例性存储器器件101包括存储器单元105、字线驱动器130、位线驱动器110和源极线驱动器120。

此外,存储器单元105还包括存储器件107和选择器件109。在一些实施例中,存储器件可以是用于MRAM的磁阻材料。在一些实施例中,存储器件可以是用于RRAM的电阻材料。在一些实施例中,存储器件可以是用于PCM的相变材料。在一些实施例中,存储器件可以是用于DRAM的电容器。其他存储器类型在本发明的范围内。

存储器单元105是形成存储器单元阵列的多个存储器单元105的一个实例。为了简单起见,图1中仅示出了存储器单元105;典型的存储器单元阵列将包括更多的存储器单元。多个存储器单元可以以行和/或列布置在存储器单元阵列内。位于存储器单元阵列的行内的存储器单元105可操作地耦接至字线(WL),而位于存储器单元阵列的列内的存储器单元105可操作地耦接至位线(BL)和对应的源极线(SL)。多个存储器单元105分别与由字线(WL)和位线(BL)的交点限定的地址相关联。

如上所述,存储器单元105包括存储器件107和选择器件109。字线驱动器130基于字线地址生成字线(WL)信号。字线(WL)信号提供至选择器件109。选择器件109基于字线(WL)信号选择性地导通或截止。在一些实施例中,选择器件109是n型选择器件。在一些实例中,选择器件109是n型场效应晶体管(FET)。选择器件109在字线(WL)信号处于逻辑高(即,“1”)时导通,而在字线(WL)信号处于逻辑低(即,“0”)时截止。在一些实施例中,选择器件109是p型选择器件。在一些实例中,选择器件109是p型FET。选择器件109在字线(WL)信号处于逻辑低时导通,并且在字线(WL)信号处于逻辑高时截止。

存储器件107耦接至连接至位线驱动器110的位线。选择器件109耦接至连接至源极线驱动器120的源极线。通过激活字线,选择器件119导通,从而允许源极线耦接至存储器件107。这样,当激活字线时,存储器件107耦接在其对应的位线和源极线之间。存储器件107具有在低电阻状态和高电阻状态之间切换的电阻状态。电阻状态指示存储在存储器件107内的数据值(例如,“1”或“0”)。

通过选择性地将信号施加至存储器单元阵列的字线、位线和源极线,可以对多个存储器单元中所选存储器单元(例如,存储器单元105)实施成形、设置、复位和读取操作。例如,在写入操作中,写入电流流过存储器件107,从而使得存储器件107从低电阻状态切换至高电阻状态,反之亦然,从而将数据位写入并且存储在存储器单元105中。另一方面,在读取操作中,读取电流流过存储器件107,并且读取电流对应于存储器件107的任一高电阻状态或低电阻状态。感测放大器(未示出)可以将读取电流与参考电流相比以感测存储在存储器单元105中的数据位。感测放大器放大感测的数据位的电平并且输出放大的数据位,从而使得可以从中读取存储在存储器单元105中的数据位。

图2是示出根据一些实施例的图1的存储器单元105的截面图。在所示的实例中,存储器单元105包括存储器件107以及两个选择器件109a和109b。具体地,存储器件107是磁性隧道结(MTJ)107,而两个选择器件109a和109b是两个晶体管109a和109b,但是也可以采用其他器件。

磁性随机存取存储器(MRAM)具有两个或多个电阻状态,这取决于两层或更多层磁性材料(诸如铁磁材料)之间的磁化对准状态。可以将存储器单元的电阻与参考相比以确定存储器单元的电阻状态。更具体地,MRAM在具有由薄绝缘膜分隔开的两个叠加的磁性材料层的存储器单元处存储数据。分层结构形成MRAM单元的MTJ。这两层包括在固定磁场对准方向上永久磁化的磁性层(该层称为“固定层”)和可变磁化的磁性层(该层称为“自由层”)。可以在相对于永久磁化层的两个取向中的一个上磁化自由层。这两个取向具有通过MTJ的叠加层的明显不同的串联电阻的特征。可改变层的磁场取向可以与永久磁体层的磁场取向相同对准(并联)或与永久磁体层的磁场取向相反对准(反向并联)。并联对准状态具有相对更低的电阻,并且反向并联对准状态具有更高的电阻。

在所示实例中,MTJ 107通过垂直互连通道(通孔)V5 245垂直连接至位于MTJ 107之上的金属轨道M6 236。MTJ 107通过底部电极通孔(BEVA)244垂直连接至位于MTJ 107之下的金属轨道M4 234。BEVA 244用于将形态运载至MTJ 107。金属轨道234通过通孔V3 243进一步垂直连接至金属轨道M3 233。金属轨道M3 233通过通孔V2 242进一步垂直连接至金属轨道M2 232。金属轨道M2 232通过通孔V1 241进一步垂直连接至金属轨道M1 231a。金属轨道M1 231a通过通孔V0 240进一步垂直连接至金属轨道M0 230a。金属轨道M0 230a通过通孔VD 246b进一步垂直连接金属接触(MD)轨道MD 211b。

晶体管109a和109b设置在有源区域201中。对于晶体管109a,栅极接触(MG)轨道221a用作栅极接触件,金属接触轨道211a用作源极接触件,并且金属接触轨道211b用作漏极接触件。对于晶体管109b,栅极接触轨道221b用作栅极接触件,金属接触轨道211c用作源极接触件,并且金属接触轨道211b用作漏极接触件。因此,MTJ 107连接至晶体管109a和109b。金属接触轨道211a通过通孔VD 246a垂直连接至金属轨道M0230a。同样地,金属接触轨道211c通过通孔VD 246c垂直连接至金属轨道M0 230c。

在示出的实例中,将字线信号施加至金属轨道M1 231b。金属轨道M1231b通过未示出的连接路径连接至栅极接触轨道221a和221b。因此,施加至金属轨道M1 231b的字线信号可以基于字线信号选择性地导通或截止晶体管109a和109b。

将位线信号施加至金属轨道236。当晶体管109a和109b导通时,读取电流流过金属轨道M6 236、MTJ 107、晶体管109a/109b至金属轨道M0230a/230c。因此,通过将读取电流与参考电流相比,可以在金属轨道M0230a或金属轨道230c上感测源极线信号。

然而,底部金属轨道(例如,M0金属轨道230a、230b和230c)更薄,与上部金属轨道(例如,金属轨道236)相比具有更小的间距。因此,运载源极线信号的金属轨道(例如,230a和230c)具有比运载位线信号的金属轨道(例如,236)更高的薄膜电阻。当通过不同的字线信号选择位于相同列中的两个不同的存储器单元105时,由于薄膜电阻中的不同(即,位线和源极线之间的不平衡),感测的读取电流是不同的(即,不平衡)。具体地,虽然用于第一存储器单元105的位线金属轨道的长度(L

根据公开的方面,对应于存储器单元105的不同列的多个源极线金属轨道可以并联连接以减小薄膜电阻,从而改善位线和源极线之间的平衡。结果,当通过不同的字线信号选择位于相同列中的两个不同的存储器单元105时,感测的读取电流彼此接近。可以根据下面参考图3描述的方法确定要并联连接的源极线金属轨道的数量。

图3是示出根据一些实施例的用于确定要连接的源极线金属轨道的数量的方法的流程图。在所示的流程图中,在步骤312中,获得位线金属轨道的第一薄膜电阻(R1)。在一个实例中,R1是金属轨道M6 236的薄膜电阻,并且R1为844欧姆。在步骤314中,获得源极线金属轨道的第二薄膜电阻(R2)。在一个实例中,R2是金属轨道230a的薄膜电阻,并且R2为6877欧姆。在步骤316中,基于第一薄膜电阻(R1)和第二薄膜电阻(R2)确定并联连接的第一数量的源极线(N)。在一个实例中,将N确定为小于或等于(R2/R1)的最大整数。因此,在R1为844欧姆并且R2为6877欧姆的实例中,将N确定为8。换句话说,八个源极线金属轨道并联连接,并且等效薄膜电阻变为859.6欧姆(即,R2/N;6877欧姆的八分之一),接近R1(即,844欧姆)。因此,改善了位线和源极线之间的平衡。

图4是示出根据一些实施例的并联连接的源极线金属轨道的结构图。在该示出的实例中,连接多个(即,正整数N)源极线金属轨道230。具体地,示例性存储器器件包括布置在阵列中的存储器单元105等。每个存储器单元105包括作为存储器器件的MTJ 107和作为选择器件的两个晶体管109a和109b等。字线信号选择性地导通或截止晶体管109a和109b。通过施加位线信号,读取电流流过MTJ 107,并且可以在源极线金属轨道230上感测。

在该示出的实例中,源极线金属轨道230是如图2所示的金属轨道M0230。源极线金属轨道230在X方向上延伸,并且借助于如图2所示在Y方向上延伸的金属接触轨道MD 211并联连接。在一个实例中,Y方向垂直于X方向。在所示的实例中,源极线金属轨道230位于金属接触轨道MD 211之上,并且多个(即,N)源极线金属轨道230通过通孔VD 246连接至每个金属接触轨道MD 211。因此,多个(即,N)源极线金属轨道230并联连接。

当读取电流流至金属接触轨道211时,存在多个(即,N)电流路径411-1至411-N。多个(即,N)电流路径411-1至411-N减小了源极线电阻,从而改善了源极线和位线之间的平衡。

源极线金属轨道230的数量(N)和金属接触轨道MD 211的数量仅用于说明。在一个实例中,源极线金属轨道230的数量(N)为8。在另一实例中,源极线金属轨道230的数量(N)为2。在一个实例中,金属接触轨道MD 211的数量为512。金属接触轨道的其他数量在本发明的范围内。

图5是示出根据一些实施例的并联连接的源极线金属轨道的结构图。在该示出的实例中,多个(即,N

在该示出的实例中,源极线金属轨道230是如图2所示的金属轨道M0230。源极线金属轨道230在X方向上延伸,并且借助于如图2所示在Y方向上延伸的金属接触轨道MD 211在每组内并联连接。在一个实例中,Y方向垂直于X方向。源极线金属轨道230位于金属接触轨道MD 211之上,并且位于每组内的多个(即,N

当读取电流流至金属接触轨道MD 211时,存在多个(即,N

位于每组内的源极线金属轨道230的数量(即,N

图6是示出根据一些实施例的并联连接的源极线金属轨道的结构图。在该示出的实例中,源极线金属轨道通过位于源极线金属轨道之上而不是之下的金属轨道并联连接。

具体地,连接多个(即,N)源极线金属轨道230。源极线金属轨道230是如图2所示的金属轨道M0 230。源极线金属轨道230在X方向上延伸,并且借助于如图2所示在Y方向上延伸的金属轨道M1 231并联连接。在一个实例中,Y方向垂直于X方向。源极线金属轨道230位于金属轨道M1 231下方,并且多个(即,N)源极线金属轨道230通过如图2所示的通孔V0 240连接至每个金属轨道M1 231。因此,多个(即,N)源极线金属轨道230并联连接。

当读取电流流至金属轨道M1 231时,存在多个(即,N)电流路径。多个(即,N)电流路径减小了源极线电阻,从而改善了源极线和位线之间的平衡。

同样地,在附图中示出的源极线金属轨道230的具体数量(N)和金属轨道M1 231的数量仅用于说明。在一个实例中,源极线金属轨道230的数量(N)为8。在另一实例中,源极线金属轨道230的数量(N)为2。在一个实例中,金属轨道M1 231的数量为512。金属轨道的其他数量在本发明的范围内。

图7是示出根据一些实施例的并联连接的源极线金属轨道的结构图。在该示出的实例中,借助于金属轨道并联连接的源极线金属轨道不必彼此相邻。

具体地,连接多个(即,N+2)源极线金属轨道230。源极线金属轨道230是如图2所示的金属轨道M0 230。源极线金属轨道230在X方向上延伸。在那些源极线金属轨道230之中,存在并联连接的多个(即,N)源极线金属轨道230-c和未连接的两个源极线金属轨道230-1和230-2。N个源极线金属轨道230-c借助于如图2所示的在Y方向上延伸的金属接触轨道MD211并联连接。在一个实例中,Y方向垂直于X方向。N个源极线金属轨道230-c位于金属接触轨道MD 211之上并且通过如图2所示的通孔VD 246连接至每个金属接触轨道MD 211。因此,N个源极线金属轨道230-c并联连接。N个源极线金属轨道230-c不必彼此相邻。

当读取电流流至金属接触轨道MD 211时,存在多个(即,N)电流路径(未示出)。多个(即,N)电流路径减小了源极线电阻,从而改善了源极线和位线之间的平衡。

同样地,源极线金属轨道230-c的具体数量(N)和金属接触轨道MD211的数量用于说明。在一个实例中,源极线金属轨道230-c的数量(N)为8。在另一实例中,源极线金属轨道230-c的数量(N)为2。在一个实例中,金属接触轨道MD 211的数量为512。金属接触轨道的其他数量在本发明的范围内。

图8是示出根据一些实施例的方法的流程图。在步骤812中,提供多个存储器单元。多个存储器单元以多个行和多个列布置。每个存储器单元具有串联连接的存储器件和选择器件。在步骤814中,提供多个字线。每个字线对应于多个行中的一个。在步骤816中,提供多个位线。每个位线对应于多个列中的一个。在步骤818中,提供多个源极线。每个源极线对应于多个列中的一个。在步骤820中,第一数量的多个源极线并联连接。在一些实施例中,基于与多个位线相关联的第一薄膜电阻和与多个源极线相关联的第二薄膜电阻确定第一数量。

根据一些公开的实施例,提供了存储器器件。该存储器器件包括存储器单元阵列,该存储器单元阵列具有以多个行和多个列布置的多个存储器单元,存储器单元的每行与字线相关联,存储器单元的每列与位线和源极线相关联。每个存储器单元包括:存储器件,耦接至位线,存储器件响应于位线处的位线信号在第一电阻状态和第二电阻状态之间是可选择的;以及选择器件,与存储器件串联连接并且耦接至源极线,选择器件配置为响应于字线处的字线信号提供至存储器件的访问。存储器器件还包括:字线驱动器,耦接至字线并且配置为生成字线信号;以及位线驱动器,耦接至位线并且配置为生成位线信号。第一数量的源极线并联连接。

根据一些公开的实施例,提供了方法。该方法包括:提供以多个行和多个列布置的多个存储器单元,每个存储器单元具有串联连接的存储器件和选择器件;提供多个字线,每个字线对应于多个行中的一个;提供多个位线,每个位线对应于多个列中的一个;提供多个源极线,每个源极线对应于多个列中的一个;以及并联连接第一数量的多个源极线。

根据进一步公开的实施例,提供了一种存储器单元。该存储器单元包括:存储器件,响应于位线信号在第一电阻状态和第二电阻状态之间是可选择的;以及晶体管,与存储器器件串联连接,晶体管配置为响应于位于晶体管的栅极处的字线信号提供至存储器件的访问;以及多个源极线,连接至晶体管,其中多个源极线彼此并联连接。

本申请的一些实施例提供了一种存储器器件,包括:存储器单元阵列,具有以多个行和多个列布置的多个存储器单元,存储器单元的每行与字线相关联,存储器单元的每列与位线和源极线相关联,其中,每个存储器单元包括:存储器件,耦接至所述位线,所述存储器件响应于所述位线处的位线信号在第一电阻状态和第二电阻状态之间是可选择的;以及选择器件,与所述存储器器件串联连接并且耦接至所述源极线,所述选择器件配置为响应于所述字线处的字线信号提供至所述存储器器件的访问;字线驱动器,耦接至所述字线并且配置为生成所述字线信号;位线驱动器,耦接至所述位线并且配置为生成所述位线信号;其中,第一数量的所述源极线并联连接。在一些实施例中,所述位线是第一金属轨道,并且所述源极线是第二金属轨道。在一些实施例中,所述第二金属轨道位于所述第一金属轨道的下方。在一些实施例中,所述第一金属轨道具有第一薄膜电阻,并且所述第二金属轨道具有第二薄膜电阻,并且基于所述第一薄膜电阻和所述第二薄膜电阻确定所述第一数量。在一些实施例中,将所述第一数量确定为小于或等于所述第二薄膜电阻与所述第一薄膜电阻的比率的最大整数。在一些实施例中,所述第一数量的源极线通过位于所述第一数量的源极线下方的第三金属接触轨道并联连接。在一些实施例中,所述第一数量的源极线通过位于所述第一数量的源极线之上的第三金属轨道并联连接。在一些实施例中,所述第一数量的源极线位于彼此相邻的列中。在一些实施例中,所述第一数量的源极线位于并非全部彼此相邻的列中。在一些实施例中,所述存储器件是磁性隧道结MTT,所述第一电阻状态是高电阻状态,并且所述第二电阻状态是低电阻状态。在一些实施例中,所述选择器件是具有耦接至所述字线的栅极的晶体管。

本申请的另一些实施例提供了一种形成存储器器件的方法,包括:提供以多个行和多个列布置的多个存储器单元,每个存储器单元具有串联连接的存储器器件和选择器件;提供多个字线,每个字线对应于所述多个行中的一个;提供多个位线,每个位线对应于所述多个列中的一个;提供多个源极线,每个源极线对应于所述多个列中的一个;以及并联连接所述第一数量的多个源极线。在一些实施例中,基于与所述多个位线相关联的第一薄膜电阻和与所述多个源极线相关联的第二薄膜电阻确定所述第一数量。在一些实施例中,并联连接所述第一数量的多个源极线包括:在所述第一数量的多个源极线的下方提供与所述第一数量的多个源极线相交的多个金属接触轨道;以及通过所述多个金属接触轨道并联连接所述第一数量的多个源极线。在一些实施例中,并联连接所述第一数量的多个源极线包括:在所述第一数量的多个源极线之上提供与所述第一数量的多个源极线相交的多个第三金属轨道;以及通过所述多个第三金属轨道并联连接所述第一数量的多个源极线。

本申请的又一些实施例提供了一种存储器单元,包括:存储器器件,响应于位线信号在第一电阻状态和第二电阻状态之间是可选择的;以及晶体管,与所述存储器器件串联连接,所述晶体管配置为响应于位于所述晶体管的栅极处的字线信号提供至所述存储器器件的访问;以及多个源极线,连接至所述晶体管,其中,所述多个源极线彼此并联连接。在一些实施例中,存储器单元还包括:位线,耦接至所述存储器器件,其中,所述位线包括第一金属轨道;并且其中,所述多个源极线包括并联连接的多个第二金属轨道。在一些实施例中,所述第一金属轨道具有第一薄膜电阻,并且所述第二金属轨道具有第二薄膜电阻,所述多个源极线包括基于所述第一薄膜电阻和所述第二薄膜电阻确定的第一数量的源极线。在一些实施例中,所述多个源极线通过位于所述多个源极线下方的金属接触轨道并联连接。在一些实施例中,所述多个源极线通过位于所述多个源极线之上的第三金属轨道并联连接。

本发明概述了各个实施例,使得本领域技术人员可以更好地理解本发明的方面。本领域技术人员应该理解,它们可以容易地使用本发明作为基础来设计或修改用于实施与本文所介绍实施例相同的目的和/或实现相同优势的其它工艺和结构。本领域技术人员也应该意识到,这种等同构造并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,本文中它们可以做出多种变化、替换以及改变。

- 存储器单元、存储器器件及其形成方法

- 存储器单元、存储器件及其形成方法