比较器

文献发布时间:2023-06-19 11:06:50

技术领域

本申请涉及集成电路技术领域,特别是涉及一种比较器。

背景技术

现有的比较器被广泛应用于各个领域,比较器的一个要求为能够快速得到比较的结果,以便于快速进行下一步处理,例如,当检测到过流异常时,希望尽快对该异常情况处理。但由于比较器本身固有的延时,经常会导致处理的速度滞后,比较器的翻转速度较慢,这个延时主要是比较器中第一级运放电路的输出端及第二级运放电路的输出端的节点充放电的延时所导致,譬如,当第一待比较电压VP大于第二待比较电压VN时,第一级运放电路的输出端的电路下拉,会从一个较高的电位下拉至地电位,当第一待比较电压VP小于第二待比较电压VN时,第一级运放电路的输出端的电位会被重新上拉至高电位。此外,比较器中第一级运放电路的输出信号的快速变化会耦合到第一待比较电压VP,形成回踢噪声(kickback noise),不仅会对待比较电压造成干扰,还可能导致输出错误翻转。

发明内容

基于此,有必要针对现有技术中的比较器存在的由于输出端充放电延时而导致的比较器处理速度滞后、翻转速度较慢的问题,及会形成回踢噪声,对待比较电压造成干扰,导致输出错误翻转等问题进行改进。

为了实现上述目的,一方面,本发明提供了一种比较器,包括:

第一级运放电路、第二级运放电路、偏置电路及钳位电路;其中,

所述第一级运放电路包括两个电压输入端及一个电压输出端;所述第一级运放电路的两个电压输入端用于输入待比较电压;

所述第二级运放电路与所述偏置电路及所述第一级运放电路的电压输出端相连接;

所述钳位电路与所述第一级运放电路的电压输出端相连接,用于将所述第一级运放电路的电压输出端的最高电压钳位至预设电压。

上述比较器中通过增设钳位电路,可以将第一级运放电路的电压输出端的最高电压钳位至预设电压,在比较器工作过程中第一级运放电路的电压输出端的电压变化幅度较小,可以减小第一级运放电路的电压输出端的放电延时,从而提高比较器的翻转速度;此外,由于第一级运放电路的电压输出端的电压变化幅度较小,第一级运放电路的电压输出端的电压变化对输入的待比较电压的耦合作用也相应减小,可以减小输入的待比较电压的回踢噪声,避免对待比较电压造成干扰,确保输出的正确性;同时,上述比较器还具有结构简单,成本低及容易实现等优点。

在其中一个实施例中,所述第一级运放电路包括:第一PMOS管、第二PMOS管、第三PMOS管、第一NMOS管及第二NMOS管;其中,

所述第一PMOS管的栅极与第一待比较电压相连接;

所述第二PMOS管的栅极与第二待比较电压相连接;

所述第三PMOS管的栅极与所述偏置电路相连接,所述第三PMOS管的漏极与所述第一PMOS管的源极及所述第二PMOS管的源极相连接;

所述第一NMOS管的栅极与漏极短接,并与所述第一PMOS管的漏极相连接,所述第一NMOS管的源极接地;

所述第二NMOS管的栅极与所述第一NMOS管的栅极相连接,所述第二NMOS管的漏极与所述第二PMOS管的漏极相连接作为所述第一级运放电路的电压输出端,所述第二NMOS管的源极接地。

在其中一个实施例中,所述钳位电路包括第一开关管,所述第一开关管的控制端及电流输入端与所述第一级运放电路的电压输出端相连接,所述第一开关管的电流输出端与所述第二NMOS的栅极相连接。

在其中一个实施例中,所述第一开关管包括NMOS管。

在其中一个实施例中,所述钳位电路还包括第二开关管,所述第二开关管的控制端及电流输入端与所述第一级运放的电压输出端相连接,所述第二开关管的电流输出端与所述第二级运放的电压输出端相连接。

在其中一个示例中,所述第二级运放电路包括:第四PMOS管及第三NMOS管;其中,

所述第四PMOS管的栅极与所述偏置电路相连接;

所述第三NMOS管的栅极与所述第一级运放电路的电压输出端相连接,所述第三NMOS管的漏极与所述第四PMOS管的漏极相连接后作为所述第二级运放电路的电压输出端,所述第三NMOS管的源极接地。

在其中一个示例中,所述偏置电路包括:第五PMOS管及电流源;其中,

所述第五PMOS管的栅极与所述第一级运放电路及所述第二级运放电路相连接,所述第五PMOS管的漏极与所述电流源相连接。

在其中一个实施例中,所述钳位电路包括开关管,所述开关管的控制端及电流输入端与所述第一级运放电路的电压输出端相连接,所述开关管的电流输出端与所述第二级运放电路的输出端相连接。

在其中一个实施例中,所述开关管包括NMOS管。

在其中一个实施例中,所述钳位电路包括开关管,所述开关管的电流输入端与所述第一级运放电路的电压输出端相连接,所述开关管的控制端与偏置电压相连接,所述开关管的电流输出端接地。

在其中一个实施例中,所述开关管包括PMOS管或PNP型晶体管。

在其中一个实施例中,所述钳位电路包括:第一开关管、第二开关管及第三开关管;其中,

所述第一开关管的电流输入端与所述第一级运放电路的电压输出端相连接,所述第一开关管的控制端与所述第二开关管的电流输出端及所述第三开关管的电流输入端相连接;

所述第二开关管的控制端接所述偏置电路;

所述第三开关管的控制端与所述第三开关管的电流输入端短接,所述第三开关管的电路输出端接地。

在其中一个实施例中,所述第一开关管包括PMOS管或PNP型晶体管,所述第二开关管包括PMOS管,所述第三开关管包括NMOS管。

附图说明

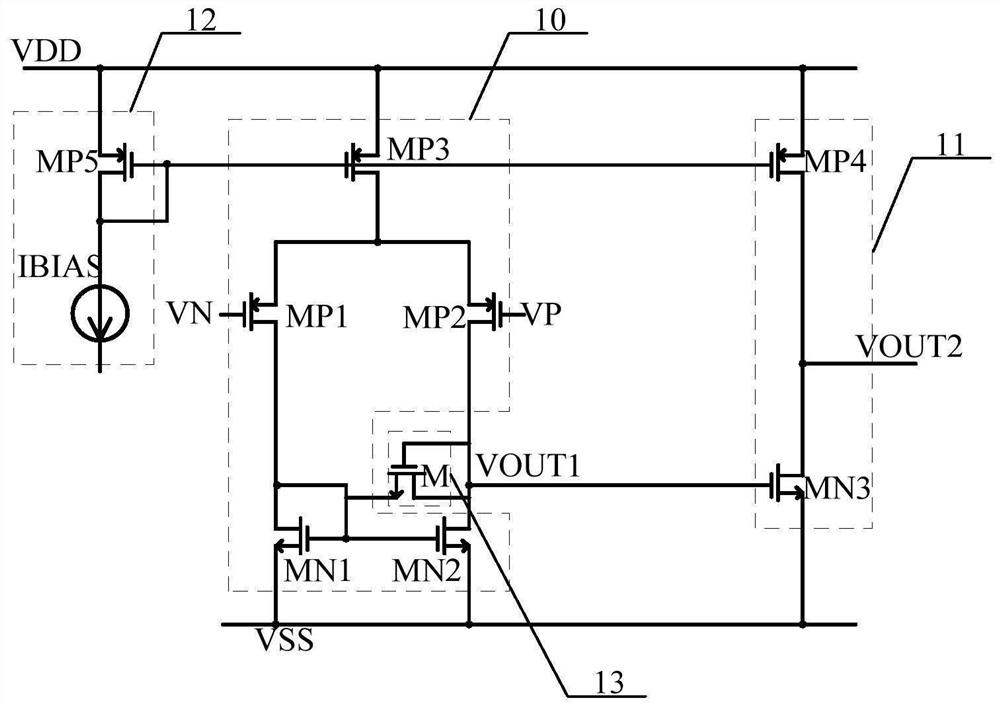

图1至图5为本发明不同实施例中的比较器的电路图。

附图标记说明:

10 第一级运放电路

11 第二级运放电路

12 偏置电路

13 钳位电路

具体实施方式

为了便于理解本申请,下面将参照相关附图对本申请进行更全面的描述。附图中给出了本申请的首选实施例。但是,本申请可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本申请的公开内容更加透彻全面。

需要说明的是,当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件并与之结合为一体,或者可能同时存在居中元件。本文所使用的术语“安装”、“一端”、“另一端”以及类似的表述只是为了说明的目的。

除非另有定义,本文所使用的所有的技术和科学术语与属于本申请的技术领域的技术人员通常理解的含义相同。本文中在本申请的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本申请。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

在一个实施例中,如图1至图5所示,本发明一种比较器,包括:第一级运放电路10、第二级运放电路11、偏置电路12及钳位电路13;其中,第一级运放电路10包括两个电压输入端及一个电压输出端;第一级运放电路10的两个电压输入端用于输入待比较电压;第二级运放电路11与偏置电路12及第一级运放电路10的电压输出端相连接;钳位电路13与第一级运放电路10的电压输出端相连接,钳位电路13用于将第一级运放电路10的电压输出端的最高电压钳位至预设电压。

具体的,第一运放电路10的一个输入端用于输入第一待比较电压VN,第一运放电路10的另一个输入端用于输入第二待比较电压VP。

在一个示例中,请继续参阅图1至图5,第一级运放电路10包括:第一PMOS管MP1、第二PMOS管MP2、第三PMOS管MP3、第一NMOS管MN1及第二NMOS管MN2;其中,第一PMOS管MP1的栅极与第一待比较电压VN相连接;第二PMOS管MP2的栅极与第二待比较电压VP相连接;第三PMOS管MP3的栅极与偏置电路12相连接,第三PMOS管MP3的漏极与第一PMOS管MP1的源极及第二PMOS管MP2的源极相连接;第一NMOS管MN1的栅极与漏极短接,并与第一PMOS管MP1的漏极相连接,第一NMOS管MN1的源极接地;第二NMOS管MN2的栅极与第一NMOS管MN1的栅极相连接,第二NMOS管MN2的漏极与第二PMOS管MP2的漏极相连接作为第一级运放电路10的电压输出端,用于输出第一输出信号VOUT1,第二NMOS管MN 2的源极接地。

在一个示例中,第二级运放电路11包括:第四PMOS管MP4及第三NMOS管MN3;其中,第四PMOS管MP4的栅极与偏置电路12相连接;第三NMOS管MN3的栅极与第一级运放电路10的电压输出端相连接,第三NMOS管MN3的漏极与第四PMOS管MP4的漏极相连接后作为第二级运放电路11的电压输出端,用于输出第二输出信号VOUT2,第三NMOS管MN3的源极接地。

在一个示例中,偏置电路12包括:第五PMOS管MP5及电流源IBIAS;其中,第五PMOS管MP5的栅极与第一级运放电路10及第二级运放电路11相连接,第五PMOS管MP5的栅极、漏极与电流源相连接IBIAS。具体的,第五PMOS管MP5的栅极与第三PMOS管MP3的栅极及第四PMOS管MP4的栅极相连接。

在一个可选的示例中,如图1所示,钳位电路13可以包括第一开关管M,第一开关管M的控制端及电流输入端与第一级运放电路10的电压输出端相连接,第一开关管M的电流输出端与第二NMOS管MN2的栅极相连接。该示例中,钳位电路13可以实现对第一级运放电路10的输出端进行钳位,可以将第一级运放电路10的输出端的最高电压钳位至Vgs(第一开关管M的栅源电压)+Vgsn1(第一NMOS管MN1的栅源电压),这样,当第二待比较电压VP大于第一待比较电压VN的时候,第一级运放电路10的输出端的电压VOUT1将不再需要从高电位(VDD-Vonp3-Vonp2,Vonp3和Vonp2分别为MP3管和MP2管的导通电压值)拉到地电位,而是从大约Vgs+Vgsn1的电压(Vgs+Vgsn1小于VDD-Vonp3-Vonp2)向下拉,这样对第一级运放电路10的放电延时就被减小,从而提高比较器的翻转电压;同时,第一级运放电压10的变化幅度更小,故第一级运放电路10的变化对第一待比较电压VN及第二待比较电压VP的耦合作用也相应减小,第一待比较电压VN及第二待比较电压VP受到回踢噪声的干扰更小。

在一个示例中,第一开关管M可以包括NMOS管。

在另一个可选的示例中,如图3所示,钳位电路13可以包括第一开关管M1,第一开关管M1的控制端及电流输入端与第一级运放电路10的电压输出端相连接,第一开关管M1的电流输出端与第二NMOS管MN2的栅极相连接;第二开关管M2的控制端及电流输入端与第一级运放电路10的电压输出端相连接,第二开关管M2的电流输出端与第二级运放电路11的电压输出端相连接。

在一个示例中,第一开关管M1可以包括NMOS管,第二开关管M2可以包括NMOS管。

在又一个可选的示例中,如图2所示,钳位电路可以包括开关管M,开关管M的控制端及电流输入端与第一级运放电路10的电压输出端相连接,开关管M的电流输出端与第二级运放电路11的输出端相连接。该示例中,钳位电路13可以实现对第一级运放电路10的输出端进行钳位,可以将第一级运放电路10的输出端的最高电压钳位至Vgs(开关管M的栅源电压)+Vdsn3(第三NMOS管MN3的漏源电压),这样,当第二待比较电压VP大于第一待比较电压VN的时候,第一级运放电路10的输出端的电压VOUT1将不再需要从高电位(VDD-Vonp3-Vonp2,Vonp3和Vonp2分别为MP3管和MP2管的导通电压值)拉到地电位,而是从大约Vgs+Vdsn3的电压向下拉,这样对第一级运放电路10的放电延时就被减小,从而提高比较器的翻转电压;同时,第一级运放电压10的变化幅度更小,故第一级运放电路10的变化对第一待比较电压VN及第二待比较电压VP的耦合作用也相应减小,第一待比较电压VN及第二待比较电压VP受到回踢噪声的干扰更小。

再回到图3的结构,结合对图1和图2的分析可知,第一级运放电路10的输出端的电压VOUT1被钳位到Vgsm1+Vgsn1(Vgsm1为M1管的栅源电压,Vgsn1为MN1管的栅源电压)与Vgsm2+Vdsn3(Vgsm2为M2管的栅源电压,Vdsn3为MN3管的漏源电压)之间更小的那个值,进一步减小了第一级运放电路10的输出端的电压VOUT1的变化幅度,从而进一步提高了比较器的翻转速度并减小了回踢噪声。

在一个示例中,开关管M可以包括NMOS管。

在又一可选的示例中,如图4所示,钳位电路13可以包括开关管M,开关管M的电流输入端与第一级运放电路10的电压输出端相连接,开关管的控制端与偏置电压VBIAS相连接,开关管M的电流输出端接地。该示例中,钳位电路13可以实现对第一级运放电路10的输出端进行钳位,可以将第一级运放电路10的输出端的最高电压钳位至Vgs1(开关管M的栅源电压)+VBIAS,这样,当第二待比较电压VP大于第一待比较电压VN的时候,第一级运放电路10的输出端的电压VOUT1将不再需要从高电位(VDD-Vonp3-Vonp2,Vonp3和Vonp2分别为MP3管和MP2管的导通电压值)拉到地电位,而是从大约Vgs1+VBIAS的电压向下拉(Vgs1+VBIAS小于VDD-Vonp3-Vonp2),且将第一级运放电路10的输出端钳位至的电压可以通过调节VBIAS进行改变,这样对第一级运放电路10的放电延时就被减小,从而提高比较器的翻转速度;同时,第一级运放电压10的变化幅度更小,故第一级运放电路10的变化对第一待比较电压VN及第二待比较电压VP的耦合作用也相应减小,第一待比较电压VN及第二待比较电压VP受到回踢噪声的干扰更小。

在一个示例中,开关管M可以包括PMOS管或PNP型晶体管。

在又一可选的示例中,如图5所示,钳位电路13可以包括:第一开关管M1、第二开关管M2及第三开关管M3;其中,第一开关管M1的电流输入端与第一级运放电路10的电压输出端相连接,第一开关管M1的控制端与第二开关管M2的电流输出端及第三开关管M3的电流输入端相连接;第二开关管M2的控制端接偏置电路12,具体的,第二开关管M2的控制端接第五PMOS管的栅极;第三开关管M3的控制端与第三开关管M3的电流输入端短接,第三开关管M3的电路输出端接地。在该示例中,第一开关管M1的栅极连接的偏置电压VBIAS即为第三开关管M3的栅源电压。通过选择具有不同的沟道宽长比的第一开关管M1、第二开关管M2或第三开关管M3可以调节钳位电路13将第一级运放电路10的电压输出端钳位至的预设的钳位电压;譬如,增加第一开关管M1、第二开关M2或第三开关M3的宽长比,可以降低偏置电压VBIAS,进而减小钳位电压;减小第一开关管M1、第二开关M2或第三开关M3的宽长比,可以增加偏置电压VBIAS,进而增加钳位电压。

在一个示例中,第一开关管M1包括PMOS管或PNP型晶体管,第二开关管M2包括PMOS管,第三开关管M3包括NMOS管。

上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

以上所述实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请专利的保护范围应以所附权利要求为准。

- 比较器电路和包括比较器电路的开关控制装置

- 比较器、AD转换器、固态成像器件、电子装置及比较器控制方法