低噪声电路

文献发布时间:2023-06-19 11:21:00

技术领域

本发明总体涉及一种低噪声电路,特别涉及一种D类放大器和驱动级。

背景技术

在音频扬声器电路中使用三电平(tri-level)的电流数模转换器(Digital-to-Analog Converter,DAC),当信号较小时,因为大部分电流数模转换器单元没有连接到D类放大器,所以可以改进D类型放大器的信噪比(Signal-to-Noise Ratio,SNR)。然而,当三电平的电流DAC被使用时,需要附加电路(例如电流到电压转换器和可编程增益放大器)放置在三电平电流DAC和D类放大器之间,用于信号转换和DC电平偏移。这些附件电路对信号造成额外的噪声。

此外,在音频扬声器电路的驱动级,快速的转换速率具有较少的失真,较好的效率和较少的开关损耗,然而,快速的转换速率也导致严重的电磁干扰(Electromagneticinterference,EMI)问题。

发明内容

本发明的目的是提供一种低噪声电路。

本发明一方面提供一低噪声电路,其包括电流数字至模拟转换器DAC和D类放大器,其中,电流数字至模拟转换器,用于接收数字信号,以产生电流信号;D类放大器,与所述电流数字至模拟转换器耦接,用于从所述电流数字至模拟转换器接收所述电流信号,并且放大所述电流信号,以产生输出信号;驱动级,与所述D类放大器耦接,用于根据所述D类放大器的输出信号产生驱动信号,所述驱动级中晶体管的栅极-漏极电容是可编程的。

本发明另一方面提供一电路,其包括:DAC,放大器和驱动级。该DAC用于接收数字信号以产生模拟信号,该放大器与所述DAC耦接,用于根据模拟信号产生输出信号,并且该驱动级用于根据该放大器的输出信号产生驱动信号,其中,该驱动级中晶体管的栅极-漏极是可编程的。

本发明另一方面提供一电路,其包括:DAC,放大器和共模电压产生器。DAC用于接收数字信号以产生模拟信号,放大器用于根据该模拟信号产生输出信号,以及共模电压产生器与所述数字至模拟转换器和所述放大器耦接,用于产生共模电压并输出给所述数字至模拟转换器和所述放大器,具体可用于根据该放大器所使用的共模电压,为DAC产生一共模电压。

本发明实施例提供的电路中在驱动级中提供功率晶体管的可编程栅极-漏极电容,可以控制转换速率。

在阅读了在各种附图和附图中示出的优选实施例的以下详细描述之后,本发明的这些和其它目的无疑将在本领域技术人员中变得显而易见。

附图说明

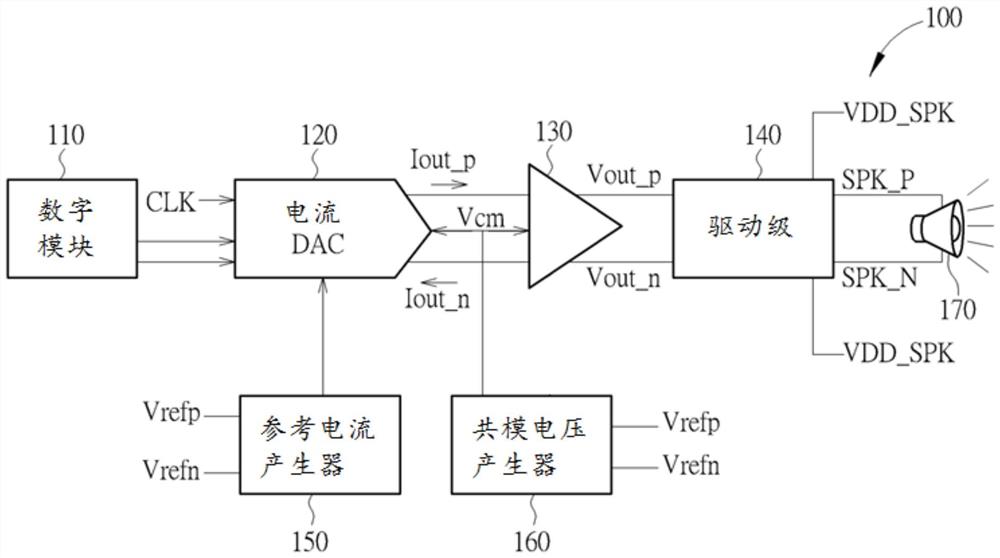

图1是本发明一实施例提供的电路示意图;

图2是本发明一实施例提供的电流DAC,D类放大器和驱动级的示意图;

图3是本发明一实施例提供的驱动级的示意图。

具体实施方式

在如下描述和权利要求中所使用的特定术语涉及特定的元件。本领域技术人员应该理解的是,电子设备厂商可以给元件以不同的命名。本发明不想以命名来区分元件,而是以功能来区分元件。在后续的描述和权利要求中,术语“包括”是一种开放式限定,其应该理解为“包含但不限于…”。而且,术语“耦接”表示直接或者间接的电连接,该连接可以表示为一直接的电连接,或者表示为通过其他装置或者连接的一间接的电连接。

本发明提供一种低噪声电路,其中D类放大器能直接的接收电流DAC产生的电流,以及在驱动级中的功率晶体管的栅极-漏极电容(gate-drain capacitance)是可编程的,可以解决一些技术问题。

请参考图1,图1是本发明一实施例示出的电路100的示意图。如图1所示,电路100包括数字模块110,电流DAC120,D类放大器130,驱动级140,参考电流产生器150,共模电压产生器160,和扬声器170。在该实施例中,电流DAC120是三电平电流DAC,D类放大器130直接的接收从电流DAC120输出的电流信号Iout_p和Iout_n,以产生输出信号Vout_p和Vout_n(电压输出)给驱动级140,其中,D类放大器130的输入端可以直接耦接电流DAC120的输出端。

在图1所示出的电路100的操作中,首先,数字模块110产生数字音频信号到电流DAC120,并且电流DAC120接收时钟信号CLK,参考电流产生器150产生的参考电流和数字音频信号,以产生两个电流信号Iout_p和Iout_n。然后,D类放大器130接收电流信号Iout_p和Iout_n,以产生输出信号Vout_p和Vout_n,并且驱动级140根据D类放大器130的输出信号Vout_p和Vout_n产生驱动信号SPK_P和SPK_N,以驱动扬声器170。此外,参考电流产生器150根据至少两个参考电压Vrefp和Vrefn(DC电压)产生参考电流,并且共模电压产生器160产生共模电压Vcm给该电流DAC120和D类放大器130,其中,共模电压Vcm是两个参考电压Vrefp和Vrefn的平均电压(即Vcm=(Vrefn+Vrefp)/2)),该共模电压Vcm被电流DAC120所使用。

与背景技术中描述的传统电路相比,图1所示实施例在电流DAC120和D类放大器130之间不具有电流到电压转换器和可编程增益放大器,因此,附加噪声能够被减少。此外,因为电流DAC120和驱动级140的供电电压不相同(驱动级140由供电电压VDD_SPK和VSS_SPK供电,并且供电电压VDD_SPK比较大(例如4.5V或者9V),以支持扬声器170的较大输出功率;电流DAC120的供电电压的值可以与两个参考电压Vrefp和Vrefn的值相同),由于D类放大器130的反馈环路,所以直接的移除电流到电压转换器和可编程增益放大器可能引起电流DAC120输出节点上不合适的DC电压,以及电流DAC120的净空(headroom)被减少。它也可以导致电流DAC120的不平衡的PMOS和NMOS输出阻抗。所以,本发明的主题之一是提供D类放大器130的设计和电流DAC120的共模电压设置,以解决问题。此外,由于本领域技术人员已知电流DAC120的内部电路和参考电压Vrefp和Vrefn,后续描述将重点集中在D类放大器130的设计上。

请参考图2,图2示出本发明实施例提供的电流DAC120,D类放大器130和驱动级140。如图2所示,D类放大器130具有两级D类结构,D类放大器130包括第一积分级和第二积分级,其中运算放大器212和214和两个电容器C11和C12作为第一积分级(integrationstage),运算放大器222和224,两个电阻器R21和R22,两个电容器C21和C22作为第二积分级,比较器232和234用于根据第一积分级的输出和第二积分级的输出,产生脉冲宽度调制(Pulse Width Modulation,PWM)信号;以及增益放大器(gain amplifier)242和244作为驱动级140以产生驱动信号SPK_P和SPK_N,以及将增益放大器242和244的输出反馈至电流DAC120输入间的反馈环路上的电阻器R

在图2所示实施例中,电流DAC120的共模电压Vcm能被共模电压产生器160直接提供,其中Vcm与运算放大器212和运算放大器214的第二输入节点上虚拟(virtual)接地电压相同,或者与运算放大器222和运算放大器224的第二输入节点上的虚拟接地电压相同。通过让D类放大器130的输入共模电压等于电流DAC120的共模电压,即使供电电压VDD_SPK变化,电流DAC120的净空也将不被影响,并且电流DAC120的输出阻抗能够一直保持不变。

在图2所示的实施例中,D类放大器130的输入共模电压直接的作为电流DAC120的共模电压Vcm,然而,本发明不限于此。在本发明的其他实施例中,只要根据D类放大器130的输入共模电压决定电流DAC120的共模电压Vcm,电流DAC120的共模电压Vcm和D类放大器130的输入共模电压具有预定的关系,替代设计就落在本发明的范围内。

图3示出本发明实施例提供的驱动级140。在图3中,驱动级140包括第一驱动电路和第二驱动电路,第一驱动电路用于接收输出信号Vout_p,p和Vout_p,n,以产生扬声器170的驱动信号SPK_P。第二驱动电路用于接收输出信号Vout_n,p和Vout_n,n,以产生扬声器170的驱动信号SPK_N,其中,输出信号Vout_p,p和Vout_p,n从输出信号Vout_p中产生,以及输出信号Vout_n,p和Vout_n,n从输出信号Vout_n中产生,如图1所示,以及它们属于不同的功率域(power domain)。可选的,比较器232的输出Vout_p耦接驱动PMOS晶体管的DC电平偏移器(DC Level Shifter)和驱动NMOS晶体管的DC电平偏移器,驱动PMOS晶体管的DC电平偏移器的输出(即Vout_p,p)用于驱动驱动级中的PMOS晶体管;驱动NMOS晶体管的DC电平偏移器的输出(即Vout_p,n)用于驱动驱动级中的NMOS晶体管;比较器234也可以有相似的连接关系,在此不再赘述。第一驱动电路包括PMOS MP1,NMOS MN1,第一开关电容电路,和第二开关电容电路,其中第一开关电容电路包括两个电容器C1和M1和相应的开关SW11和SW12,其中,开关SW11与电容器C1串联耦接,开关SW12与电容器M1串联耦接,且串联耦接的开关SW11与电容器C1与串联耦接的开关SW12与电容器M1并联,第二开关电容电路包括两个电容器C2和M2和相应的开关SW21和SW22,开关SW21与电容器C2串联耦接,开关SW22与电容器M2串联耦接,且串联耦接的开关SW21与电容器C2与串联耦接的开关SW22与电容器M2并联。第二驱动电路包括PMOS MP2,NMOS MN2,第三开关电容电路和第四开关电容电路,其中第三开关电容电路包括两个电容器C3和M3和相应的开关SW31和SW32,开关SW31与电容器C3串联耦接,开关SW32与电容器M3串联耦接,且串联耦接的开关SW31与电容器C3与串联耦接的开关SW32与电容器M3并联;第四开关电容电路包括两个电容器C4和M4和相应的开关SW41和SW42,开关SW41与电容器C4串联耦接,开关SW42与电容器M4串联耦接,且串联耦接的开关SW41与电容器C4与串联耦接的开关SW42与电容器M4并联。此外,图3中示出的“Cgd1”是PMOS MP1的寄生电容,“Cgd2”是NMOS MN1的寄生电容,其中,寄生电容可以是跨在栅极与漏极之间的栅极-漏极电容,其随着栅极、漏极的信号不同而改变。

开关SW11,SW12,SW21,SW22,SW31,SW32,SW41和SW42能够根据数字控制信号被导通(turn on)或者关断(turn off),以使得PMOS MP1和PMOS MP2和NMOS MN1和NMOS MN2具有适当的栅极-漏极电容(gate-drain capacitance)以获得理想的转换速率。例如,假定输出信号Vout_p,p从0V到10V,PMOS MP1的寄生电容Cgd1是900fF,以及驱动电流是5mA,驱动级140的驱动信号SPK_P从1V到9V的转换时间大约1.44ns,这是非常快的,从而引起严重的EMI。所以,开关SW11和/或SW12可以被导通来增加PMOS MP1的栅极-漏极电容,以增加转换时间,降低EMI。

通过使用驱动级140的PMOS/NMOS的可编程栅极-漏极电容,可以控制驱动信号的转换速率以具有适当的设置,并且效率和EMI问题之间的折衷能更灵活。

简要总结,在本发明的实施例中,D类放大器可以设计成直接从三电平电流DAC接收输出电流,以减小在小信号输入处的噪声,并且将传统的电流DAC和D类放大器之间的电流-电压转换器和可编程增益放大器去除,以减少额外的电路噪声。此外,在驱动级中提供功率晶体管的可编程栅极-漏极电容,以具有适当的转换速率设置。

虽然本发明已以较佳实施例揭露如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰,因此本发明的保护范围当以所附权利要求为准。

- 一种低噪声放大电路及具有该电路的低噪声放大器

- 低噪声放大电路以及低噪声放大器