控制片内终结器的方法和执行该方法的系统

文献发布时间:2023-06-19 11:21:00

本申请是基于2018年5月28日提交的、申请号为201810522583.2、发明创造名称为“控制片内终结器的方法和执行该方法的系统”的中国专利申请的分案申请。

相关申请的交叉引用

本申请要求于2017年5月29日提交的韩国专利申请No.10-2017-0066377和于2017年7月14日提交的韩国专利申请No.10-2017-0089692的优先权,所述申请的公开内容通过引用方式整体并入本文。

技术领域

概括地说,示例性实施例涉及半导体集成电路,并且更具体地说,涉及控制片内终结器的方法和执行该方法的系统。

背景技术

引入片内终结器(ODT)以通过减小发送器与接收器之间的信号反射来提高信号完整性。ODT电路可通过提供与传输线路的阻抗匹配的终结器电阻来减少信号反射。然而,如果实施ODT以提高信号完整性,则会增大功耗。

发明内容

本发明构思的至少一个实施例提供了一种控制能够降低功耗和提高信号完整性的ODT的方法。

本发明构思的至少一个实施例提供了一种执行控制能够降低功耗和提高信号完整性的ODT的方法的系统。

根据本发明构思的示例性实施例,一种控制包括多个存储器区块的多区块存储器系统中的片内终结器(ODT)的方法,所述方法包括:当多区块存储器系统上电时,使所述多个存储器区块的ODT电路进入初始状态;在写操作期间,启用所述多个存储器区块中的写目标存储器区块和非目标存储器区块的ODT电路;以及在读操作期间,在启用所述多个存储器区块中的非目标存储器区块的ODT电路的同时,禁用所述多个存储器区块中的读目标存储器区块的ODT电路。

根据本发明构思的示例性实施例,一种控制存储器装置中的片内终结器(ODT)的方法,所述方法包括:当存储器装置上电时,使存储器装置的ODT电路进入初始状态以具有第一电阻值;在相对于存储器装置的写操作期间启用ODT电路;以及在相对于存储器装置的读操作期间禁用ODT电路。

根据本发明构思的示例性实施例,一种存储器系统包括:包括多个存储器装置的多个存储器区块和被构造为控制所述多个存储器区块的存储器控制器。当所述存储器系统上电时,使所述多个存储器区块的片内终结器(ODT)电路进入初始状态;所述多个存储器区块的ODT电路在相对于所述多个存储器区块中的写目标存储器区块和非目标存储器区块的写操作期间启用;并且在读操作期间,在启用所述多个存储器区块中的非目标存储器区块的ODT电路的同时,所述多个存储器区块中的读目标存储器区块的ODT电路被禁用。

根据本发明构思的示例性实施例,一种存储器系统包括第一存储器区块和第二存储器区块。所述第一存储器区块包括连接至第一片内终结器(ODT)电路的多个第一存储器装置。所述第二存储器区块包括连接至第二ODT电路的多个第二存储器装置。在所述第一存储器区块的写操作期间启用所述第一ODT电路和第二ODT电路,并且在所述第一存储器区块的读操作期间禁用第一ODT电路并启用第二ODT电路。

根据示例性实施例的控制ODT的方法和执行所述方法的系统可通过静态ODT控制来降低功耗和提高信号完整性,以使得目标存储器区块和非目标存储器区块的ODT电路基本保持在启用状态,而读目标存储器区块的ODT电路在读操作期间被禁用。

附图说明

根据以下结合附图来理解的详细描述,将更清楚地理解本公开的示例性实施例。

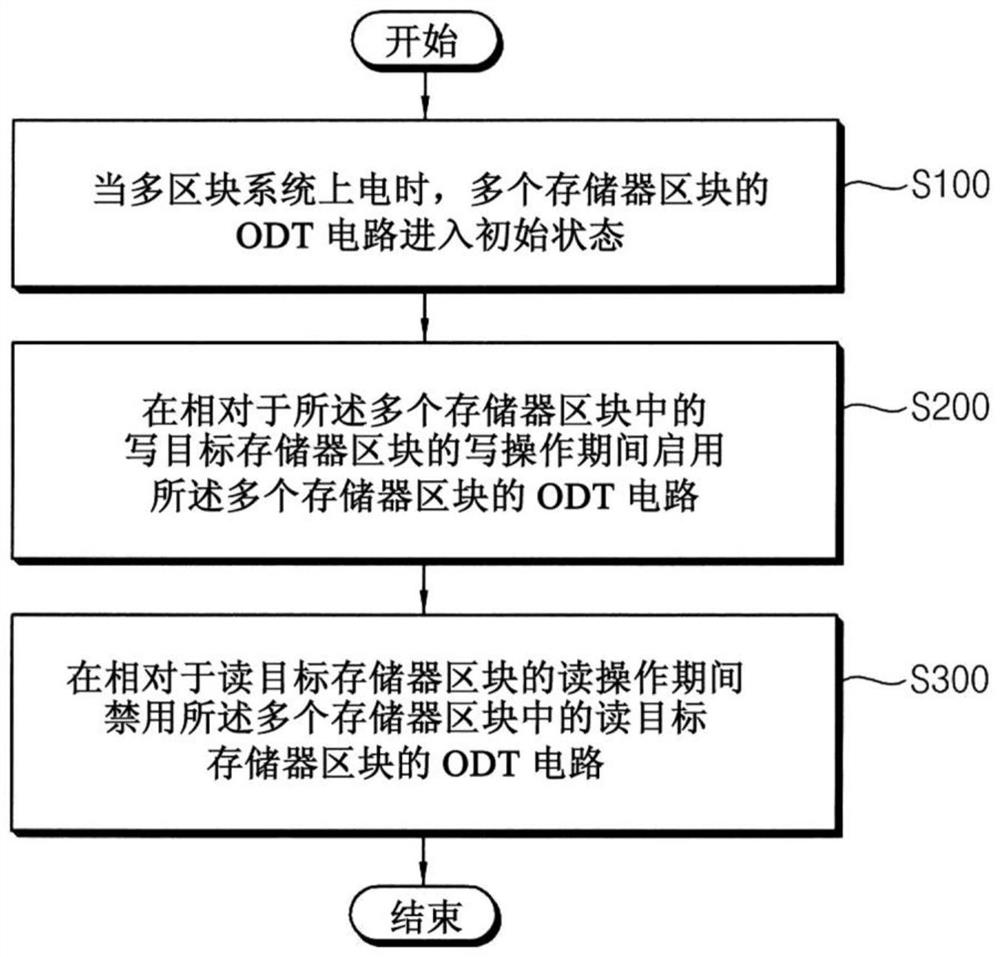

图1是示出根据本发明构思的示例性实施例的控制片内终结器(ODT)的方法的流程图。

图2是示出根据本发明构思的示例性实施例的控制ODT的方法的时序图。

图3是示出根据本发明构思的示例性实施例的多区块系统的框图。

图4是示出包括在图3的多区块系统中的存储器装置的示例性实施例的框图。

图5是示出根据本发明构思的示例性实施例的包括在图4的存储器装置中的数据输入-输出电路的实施例的框图。

图6是示出根据本发明构思的示例性实施例的包括在图5的数据输入-输出电路中的ODT电路的电路图。

图7、图8A和图8B是示出根据本发明构思的示例性实施例的在写操作中控制ODT的方法的示图。

图9和图10是示出根据本发明构思的示例性实施例的在读操作中控制ODT的方法的示图。

图11是示出根据本发明构思的示例性实施例的应用于控制ODT的方法的电阻设置的实施例的示图。

图12是用于描述对应于图11的电阻设置的写操作中的ODT电路的等效电阻的示图。

图13是用于描述对应于图11的电阻设置的读操作中的ODT电路的等效电阻的示图。

图14A和图14B是用于描述中间抽头的终结器(CTT)的示图。

图15A和图15B是用于描述第一伪漏极开路(POD)终结器的示图。

图16A和图16B是用于描述第二POD终结器的示图。

图17是示出根据本发明构思的示例性实施例的应用于控制ODT的方法的电阻设置的实施例的示图。

图18是示出根据本发明构思的示例性实施例的CAS命令的示图。

图19A和图19B是用于描述根据本发明构思的示例性实施例的用于ODT的模式寄存器的示图。

图20是示出根据本发明构思的示例性实施例的半导体存储器装置的结构图。

图21是示出根据本发明构思的示例性实施例的移动系统的框图。

具体实施方式

下文中,将参照其中示出了本发明构思的一些示例性实施例的附图来更完全地描述本发明构思。在附图中,相同的标号贯穿全文指代相同的元件。

图1是示出根据本发明构思的示例性实施例的控制片内终结器(ODT)的方法的流程图,并且图2是示出根据本发明构思的示例性实施例的控制ODT的方法的时序图。

图1和图2示出了在包括多个存储器区块的多区块系统中控制ODT的方法。下面将参照图3来描述多区块系统。在实施例中,存储器区块是连接至相同的芯片选择信号的一组存储器芯片。因此,当存在多个存储器区块时,各个存储器区块接收不同的芯片选择信号。在另一实施例中,用于给定存储器区块的该组存储器芯片共享相同的命令和控制信号。

参照图1,当多区块系统上电时,使多个存储器区块的ODT电路进入初始状态(S100)。例如,可通过将功率施加至ODT电路和将ODT电路中的每一个的电阻设为相同电阻值来执行使ODT电路进入初始状态的步骤。在相对于所述多个存储器区块中的写目标存储器区块的写操作期间启用所述多个存储器区块的ODT电路(S200)。例如,如果目前是写操作的目标的存储器区块的ODT电路中的一个由于存储器区块的先前读操作而目前禁用,则在写操作的期间启用ODT。此外,可以在实际写操作之前的一些时间启用目前是写操作的目标的存储器区块的ODT电路。在相对于读目标存储器区块的读操作期间禁用所述多个存储器区块中的读目标存储器区块的ODT电路(S300)。

存储器存取操作可包括写操作和读操作,并且可从诸如模式寄存器写操作、模式寄存器读操作、刷新操作等的其它操作中区分出存储器存取操作。就写操作而言,所述多个存储器区块可通过作为写操作的对象的写目标存储器区块和除了所述写目标存储器区块之外的非目标存储器区块来划分。例如,在写操作期间,将数据写至多个存储器区块中的一个(即,写目标存储器区块)并且不将数据写至其余存储器区块。就读操作而言,所述多个存储器区块可通过作为读操作的对象的读目标存储器区块和除了所述读目标存储器区块之外的非目标存储器区块来划分。例如,在读操作中,从多个存储器区块之一(即,读目标存储器区块)中读数据,并且不从其余存储器区块中读数据。写目标存储器区块或读目标存储器区块可简单地称作目标存储器区块。

参照图2,在当多区块系统上电的时间点T1,使所述多个存储器区块的ODT电路进入初始状态。在示例性实施例中,将所述多个存储器区块的ODT电路中的每一个设为在初始状态中具有第一电阻值。即使图2示出了ODT电路的启用时间点与上电时刻一致,可首先完成上电序列,并随后,在特定时间间隔过去之后,可使ODT电路进入初始状态。

在执行写操作时,在时间间隔T2至T3和T4至T5期间,包括写目标存储器区块和非目标存储器区块的存储器区块的所有ODT电路保持启用状态。在示例性实施例中,所述多个存储器区块的ODT电路保持初始状态,以在写操作期间具有第一电阻值。在另一示例性实施例中,在写操作期间,写目标存储器区块的ODT电路的电阻值从第一电阻值改变为与第一电阻值不同的第二电阻值。

在执行读操作时,在时间间隔T6至T7中,禁用所述读目标存储器区块的ODT电路,并且启用所述非目标存储器区块的ODT电路。在示例性实施例中,非目标存储器区块的ODT电路保持初始状态,以在读操作期间具有第一电阻值。即使图2示出了读目标存储器区块被禁用的时间间隔与读操作的时间间隔一致,读目标存储器区块被禁用的时间间隔也可小于读操作的时间间隔。换句话说,仅当通过数据输入-输出引脚输出读数据时禁用读目标存储器区块的ODT电路就足够了。例如,可仅当通过目标存储器区块的引脚输出来自目标存储器区块的读数据时禁用读目标存储器区块的ODT电路。

在当多区块系统断电时的时间点T8,电源被阻断(blocked),并且所有存储器区块的ODT电路被禁用。例如,在供应至ODT电路的功率之间可存在开关,并且可以通过断开所述开关来执行所述阻断。例如,当所述开关为晶体管时,所述开关可基于施加至所述晶体管的栅极的控制信号而开路。

如果仅启用目标存储器区块的ODT电路,并且禁用非目标存储器区块的ODT电路,则信号完整性可变差,这是因为注入非目标存储器区块中的信号的波未终止并因而可导致抖动。相反,根据本发明构思的至少一个实施例,除了读目标存储器区块的情况之外,通过启用ODT电路几乎总是可提高信号完整性。如将在下面描述的,即使总是启用非目标存储器区块的ODT电路,在伪漏极开路终结器的情况下也不导致待机功耗。

如果在写操作中启用并且在读操作中禁用非目标存储器区块的ODT电路,则所有待机存储器区块接收和解码存储器存取命令(例如,写命令或读命令)。在这种情况下,ODT电路不进入掉电(power-down)模式,并因此增加待机功耗。相反,根据示例性实施例,非目标存储器区块的ODT电路在写操作和读操作中保持在启用状态。在这种情况下,ODT电路可更容易地进入掉电模式,并因此可降低待机功耗。

在实施例中,无论由存储器控制器输出的存储器存取命令(例如,写命令或读命令)如何,所述多个存储器区块中的非目标存储器区块的ODT电路都具有恒定电阻值。该恒定电阻值可基于存储在模式寄存器中的值。

在示例性实施例中,基于分别提供至所述多个存储器区块的多个区块选择信号来向所述多个存储器区块通知哪个存储器区块对应于用于写操作或读操作的目标存储器区块。在这种情况下,在待机状态中的所有存储器区块进入掉电模式,并且对应于激活的区块选择信号的目标存储器区块从掉电模式醒来至正常操作模式。非目标存储器区块不需要改变ODT电路的启用状态,并因此可相对于非目标存储器区块保持所述掉电模式。

这样,根据至少一个实施例的控制ODT的方法和执行该方法的系统可通过静态ODT控制来降低功耗和提高信号完整性,以使得目标存储器区块和非目标存储器区块的ODT电路基本保持在启用状态,而在读操作中禁用读目标存储器区块的ODT电路。

虽然参照图1和图2描述了针对多区块系统的控制ODT的方法,但是示例性实施例可应用于包括单个存储器区块的存储器装置的系统。

在单区块系统的情况下,所述单个存储器装置在写操作期间对应于写目标存储器区块,并且在读操作期间对应于读目标存储器区块。根据示例性实施例,当存储器装置上电时,使存储器装置的ODT电路进入初始状态以具有第一电阻值。所述ODT电路可在相对于存储器装置的写操作期间被启用,并且所述ODT电路可在相对于存储器装置的读操作期间被禁用。

图3是示出根据本发明构思的示例性实施例的多区块系统的框图。

参照图3,多区块系统10包括存储器控制器20和存储器子系统30。存储器子系统30包括多个存储器区块RNK1至RNKM,并且所述存储器区块RNK1至RNKM中的每一个包括一个或多个存储器装置MEM,M是大于1的自然数。存储器控制器20和存储器子系统30可分别包括用于互通信的接口电路。接口电路可通过用于传递命令CMD、地址ADDR和控制信号CTRL等的控制总线和用于传递数据的数据总线而连接。在实施例中,命令CMD包括地址ADDR。存储器控制器20可发出用于访问存储器子系统30的命令CMD和地址ADDR,并且可在存储器控制器20的控制下将数据写入存储器子系统30中或者可从存储器子系统30读出数据。在实施例中,存储器控制器20包括用于输出控制信号CTRL、命令CMD、地址ADDR和与存储器子系统30交换数据DATA的分别的引脚。当命令CMD包括地址ADDR时,存储器控制器20可省略用于输出地址ADDR的引脚。根据示例性实施例,当多区块系统10上电时,使所述多个存储器区块RNK1至RNKM的ODT电路进入初始状态,在相对于所述多个存储器区块RNK1至RNKM中的写目标存储器区块的写操作期间启用所述多个存储器区块RNK1至RNKM的ODT电路,并且在相对于读目标存储器区块的读操作期间禁用所述多个存储器区块RNK1至RNKM中的读目标存储器区块的ODT电路。

图4是示出包括在图3的多区块系统中的存储器装置的示例性实施例的框图。

参照图4,存储器装置400包括控制逻辑410(例如,控制逻辑电路)、地址寄存器420、分块控制逻辑430(例如,分块控制逻辑电路)、行地址多路复用器440、刷新计数器445、行解码器460、列解码器470、存储器单元阵列480、读出放大器单元485(例如,读出放大器电路)、输入-输出(I/O)门控电路490和数据输入-输出(I/O)电路500。

存储器单元阵列480包括多个分块阵列480a至480h。行解码器460包括分别耦合至分块阵列480a至480h的多个分块行解码器460a至460h。列解码器470包括分别连接至分块阵列480a至480h的多个分块列解码器470a至470h。读出放大器单元485包括分别连接至分块阵列480a至480h的多个分块读出放大器485a至485h。

地址寄存器420从存储器控制器20接收包括分块地址BANK_ADDR、行地址ROW_ADDR和列地址COL_ADDR的地址ADDR。地址寄存器420将接收到的分块地址BANK_ADDR提供至分块控制逻辑430,将接收到的行地址ROW_ADDR提供至行地址多路复用器440,并且将接收到的列地址COL_ADDR提供至列解码器470。

分块控制逻辑430可基于分块地址BANK_ADDR产生分块控制信号。可基于分块控制信号来激活分块行解码器460a至460h中的对应于分块地址BANK_ADDR的一个分块行解码器。可基于分块控制信号来激活分块列解码器470a至470h中的对应于分块地址BANK_ADDR的一个分块列解码器。

行地址多路复用器440可从地址寄存器420接收行地址ROW_ADDR,并且可从刷新计数器445接收刷新行地址REF_ADDR。行地址多路复用器440可选择性地输出行地址ROW_ADDR或刷新行地址REF_ADDR中的一个作为行地址RA。可将从行地址多路复用器440输出的行地址RA应用于分块行解码器460a至460h。

分块行解码器460a至460h中的激活的一个可解码从行地址多路复用器440输出的行地址RA,并且可激活对应于行地址RA的字线。例如,激活的分块行解码器可将字线驱动电压施加至对应于行地址RA的字线。

列解码器470可包括列地址锁存器。列地址锁存器可从地址寄存器420接收列地址COL_ADDR,并且临时存储所接收到的列地址COL_ADDR。在示例性实施例中,在触发模式中,列地址锁存器产生从接收到的列地址COL_ADDR增加的列地址。列地址锁存器可将临时存储的或产生的列地址应用于分块列解码器470a至470h。

分块列解码器470a至470h中的激活的一个可解码从列地址锁存器输出的列地址COL_ADDR,并且可以控制输入-输出门控电路490以便输出对应于列地址COL_ADDR的数据。

I/O门控电路490可包括用于对输入-输出数据进行门控的电路。I/O门控电路490还可包括用于存储从分块阵列480a至480h输出的数据的读数据锁存器,以及用于将数据写至分块阵列480a至480h的写驱动器。

将从分块阵列480a至480h的一个分块阵列读取的数据可由耦合至将从中读取数据的一个分块阵列的读出放大器485感测,并且可存储在读数据锁存器中。可经由数据I/O电路500将存储在读数据锁存器中的数据提供至存储器控制器20。可将将写入分块阵列480a至480h的一个分块阵列中的数据DQ从存储器控制器20提供至数据I/O电路500。写驱动器可将数据DQ写入分块阵列480a至480h的一个分块阵列中。

控制逻辑410可控制存储器装置400的操作。例如,控制逻辑410可产生用于存储器装置400的控制信号,以便执行写操作或读操作。控制逻辑410可包括解码从存储器控制器20接收到的命令CMD的命令解码器411和设置存储器装置的操作模式的模式寄存器组412。例如,模式寄存器组412中的寄存器的值可指示存储器装置的操作模式。

图5是示出根据本发明构思的示例性实施例的包括在图4的存储器装置中的数据输入-输出电路的实施例的框图。

参照图5,数据输入-输出电路500包括ODT电路300、数据输入-输出引脚600、传输驱动器DR 710和接收缓存器BF 720。传输驱动器710基于读数据来驱动数据输入-输出引脚600,并且接收缓存器720接收通过数据输入-输出引脚600提供的写数据。例如,将读数据从存储器区块的存储器输出至传输驱动器710,并且存储器控制器将写数据输出至接收缓存器720。在实施例中,传输驱动器DR 710和接收缓存器BF 720由运算放大器来实现。

ODT电路300包括终结器控制单元310(例如,终结器控制电路)和终结器电阻器单元350。

终结器电阻器单元350耦合至数据输入-输出引脚600,并且将终结器阻抗提供至耦合至数据输入-输出引脚600的传输线路。可将根据示例性实施例的控制ODT的方法应用于用于存储器控制器20与存储器装置30之间的双向通信的输入-输出引脚的控制终结器。因此,除数据输入-输出引脚600之外,还可将根据示例性实施例的方法应用于数据选通引脚、数据屏蔽引脚或者终结器数据选通引脚。根据示例性实施例的方法排除了地址引脚、从存储器控制器20至存储器装置30的单向通信的命令引脚的ODT。术语“引脚”宽泛地指代用于集成电路的电互连,例如,集成电路上的焊盘或其它电接触件。

在实施例中,终结器电阻器单元350执行上拉终结器操作,以在电源电压节点与数据输入-输出引脚600之间提供终结器电阻,和/或执行下拉终结器操作,以在地节点与数据输入-输出引脚600之间提供终结器电阻。下面将参照图14A和图14B来描述用于上拉终结器操作和下拉终结器操作二者的中间抽头的终结器(CTT),下面将参照图15A和图15B来描述仅用于下拉终结器操作的第一伪漏极开路(POD)终结器,并且下面将参照图16A和图16B来描述仅用于上拉终结器操作的第二POD终结器。

即使图5示出了其中配备有不同的终结器电阻器单元350的示例性实施例,传输驱动器710中的信号驱动器(未示出)本身也可用作终结器电阻器。例如,在写操作中,在启用接收缓存器720以接收写数据的同时,传输驱动器710不发送读数据,并且传输驱动器710用作终结器电阻器单元350。

当终结器电阻器单元350执行上拉终结器操作时,连接至数据输入-输出引脚600的传输线路的电压可基本保持在电源电压的电平。结果,仅当传递逻辑低电平的数据时,电流流动通过终结器电阻器单元350和传输线路。相反,当终结器电阻器单元350执行下拉终结器操作时,连接至数据输入-输出引脚600的传输线路的电压可基本保持在地电压。结果,仅当传递逻辑高电平的数据时,电流流动通过终结器电阻器单元350和传输线路。

终结器控制单元310(例如,终结器控制电路)接收强度代码SCD和输出使能信号OEN。终结器控制单元310产生用于控制终结器电阻器单元350的终结器控制信号TCS,以基于强度代码SCD和输出使能信号OEN来调整终结器阻抗。

在示例性实施例中,强度代码SCD是与数据速率关联的多个比特。数据速率是指存储器装置的操作频率或通过数据输入-输出引脚600传递的数据的翻转率。例如,当操作频率是第一频率时终结器阻抗可改变为第一阻抗,并且当操作频率是第二频率时,其改变为第二阻抗。如下面将参照图19A和图19B描述的,可基于存储在图4中的模式寄存器412中的值来提供多个比特的强度代码SCD。

在实施例中,在读操作期间激活输出使能信号OEN。在输出使能信号OEN为激活的时,终结器控制单元310提供预定逻辑电平的终结器控制信号TCS,以控制终结器电阻器单元350不提供终结器阻抗。在这种情况下,终结器电阻器单元350可响应于具有预定逻辑电平的终结器控制信号TCS,与数据输入-输出引脚600去耦合。当终结器电阻器单元350与数据输入-输出引脚600去耦合时,ODT电路300或终结器电阻器单元350可被称为“被禁用”。

在写操作期间去激活输出使能信号OEN时,终结器控制单元310产生终结器控制信号TCS,以控制终结器电阻器单元350提供终结器阻抗。终结器控制单元310可响应于强度代码SCD来改变终结器控制信号TCS的逻辑电平,以改变终结器阻抗。例如,强度代码SCD的值可指示特定终结器阻抗或电阻。如果终结器电阻器单元350先前从数据输入-输出引脚600去耦合,则终结器电阻器单元350响应于终结器控制信号TCS的施加而重新耦合至数据输入-输出引脚600。

图6是示出根据本发明构思的示例性实施例的包括在图5的数据输入-输出电路中的ODT电路的电路图。

参照图6,ODT电路300包括上拉终结器控制单元330、下拉终结器控制单元340、上拉驱动器360和下拉驱动器370。

上拉终结器控制单元330包括第一选择器334至第三选择器336(例如,多路复用器),并且下拉终结器控制单元340包括第四选择器344至第六选择器346(例如,多路复用器)。上拉驱动器360包括第一PMOS晶体管361至第三PMOS晶体管363以及第一电阻器R1至第三电阻器R3。第一PMOS晶体管361至第三PMOS晶体管363连接至电源电压VDDQ,并且第一电阻器R1至第三电阻器R3中的每一个连接在第一PMOS晶体管361至第三PMOS晶体管363中的相应的一个与数据输入-输出引脚600之间。下拉驱动器370包括第一NMOS晶体管371至第三NMOS晶体管373以及第四电阻器R4至第六电阻器R6。第一NMOS晶体管371至第三NMOS晶体管373连接至地电压VSSQ,并且第四电阻器R4至第六电阻器R6中的每一个连接在第一NMOS晶体管371至第三NMOS晶体管373中的相应的一个与数据输入-输出引脚600之间。

第一选择器334至第三选择器336中的每一个可接收电源电压VDDQ作为第一输入中的每一个,可接收第一强度代码比特至第三强度代码比特(SCD1、SCD2和SCD3)作为第二输入中的每一个,并且可接收输出使能信号OEN作为控制信号中的每一个。第四选择器344至第六选择器346中的每一个可接收地电压VSSQ作为第一输入中的每一个,可接收第四强度代码比特至第六强度代码比特(SCD4、SCD5和SCD6)作为第二输入中的每一个,并且可接收输出使能信号OEN作为控制信号中的每一个。强度代码SCD可包括强度代码比特SCD1至SCD6。

在读操作期间,在输出使能信号OEN以逻辑高电平被激活时,第一选择器334至第三选择器336可输出逻辑高电平的第一终结器控制信号至第三终结器控制信号(TCS1、TCS2和TCS3),并且第四选择器344至第六选择器346可输出逻辑低电平的第四终结器控制信号至第六终结器控制信号(TCS4、TCS5和TCS6)。第一PMOS晶体管361至第三PMOS晶体管363响应于逻辑高电平的第一终结器控制信号至第三终结器控制信号(TCS1、TCS2和TCS3)而截止,并且第一NMOS晶体管371至第三NMOS晶体管373响应于逻辑低电平的第四终结器控制信号至第六终结器控制信号(TCS4、TCS5和TCS6)而截止。因此,数据输入-输出引脚600与电源电压VDDQ和地电压VSSQ电断开连接,并且在读操作期间禁用ODT电路300。

在写操作期间,在输出使能信号OEN以逻辑低电平被去激活时,第一选择器334至第三选择器336输出第一强度代码比特至第三强度代码比特(SCD1、SCD2和SCD3)作为第一终结器控制信号至第三终结器控制信号(TCS1、TCS2和TCS3),并且第四选择器344至第六选择器346输出第四强度代码比特至第六强度代码比特(SCD4、SCD5和SCD6)作为第四终结器控制信号至第六终结器控制信号(TCS4、TCS5和TCS6)。

如上所述,强度代码SCD(也就是说,强度代码比特SCD1至SCD6)可与数据速率或操作频率关联。因此,当数据速率相对高时,通过减小终结器阻抗,沟道快速地充电/放电。当数据速率相对低时,可通过增大终结器阻抗以减小流动通过沟道的DC电流而减小电流消耗。

虽然图6中将第一电阻器R1至第六电阻器R6中的每一个示为单个电阻器,但是在示例性实施例中,第一电阻器R1至第六电阻器R6中的每一个可利用多个电阻器来实现,所述多个电阻器与用于控制所述多个电阻器的连接的多个晶体管并联和/或串联。

图6示出了图14A和图14B的CTT方案的示例性实施例,并且可从中理解POD终结器方案。省略了图6中的上拉终结器控制单元330和上拉驱动器360的构造对应于图15A和图15B的第一POD终结器,并且省略了图6中的下拉终结器控制单元340和下拉驱动器370的构造对应于图16A和图16B的第二POD终结器。

图7、图8A和图8B是示出根据本发明构思的示例性实施例的在写操作中控制ODT的方法的示图。

如图7所示,存储器控制器MC通过数据输入-输出引脚PADC和PAD1至PADM以及传输线路TL并行地连接至所述多个存储器区块RNK1至RNKM。传输线路TL在公共节点NC处分支至存储器区块RNK1至RNKM的数据输入-输出引脚PAD1至PADM。

图7示出了其中第一存储器区块RNK1对应于写目标存储器区块,并且其它存储器区块RNK2至RNKM对应于非目标存储器区块的示例性情况。在图7中,启用的元件用阴影线标记。在写操作中,在对应于数据发送器装置的存储器控制器MC中启用传输驱动器DR0并且禁用接收缓存器BF0。另外,在对应于数据接收器装置的写目标存储器区块RNK1中启用接收缓存器BF1,而写目标存储器区块RNK1中的传输驱动器DR1、非目标存储器区块RNK2至RNKM中的接收缓存器BF2至BFM和传输驱动器DR2至DRM被禁用。

根据示例性实施例,在写操作期间,写目标存储器区块RNK1中的ODT电路TER1和非目标存储器区块RNK2至RNKM中的ODT电路TER2至TERM全被启用。存储器控制器MC中的ODT电路TER0被禁用。可从存储器控制器MC中的传输驱动器DR0到存储器区块RNK1至RNKM中的所有ODT电路TER1至TERM形成电流路径,并因此可减小信号反射并且可提高信号完整性。

在图8A和图8B中,时间点Ta0至Tf1对应于操作时钟信号对CK_T和CK_C的边缘。第一区块选择信号CS_RNK1和第一命令信号CMD_RNK1专用于第一存储器区块RNK1,并且第二区块选择信号CS_RNK2和第二命令信号CMD_RNK2专用于第二存储器区块RNK2。将数据选通信号对WCK_T和WCK_C和数据信号DQ[15:0]从存储器控制器MC提供至写目标存储器区块RNK1。ODT_RNK1表示第一存储器区块RNK1的ODT状态,并且ODT_RNK2表示第二存储器区块RNK2的ODT状态。DES表示“取消选择”,并且TRANSITION表示当ODT状态改变时的转变间隔。

图8A和图8B示出了当第一存储器区块RNK1对应于写目标存储器区块并且第二存储器区块RNK2对应于非目标存储器区块时的写操作的示例情况。在激活第一区块选择信号CS_RNK1的同时,CAS命令和写命令WR通过第一命令信号CMD_RNK1传递,并且第二区块选择信号CS_RNK2和第二命令信号CMD_RNK2保持去激活状态。

根据示例性实施例,在写操作期间,写目标存储器区块RNK1中的ODT电路和非目标存储器区块RNK2中的ODT电路被启用。在示例性实施例中,如图8A所示,在用于写操作的数据信号DQ[15:0]切换的同时,写目标存储器区块RNK1和非目标存储器区块RNK2中的ODT电路保持初始状态NT-ODT。在示例性实施例中,如图8B所示,在用于写操作的数据信号DQ[15:0]切换的同时,非目标存储器区块RNK2中的ODT电路保持初始状态NT-ODT,并且写目标存储器区块RNK1中的ODT电路改变为具有不同于初始状态NT-ODT的电阻值的电阻值的状态TG-ODT。虽然上面描述了16比特数据的数据信号,但是本发明构思不限于此,这是因为在替代性实施例中,数据的大小可小于16比特或者大于16比特。

图9和图10是示出根据本发明构思的示例性实施例的在读操作中控制ODT的方法的示图。

如图9所示,存储器控制器MC通过数据输入-输出引脚PADC和PAD1至PADM以及传输线路TL并行地连接至所述多个存储器区块RNK1至RNKM。传输线路TL在公共节点NC处分支到存储器区块RNK1至RNKM的数据输入-输出引脚PAD1至PADM。

图9示出了其中第一存储器区块RNK1对应于读目标存储器区块并且其它存储器区块RNK2至RNKM对应于非目标存储器区块的示例性情况。在图9中,用阴影线标记启用的元件。在读操作中,在对应于数据接收器装置的存储器控制器MC中,接收缓存器BF0被启用,并且传输驱动器DR0被禁用。另外,在对应于数据发送器装置的读目标存储器区块RNK1中启用传输驱动器DR1,而读目标存储器区块RNK1中的接收缓存器BF1、非目标存储器区块RNK2至RNKM中的接收缓存器BF2至BFM和传输驱动器DR2至DRM被禁用。

根据示例性实施例,在读操作期间,写目标存储器区块RNK1中的ODT电路TER1被禁用,并且非目标存储器区块RNK2至RNKM中的ODT电路TER2至TERM被启用。存储器控制器MC中的ODT电路TER0被启用。可从读目标存储器区块RNK1中的传输驱动器DR1到存储器控制器MC中的ODT电路TER0和非目标存储器区块RNK2至RNKM中的ODT电路TER2至TERM形成电流路径,并因此可减少信号反射并且可提高信号完整性。

在图10中,时间点Ta0至Tf1对应于操作时钟信号对CK_T和CK_C的边缘。第一区块选择信号CS_RNK1和第一命令信号CMD_RNK1专用于第一存储器区块RNK1,并且第二区块选择信号CS_RNK2和第二命令信号CMD_RNK2专用于第二存储器区块RNK2。将数据选通信号对WCK_T和WCK_C和数据信号DQ[15:0]从读目标存储器区块RNK1提供至存储器控制器MC。ODT_RNK1表示第一存储器区块RNK1的ODT状态,并且ODT_RNK2表示第二存储器区块RNK2的ODT状态。DES表示“取消选择”,并且TRANSITION表示当ODT状态改变时的转变间隔。

图10示出了当第一存储器区块RNK1对应于读目标存储器区块并且第二存储器区块RNK2对应于非目标存储器区块时的读操作的示例情况。在激活第一区块选择信号CS_RNK1时,CAS命令和读命令RD通过第一命令信号CMD_RNK1传递,并且第二区块选择信号CS_RNK2和第二命令信号CMD_RNK2保持去激活状态。

根据示例性实施例,在读操作期间,读目标存储器区块RNK1中的ODT电路被禁用,并且非目标存储器区块RNK2中的ODT电路被启用。在示例性实施例中,如图10所示,在用于读操作的数据信号DQ[15:0]被切换时,非目标存储器区块RNK2中的ODT电路保持初始状态NT-ODT,并且读目标存储器区块RNK1中的ODT电路改变为禁用状态NT-ODT OFF。

图11是示出根据本发明构思的示例性实施例的应用于控制ODT的方法的电阻设置的实施例的示图。

参照图11,在读操作期间,目标存储器区块RNK_TG中的ODT电路被禁用,并且非目标存储器区块RNK_NT和存储器控制器MC中的ODT电路具有第一电阻值M*Rtt。在写操作期间,目标存储器区块RNK_TG和非目标存储器区块RNK_NT中的ODT电路具有第一电阻值M*Rtt,并且存储器控制器MC中的ODT电路被禁用。第一电阻值M*Rtt可对应于上述初始状态的电阻值。因此,如参照图8A所描述的,目标存储器区块RNK_TG和非目标存储器区块RNK_NT中的ODT电路可保持初始状态,以在写操作期间具有第一电阻值M*Rtt。

图12是用于描述对应于图11的电阻设置的、写操作中的ODT电路的等效电阻的示图。

参照图12,在数据被从存储器控制器MC传递至目标存储器区块RNK1的写操作中,目标存储器区块RNK1和非目标存储器区块RNK2至RNKM中的所有ODT电路具有第一电阻值M*Rtt。当所述多个存储器区块RNK1至RNKM的数量为M时,具有第一电阻值M*Rtt的M个电阻器在公共节点NC与电源电压VDDQ之间并联,并且公共节点NC与电源电压VDDQ之间的等效电阻值对应于Rtt。以相同的方式,公共节点NC与地电压VSSQ之间的等效电阻值对应于Rtt。下面将参照图14A至图16B来描述对应于等效电阻值Rtt的各个终结器方案。

图13是用于描述对应于图11的电阻设置的、读操作中的ODT电路的等效电阻的示图。

参照图13,在数据被从目标存储器区块RNK1传递至存储器控制器MC的读操作期间,目标存储器区块RNK1中的ODT电路被禁用,并且非目标存储器区块RNK2至RNKM和存储器控制器MC中的ODT电路具有第一电阻值M*Rtt。当所述多个存储器区块RNK1至RNKM的数量为M时,具有第一电阻值M*Rtt的M个电阻器在公共节点NC与电源电压VDDQ之间并联,并且公共节点NC与电源电压VDDQ之间的等效电阻值对应于Rtt。以相同的方式,公共节点NC与地电压VSSQ之间的等效电阻值对应于Rtt。下面将参照图14A至图16B来描述对应于等效电阻值Rtt的各个终结器方案。图14A至图16B的构造是用于描述几个可能的终结器方案的示例性实施例,但是传输驱动器和ODT电路的构造不限于此。例如,可交换N型和P型晶体管和/或可将用于功率门控的晶体管加至传输驱动器。

图14A和图14B是用于描述中间抽头的终结器(CTT)的示图。

参照图14A,发送器装置中的传输驱动器70基于来自发送器装置的内部信号的传输信号ST来驱动输入-输出焊盘PADH。发送器装置的输入-输出焊盘PADH通过传输线路TL连接至接收器装置的输入-输出焊盘PADS。为了阻抗匹配,CTT方案的终结器电路80连接至接收器装置的输入-输出焊盘PADS。接收器装置中的接收缓存器BF可将通过输入-输出焊盘PADS的输入信号SI与参考电压VREF进行比较,以将缓存信号SB提供至接收器装置的内部电路。

传输驱动器70可包括连接在第一电源电压VDDQ与输入-输出焊盘PADH之间的上拉单元和连接在输入-输出焊盘PADH与低于第一电源电压VDDQ的第二电源电压VSSQ之间的下拉单元。上拉单元可包括导通电阻器RON和响应于传输信号ST而开关的p沟道金属氧化物半导体(PMOS)晶体管TP1。下拉单元可包括导通电阻器RON和响应于传输信号ST而开关的n沟道金属氧化物半导体(NMOS)晶体管TN1。可省略导通电阻器RON,并且各个导通电阻器RON可表示当晶体管TP1和TN1中的每一个被导通时电压节点与输入-输出焊盘PADH之间的电阻。

CTT方案的终结器电路80可包括连接在第一电源电压VDDQ与输入-输出焊盘PADS之间的第一子终结器电路和连接在输入-输出焊盘PADS与第二电源电压VSSQ之间的第二子终结器电路。第一子终结器电路可包括终结器电阻器Rtt和响应于低电压被导通的PMOS晶体管TP2。第二子终结器电路可包括终结器电阻器Rtt和响应于高电压被导通的NMOS晶体管TN2。可省略终结器电阻器Rtt,并且各个终结器电阻器Rtt可表示当晶体管TP2和TN2中的每一个被导通时电压节点与输入-输出焊盘PADS之间的电阻。

就图14A中的CTT方案的终结器电路80而言,输入信号SI的高电压电平VIH和低电压电平VIL可如图14B所表示。可假设第二电源电压VSSQ为地电压(即,VSSQ=0),并且沿着传输线路TL的电压降可忽略。因此,可根据表达式1来计算高电压电平VIH、低电压电平VIL和优选参考电压VREF。

VIH=VDDQ*(RON+Rtt)/(2RON+Rtt),

VIL=VDDQ*RON/(2RON+Rtt),

VREF=(VIH+VIL)/2=VDDQ/2

图15A和图15B是用于描述第一伪漏极开路(POD)终结器的示图。

参照图15A,发送器装置中的传输驱动器70基于来自发送器装置的内部信号的传输信号ST来驱动输入-输出焊盘PADH。发送器装置的输入-输出焊盘PADH通过传输线路TL连接至接收器装置的输入-输出焊盘PADS。为了阻抗匹配,第一POD终结器方案的终结器电路81可连接至接收器装置的输入-输出焊盘PADS。接收器装置中的接收缓存器BF可将通过输入-输出焊盘PADS的输入信号SI与参考电压VREF进行比较,以将缓存信号SB提供至接收器装置的内部电路。

传输驱动器70可包括连接在第一电源电压VDDQ与输入-输出焊盘PADH之间的上拉单元以及连接在输入-输出焊盘PADH与低于第一电源电压VDDQ的第二电源电压VSSQ之间的下拉单元。上拉单元可包括导通电阻器RON和响应于传输信号ST而开关的PMOS晶体管TP1。下拉单元可包括导通电阻器RON和响应于传输信号ST而开关的NMOS晶体管TN1。可省略导通电阻器RON,并且各个导通电阻器RON可表示当晶体管TP1和TN1中的每一个被导通时电压节点与输入-输出焊盘PADH之间的电阻。

第一POD终结器方案的终结器电路81可包括终结器电阻器Rtt和响应于高电压而被导通的NMOS晶体管TN2。可省略终结器电阻器Rtt并且终结器电阻器Rtt可表示当NMOS晶体管TN2被导通时电压节点与输入-输出焊盘PADS之间的电阻。

就图15A中的第一POD终结器方案的终结器电路81而言,输入信号SI的高电压电平VIH和低电压电平VIL可如图15B所表示。可假设第二电源电压VSSQ为地电压(即,VSSQ=0),并且沿着传输线路TL的电压降可忽略。因此,可根据表达式2来计算高电压电平VIH、低电压电平VIL和最佳参考电压VREF。

VIH=VDDQ*RTT/(RON+RTT),

VIL=VSSQ=0,

VREF=(VIH+VIL)/2=VDDQ*RTT/2(RON+RTT)

图16A和图16B是用于描述第二POD终结器的示图。

参照图16A,发送器装置中的传输驱动器70基于来自发送器装置的内部信号的传输信号ST来驱动输入-输出焊盘PADH。发送器装置的输入-输出焊盘PADH通过传输线路TL连接至接收器装置的输入-输出焊盘PADS。为了阻抗匹配,第二POD终结器方案的终结器电路82连接至接收器装置的输入-输出焊盘PADS。接收器装置中的接收缓存器BF可将通过输入-输出焊盘PADS的输入信号SI与参考电压VREF进行比较,以将缓存信号SB提供至接收器装置的内部电路。

传输驱动器70可包括连接在第一电源电压VDDQ与输入-输出焊盘PADH之间的上拉单元以及连接在输入-输出焊盘PADH与低于第一电源电压VDDQ的第二电源电压VSSQ之间的下拉单元。上拉单元可包括导通电阻器RON和响应于传输信号ST而开关的PMOS晶体管TP1。下拉单元可包括导通电阻器RON和响应于传输信号ST而开关的NMOS晶体管TN1。可省略导通电阻器RON,并且各个导通电阻器RON可表示当晶体管TP1和TN1中的每一个被导通时电压节点与输入-输出焊盘PADH之间的电阻。

第二POD终结器方案的终结器电路82可包括终结器电阻器Rtt和响应于低电压而被导通的PMOS晶体管TP2。可省略终结器电阻器Rtt,并且终结器电阻器Rtt可表示当NMOS晶体管TN2被导通时电压节点与输入-输出焊盘PADS之间的电阻。

就图16A中的第一POD终结器方案的终结器电路82而言,输入信号SI的高电压电平VIH和低电压电平VIL可如图16B所表示。可假设第二电源电压VSSQ为地电压(即,VSSQ=0),并且沿着传输线路TL的电压降可忽略。因此,可根据表达式3来计算高电压电平VIH、低电压电平VIL和最佳参考电压VREF。

VIH=VDDQ,

VIL=VDDQ*RON/(RON+Rtt),

VREF=(VIH+VIL)/2=VDDQ*(2RON+Rtt)/2(RON+Rtt)

这样,根据至少一个示例性实施例的ODT电路可采用各种终结器方案。在示例性实施例中,根据表达式1、表达式2和表达式3执行训练处理以获得优选参考电压VREF。在示例性实施例中,存储器控制器考虑非目标存储器区块的ODT电阻器,其被连续启用以调整存储器控制器中的ODT电路的电阻值或存储器控制器中的传输驱动器的导通电阻值。

图17是示出根据本发明构思的示例性实施例的应用于控制ODT的方法的电阻设置的实施例的示图。

参照图17,在读操作期间,目标存储器区块RNK_TG中的ODT电路被禁用,并且非目标存储器区块RNK_NT和存储器控制器MC中的ODT电路具有第一电阻值M*Rtt。在写操作期间,目标存储器区块RNK_TG中的ODT电路具有与第一电阻值M*Rtt不同的第二电阻值M*Rtt+Rtg,非目标存储器区块RNK_NT中的ODT电路具有第一电阻值M*Rtt,并且存储器控制器MC中的ODT电路被禁用。第一电阻值M*Rtt可对应于上述初始状态的电阻值。例如,第一电阻值M*Rtt可为约70Ω,并且第二电阻值M*Rtt+Rtg可为约150Ω。因此,如参照图8B所描述的,目标存储器区块RNK_TG中的ODT电路的电阻值可从第一电阻值M*Rtt改变为第二电阻值M*Rtt+Rtg,并且非目标存储器区块RNK_NT中的ODT电路可在写操作期间保持初始状态,以具有第一电阻值M*Rtt。在实施例中,第二电阻值大于第一电阻值,在读操作期间,目标存储器区块RNK_TG的ODT电路被禁用并且非目标存储器区块RNK_NT的ODT电路被启用并被设为第一电阻值,以及在写操作期间,目标存储器区块的ODT电路被启用并被设为第二电阻值。

图18是示出根据示例性实施例的CAS命令的示图。

图18示出了符合低功率双数据速率5(LPDDR5)标准的示例性CAS命令。参照图18,CAS命令可表示为命令-地址信号CA0至CA6的组合。“L”表示逻辑低电平,“H”表示逻辑高电平,EDC_EN、WS_WR、WS_RD、WS_FAST、DC0-DC3、NT0、NT1和BL表示形成CAS命令的域值。具体地说,NT0和NT1表示用于终结器控制的字段值。

如图18所示,当采用根据示例性实施例的静态ODT控制时,可省略NT0和NT1,并且可保留对应的部分以备将来使用(RFU)。

图19A和图19B是用于描述根据示例性实施例的用于ODT的模式寄存器的示图。

用于ODT控制的信息可存储在图4中的模式寄存器412中。例如,模式寄存器412的对应的部分可具有如图19A和图19B所示的模式寄存器设置MRSET。运算对象OP0至OP7的一些值可表示关于ODT电路的电阻值的信息。

图19A示出了用于共同地控制目标存储器区块和非目标存储器区块中的ODT电路的电阻值的值ODT,如参照图8A所描述的。图19B示出了用于控制目标存储器区块中的ODT电路的第一电阻值的第一值TG-ODT和用于控制非目标存储器区块中的ODT电路的第二电阻值的第二值NT-ODT,如参照图8B所描述的。可通过模式寄存器写操作将存储在模式寄存器412中的值ODT、TG-ODT和NT-ODT从存储器控制器提供至存储器区块。可基于值ODT、TG-ODT和NT-ODT来提供上述强度代码SCD。

图20是示出根据本发明构思的示例性实施例的半导体存储器装置的结构图。

参照图20,半导体存储器装置900包括第一半导体集成电路层LA1至第k半导体集成电路层LAk,其中,假设最下面的第一半导体集成电路层LA1为接口或控制芯片,并且假设其它半导体集成电路层LA2至LAk为包括核存储器芯片的从芯片。从芯片可形成上述多个存储器区块。

第一半导体集成电路层LA1至第k半导体集成电路层LAk可通过穿通衬底的过孔TSV(例如,硅通孔)在层之间发送和接收信号。作为接口或控制芯片的最下面的第一半导体集成电路层LA1可通过形成在外部表面上的导电结构与外部存储器控制器通信。

第一半导体集成电路层910至第k半导体集成电路层920中的每一个可包括存储器区921和用于驱动存储器区921的外围电路922。例如,外围电路922可包括用于驱动存储器的字线的行驱动器、用于驱动存储器的位线的列驱动器、用于控制数据的输入-输出的数据输入-输出电路、用于从外部源接收命令和缓存所述命令的命令缓存器、以及用于从外部源接收地址和缓存所述地址的地址缓存器。

第一半导体集成电路层910还可包括控制电路。控制电路可基于来自存储器控制器的命令和地址信号来控制对存储器区921的访问,并且可产生用于访问存储器区921的控制信号。

图21是示出根据本发明构思的示例性实施例的移动系统的框图。

参照图21,移动系统1200包括应用处理器1210、连接电路1220、易失性存储器装置(VM)1230、非易失性存储器装置(NVM)1240、用户接口1250和电源1260。

应用处理器1210可执行存储在包括诸如网络浏览器、游戏应用、视频播放器等的应用的计算机可读介质(例如,存储器装置)中的计算机指令。连接电路1220可与外部装置执行有线或无线通信。易失性存储器装置1230可存储由应用处理器1210处理的数据,或者可作为工作存储器来操作。例如,易失性存储器装置1230可为动态随机存取存储器,诸如双数据速率同步动态随机存取存储器(DDR SDRAM)、低功率双数据速率同步动态随机存取存储器(LPDDR SDRAM)、图形双数据速率同步动态随机存取存储器(GDDR SDRAM)、Rambus动态随机存取存储器(RDRAM)等。非易失性存储器装置1240可存储用于引导(booting)移动系统1200的引导图像。用户接口1250可包括诸如小键盘、触摸屏等的至少一个输入装置,以及诸如扬声器、显示装置等的至少一个输出装置。电源1260可将电源电压供应至移动系统1200。在示例性实施例中,移动系统1200还包括相机图像处理器(CIS)和/或诸如存储卡、固态驱动(SSD)、硬盘驱动(HDD)、CD-ROM等的存储装置。

易失性存储器装置1230和/或非易失性存储器装置1240可具有用于执行如参照图1至图19B描述的根据示例性实施例的控制ODT的方法的构造。

如上所述,控制ODT的方法和执行根据示例性实施例的方法的系统可通过静态ODT控制来降低功耗和提高信号完整性,以使得目标存储器区块和非目标存储器区块的ODT电路基本保持在启用状态,而在读操作期间所述读目标存储器区块的ODT电路被禁用。

可将本发明构思的实施例应用于各种装置和包括存储器装置的系统。例如,可将本发明构思应用于诸如存储卡、移动电话、智能电话、个人数字助理(PDA)、便携式多媒体播放器(PMP)、数码相机、摄像机、个人计算机(PC)、服务器计算机、工作站、笔记本计算机、数字TV、机顶盒、便携式游戏机、导航系统等的系统。

上面示出了本发明构思的示例性实施例,并且不应被理解为是其限制。虽然已描述了几个示例性实施例,但是本领域技术人员应该理解,在不实质脱离本发明构思的情况下,在示例性实施例中许多修改是可能的。

- 控制片内终结器的方法和执行该方法的系统

- 控制片内终结器的方法和执行该方法的系统