像素阵列

文献发布时间:2023-06-19 11:26:00

技术领域

本发明涉及一种像素阵列,且特别涉及一种具有横向图案的像素阵列。

背景技术

随着科技的进步,大尺寸面板多朝向窄边框设计的形态发展。目前多采用TGP(Tracking Gate-line in Pixel)窄边框技术,使在水平方向上延伸的栅极线通过在垂直方向上延伸的转接元件电性连接至栅极驱动电路,以进一步减少面板边框的宽度。

然而,当转接元件设置于主动区时,转接元件势必会与数据线相邻,易发生与相邻数据线耦合或产生栅极/漏极电容(gate-drain capacitance,Cgd)等问题,往往影响信号传递的品质,而导致最终呈现的功能不符预期。举例来说,转接元件与数据线之间的耦合作用容易使像素的电压高于规定值,而于显示画面中呈现出一斜线的亮点,影响使用者观赏体验。因此如何解决上述问题,已成为目前研发人员所关注的议题。

发明内容

本发明提供一种像素阵列,其设计可有助于实现窄边框设计的需求,且可降低线路之间的耦合进而改善像素阵列的品质。

本发明的至少一实施例提供一种像素阵列,包括基板、多条横向信号线、多条第一纵向信号线、多条第二纵向信号线以及多个像素结构。基板具有主动区及位于主动区外的周边区。横向信号线配置于主动区。第一纵向信号线自周边区延伸进主动区,且与横向信号线相交。第二纵向信号线与多条横向信号线的其中一者电性连接,且相邻于至少一条第一纵向信号线,多条第二纵向信号线的其中一者包含横向图案,其中横向图案相邻于多条横向信号线的另一者。像素结构配置于主动区,且与横向信号线及第一纵向信号线电性连接,多个像素结构的其中一者被相邻两条横向信号线以及相邻两条第一纵向信号线围绕。

在本发明的一实施例中,上述横向图案的长度大于或等于多个像素结构的其中一者的横向宽度。

在本发明的一实施例中,上述多条第二纵向信号线的至少一者包含横向图案,且多条第二纵向信号线的至少一者不包含横向图案。

在本发明的一实施例中,每一上述多条第二纵向信号线包含横向图案。

在本发明的一实施例中,上述包含横向图案的第二纵向信号线还包含第一纵向图案及第二纵向图案,其中第一纵向图案及第二纵向图案分别邻接于横向图案的两端,且分别相邻于两条第一纵向信号线。并且,第一纵向图案、横向图案以及第二纵向图案按序电性连接。

在本发明的一实施例中,上述第一纵向图案与第二纵向图案位于相同膜层中,且横向图案所在的膜层不同于第一纵向图案与第二纵向图案所在的膜层。

在本发明的一实施例中,上述像素阵列还包括第一转接结构及第二转接结构,其中第一转接结构配置于主动区,且在像素阵列的俯视图中,第一转接结构设置于第一纵向图案与横向图案的相交处;第二转接结构配置于主动区,且在像素阵列的俯视图中,第二转接结构设置于第二纵向图案与横向图案的相交处。并且,第一纵向图案通过第一转接结构连接横向图案,横向图案通过第二转接结构连接第二纵向图案。

在本发明的一实施例中,上述第一纵向图案的沿纵向方向上的长度大于或等于a个像素结构,上述第二纵向图案的沿纵向方向上的长度大于或等于b个像素结构,其中a、b为正整数。

在本发明的一实施例中,上述b为1。

在本发明的一实施例中,上述像素阵列还包括多个栅极驱动垫,其中多个栅极驱动垫横向按序排列于周边区,且每一栅极驱动垫分别电性连接对应的第二纵向信号线。

在本发明的一实施例中,上述像素阵列还包括定电压线,其中定电压线配置于周边区,且具有主线段及支线段。主线段与横向信号线平行,支线段自主线段沿多条第一纵向信号线的其中一者延伸,且跨越c个像素结构,其中c为正整数。在像素阵列的俯视图中,支线段相对于主线段的一端与第二纵向信号线及横向信号线的电性连接处相隔一距离,所述距离小于多个像素结构的其中一者的纵向长度。

在本发明的一实施例中,上述距离为3μm~5μm。

在本发明的一实施例中,上述像素阵列还包括绝缘层,其中绝缘层覆盖第一纵向信号线与第二纵向信号线,且具有沟槽。沟槽沿着第一纵向信号线与第二纵向信号线延伸,且沟槽在基板的投影位于第一纵向信号线在基板的投影与第二纵向信号线在基板的投影之间。

基于上述,本发明通过其中一条第二纵向信号线包含横向图案,能够将第二纵向信号线在纵向方向适度地分段,可降低第二纵向信号线对相邻第一纵向信号线传递信号时所产生的耦合现象,有助于在实现窄边框设计需求的同时,还可降低线路之间的耦合进而改善像素阵列的品质。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合说明书附图作详细说明如下。

附图说明

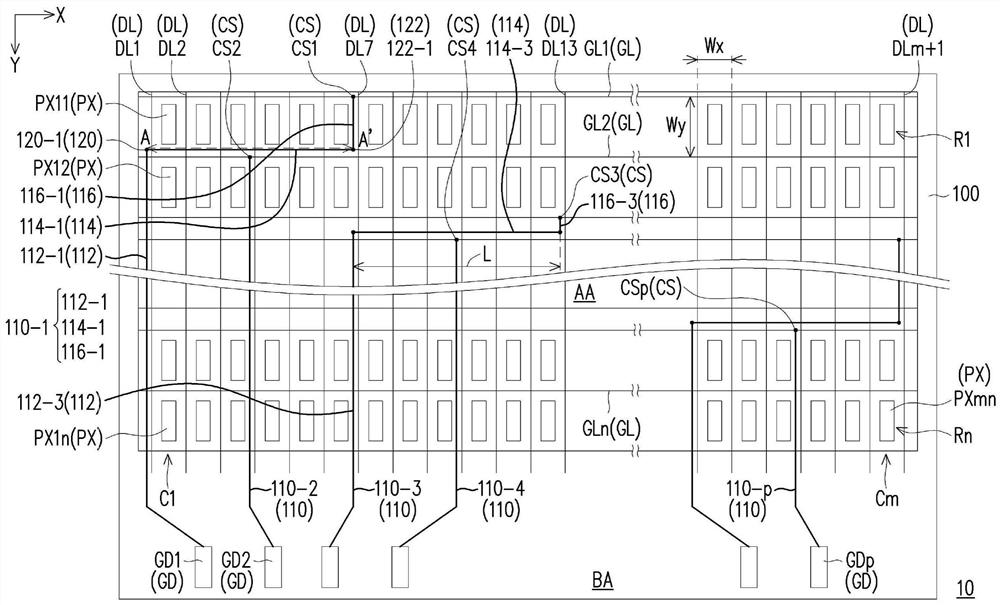

图1A是依照本发明的第一实施例的一种像素阵列的俯视示意图。

图1B是图1A的像素阵列中沿剖线A-A’的剖面示意图。

图2是依照本发明的第二实施例的一种像素阵列的俯视示意图。

图3A是依照本发明的第三实施例的一种像素阵列的俯视示意图。

图3B是图3A的像素阵列中沿剖线A-A’的剖面示意图。

图4是依照本发明的第三实施例的另一种像素阵列的俯视示意图。

图5是依照本发明的第四实施例的一种像素阵列的局部俯视示意图。

附图标记说明:

10、20、30A、30B、40:像素阵列

100:基板

110、110-1~110-4、110-p、310、310-1~310-3:第二纵向信号线

112、112-1、112-3、312、312-1:第一纵向图案

114、114-1、114-3、314、314-1:横向图案

116、116-1、116-3、316、316-1:第二纵向图案

120、120-1:第一转接结构

122、122-1:第二转接结构

200:定电压线

202:主线段

204:支线段

AA:主动区

BA:周边区

C1、Cm:像素行

CS、CS1~CS4、CSp:导通结构

D1~D4:长度

DL、DL1、DL2、DL7、DL13、DLm+1:第一纵向信号线

GD、GD1、GD2、GDp:栅极驱动垫

GL、GL1、GL2、GLn:横向信号线

I1:第一绝缘层

I2:第二绝缘层

L、La、Lb:长度

M1:第一导体层

M2:第二导体层

PX、PX11、PX12、PX1n、PXmn:像素结构

R1、Rn:像素列

TR:沟槽

V1:第一通孔

V2:第二通孔

Vgl:低电平电压

Vgh:高电平电压

Wx:横向宽度

Wy:纵向长度

X:横向方向

Y:纵向方向

具体实施方式

在附图中,为了清楚起见,放大了层、膜、面板、区域等的厚度。在整个说明书中,相同的附图标记表示相同的元件。应当理解,当诸如层、膜、区域或基板的元件被称为在“另一元件上”、或“连接到另一元件”、“重叠于另一元件”时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反,当元件被称为“直接在另一元件上”或“直接连接到”另一元件时,不存在中间元件。如本文所使用的,“连接”可以指物理及/或电性连接。再者,“电性连接”或“耦合”是可为二元件间存在其它元件。

应当理解,尽管术语“第一”、“第二”、“第三”等在本文中可以用于描述各种元件、部件、区域、层及/或部分,但是这些元件、部件、区域、及/或部分不应受这些术语的限制。这些术语仅用于将一个元件、部件、区域、层或部分与另一个元件、部件、区域、层或部分区分开。因此,下面讨论的“第一元件”、“部件”、“区域”、“层”、或“部分”可以被称为第二元件、部件、区域、层或部分而不脱离本文的教导。

这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所使用的,除非内容清楚地指示,否则单数形式“一”、“一个”和“该”旨在包括多个形式,包括“至少一个”。“或”表示“及/或”。如本文所使用的,术语“及/或”包括一个或多个相关所列项目的任何和所有组合。还应当理解,当在本说明书中使用时,术语“包括”及/或“包括”指定所述特征、区域、整体、步骤、操作、元件的存在及/或部件,但不排除一个或多个其它特征、区域整体、步骤、操作、元件、部件及/或其组合的存在或添加。

此外,诸如“下”或“底部”和“上”或“顶部”的相对术语可在本文中用于描述一个元件与另一元件的关系,如图所示。应当理解,相对术语旨在包括除了图中所示的方位之外的装置的不同方位。例如,如果一个附图中的装置翻转,则被描述为在其他元件的“下”侧的元件将被定向在其他元件的“上”侧。因此,示例性术语“下”可以包括“下”和“上”的取向,取决于附图的特定取向。类似地,如果一个附图中的装置翻转,则被描述为在其它元件“下方”或“下方”的元件将被定向为在其它元件“上方”。因此,示例性术语“下面”或“上面”可以包括上方和下方的取向。

本文使用的“约”、或“大致上”包括所述值和在本领域普通技术人员确定的特定值的可接受的偏差范围内的平均值,考虑到所讨论的测量和与测量相关的误差的特定数量(即,测量系统的限制)。例如,“约”可以表示在所述值的一个或多个标准偏差内,或±30%、±20%、±10%、±5%内。再者,本文使用的“约”、或“大致上”可依光学性质、蚀刻性质或其它性质,来选择较可接受的偏差范围或标准偏差,而可不用一个标准偏差适用全部性质。

除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

本文参考作为理想化实施例的示意图的截面图来描述示例性实施例。因此,可以预期到作为例如制造技术及/或公差的结果的图示的形状变化。因此,本文所述的实施例不应被解释为限于如本文所示的区域的特定形状,而是包括例如由制造导致的形状偏差。例如,示出或描述为平坦的区域通常可以具有粗糙及/或非线性特征。此外,所示的锐角可以是圆的。因此,图中所示的区域本质上是示意性的,并且它们的形状不是旨在示出区域的精确形状,并且不是旨在限制权利要求的范围。

图1A是依照本发明的第一实施例的一种像素阵列的俯视示意图;图1B是图1A的像素阵列中沿剖线A-A’的剖面示意图。为方便说明,图1A中省略示出绝缘层的位置及部分像素结构PX。

请同时参照图1A及图1B,像素阵列10包括基板100、多条横向信号线GL、多条第一纵向信号线DL、多条第二纵向信号线110以及多个像素结构PX。基板100可具有主动区AA以及位于主动区AA外的周边区BA。在本实施例中,基板100的材料可包括玻璃或其他适宜的材料等,但本发明不以此为限。

横向信号线GL配置于基板100的主动区AA上,且沿着横向方向X延伸。在本实施例中,多条横向信号线GL可包括横向信号线GL1、横向信号线GL2、…、横向信号线GLn,其中n为正整数。横向信号线GL1、横向信号线GL2、…、横向信号线GLn例如按序沿纵向方向Y排列,如图1A所示,横向信号线GL1、横向信号线GL2、…、横向信号线GLn例如是由基板100的上侧至基板100的下侧按序排列于基板100上。横向方向X与纵向方向Y交错。举例而言,在本实施例中,横向方向X与纵向方向Y可垂直,但本发明不以此为限。以下实施例描述的横向与纵向可分别视为图1A中的横向方向X与纵向方向Y。在本实施例中,横向信号线GL可为栅极线。

第一纵向信号线DL配置于基板100上,并自周边区BA延伸进主动区AA,且与多条横向信号线GL相交。在本实施例中,多条第一纵向信号线DL可包括第一纵向信号线DL1、第一纵向信号线DL2、…、第一纵向信号线DLm+1,其中m为正整数。第一纵向信号线DL1、第一纵向信号线DL2、…、第一纵向信号线DLm+1例如按序沿横向方向X排列,如图1A所示,第一纵向信号线DL1、第一纵向信号线DL2、…、第一纵向信号线DLm+1例如是由基板100的左侧至基板100的右侧按序排列于基板100上。在本实施例中,第一纵向信号线DL可为数据线。

第二纵向信号线110配置于基板100上。在本实施例中,在横向方向X上,第二纵向信号线110与至少一条第一纵向信号线DL相邻。在本实施例中,第二纵向信号线110的延伸方向大体上可平行于第一纵向信号线DL。举例来说,第二纵向信号线110与第一纵向信号线DL可以是相互平行的线型图案,也可以具有相互平行的曲折图案,但本发明不以此为限。在本实施例中,第二纵向信号线110可作为栅极转接线,而与其中一条横向信号线GL电性连接。另外,为了避免横向信号线GL与第二纵向信号线110之间的短路,横向信号线GL与第二纵向信号线110可由不同膜层构成,且横向信号线GL与第二纵向信号线110之间可夹有一或多层绝缘层。在一些实施例中,第一纵向信号线DL及第二纵向信号线110可位于相同的膜层,且横向信号线GL可位于与第一纵向信号线DL及第二纵向信号线110不同的膜层中。在一些实施例中,第二纵向信号线110可包括通过对应的导通结构CS连接于对应的该横向信号线GL。在一些实施例中,其中一条第二纵向信号线110包含横向图案114,其中横向图案114相邻于未与所述第二纵向信号线110电性连接的另一条横向信号线GL,但本发明不以此为限。举例来说,如图1A所示,图1A中最左侧的第二纵向信号线110-1可通过位于最上列但非位于自左方起算第一行的导通结构CS1而电性连接至最上列的横向信号线GL1。更具体而言,位于第一行的第二纵向信号线110-1是于相邻于横向信号线GL2处通过长度至少横跨六个像素结构PX的横向宽度Wx的横向图案114-1以及相邻于第一纵向信号线DL7且长度至少跨越一个像素结构PX的纵向长度Wy的第二纵向图案116而与横向信号线GL1连接。

多个像素结构PX以阵列排列的方式配置于基板100的主动区AA上。换句话说,像素结构PX沿着横向方向X以及纵向方向Y呈现阵列排列。在本实施例中,每一像素结构PX与其中一条横向信号线GL以及其中一条第一纵向信号线DL电性连接。另外,第二纵向信号线110没有直接连接像素结构PX。举例来说,每一像素结构PX可包括薄膜晶体管(未示出)及像素电极(未示出),其中所述薄膜晶体管的源极与栅极可分别电性连接至对应的一条第一纵向信号线DL及对应的一条横向信号线GL,而所述像素电极电性连接至所述薄膜晶体管的漏极。

多个像素结构PX可沿横向方向X按序排列成像素列R1~像素列Rn(以下有时略称为多个像素列R),且可沿纵向方向Y按序排列成像素行C1~像素行Cm(以下有时略称为多个像素行C),其中n及m可与上述多条横向信号线GL的n及多条第一纵向信号线DL的m同义。举例来说,多个像素列R在纵向方向Y上按序排列;每一像素列R的多个像素结构PX在横向方向X上按序排列。多个像素行C在横向方向X上按序排列;每一像素行C的多个像素结构PX在纵向方向Y上按序排列,但本发明不以此为限。在本实施例中,位于像素行Cx及像素列Ry的一像素结构PX的坐标为(x,y),以下表示为像素结构PXxy,其中x及y为正整数,且1≦x≦m,1≦y≦n。举例来说,位于像素行C1及像素列R1的一像素结构PX的坐标为(1,1),以下表示为像素结构PX11;位于像素行C1及像素列Rn的一像素结构PX的坐标为(1,n),以下表示为像素结构PX1n;位于像素行Cm及像素列Rn的一像素结构PX的坐标为(m,n),以下表示为像素结构PXmn。

在本实施例中,其中一像素结构PX被相邻两条横向信号线GL以及相邻两条第一纵向信号线DL围绕。举例来说,以像素结构PX11为例,像素结构PX11被横向信号线GL1、横向信号线GL2、第一纵向信号线DL1及第一纵向信号线DL2围绕。在本实施例中,同一像素行C的多个像素结构PX可选择性地电性连接至同一条第一纵向信号线DL,且相邻的两像素列R的多个像素结构PX可分别电性连接至不同的多个横向信号线GL。简言之,在本实施例中,像素阵列10可采一条栅极线一条数据线(one gate line and one data line,1G1D)的驱动方式,但本发明不以此为限。在一些实施例中,同一像素行C的多个像素结构PX可选择性地按序与不同侧的第一纵向信号线DL电性连接。举例来说,在像素行C1中,如像素结构PX11等位于单数列的像素结构PX可电性连接位于第一侧(如图1A的左侧)的第一纵向信号线DL1,另一方面,如像素结构PX12等位于双数列的像素结构PX可电性连接位于第二侧(如图1A的右侧)的第一纵向信号线DL2,但本发明不限于此。

在本实施例中,像素阵列10于周边区BA还可具有多个栅极驱动垫GD。多个栅极驱动垫GD可横向按序排列于基板100的周边区BA,且每一栅极驱动垫GD电性连接其中一条第二纵向信号线110。举例来说,多个栅极驱动垫GD可包括栅极驱动垫GD1、栅极驱动垫GD2、…、栅极驱动垫GDp,其中p为正整数,栅极驱动垫GD1、栅极驱动垫GD2、…、栅极驱动垫GDp可按序分别与对应的第二纵向信号线110-1、第二纵向信号线110-2、…、第二纵向信号线110-p电性连接。在一些实施例中,在第二纵向信号线110-1、第二纵向信号线110-2、…、第二纵向信号线110-p分别与不同的多个横向信号线GL电性连接处可设置有对应的导通结构CS1、导通结构CS2、…、导通结构CSp,但本发明不以此为限。举例来说,如图1A所示,第二纵向信号线110-1的一端连接于栅极驱动垫GD1,第二纵向信号线110-1的另一端通过导通结构CS1而与横向信号线GL1电性连接。

请参照图1A,值得注意的是,本实施例的像素阵列10中的至少一条第二纵向信号线110包含横向图案114,通过横向图案114能够将第二纵向信号线110在纵向方向适度地分段,可降低第二纵向信号线110对相邻第一纵向信号线DL传递信号时所产生的耦合现象,进而改善像素阵列的品质。在本实施例的像素阵列10中,至少一条第二纵向信号线110不包含横向图案114。举例来说,如图1A所示,第二纵向信号线110-1、第二纵向信号线110-3包含横向图案114,第二纵向信号线110-2、第二纵向信号线110-4不包含横向图案114,但本发明不限于此。

在一些实施例中,横向图案114沿横向方向X延伸的长度L大于等于一个像素结构PX的横向宽度Wx。举例来说,第二纵向信号线110-3的横向图案114-3大致上自第一纵向信号线DL7延伸至第一纵向信号线DL13,换言之,横向图案114-3大致上跨越了六个像素结构PX。也就是说,横向图案114-3的长度L例如相当于六个像素结构PX的横向宽度Wx的总和。在一些实施例中,横向图案114的长度L可相当于一个像素结构PX的横向宽度Wx,所属领域中技术人员可依据设计需求调整横向图案的长度,本发明并不以此为限。

在本实施例中,包含有横向图案114的第二纵向信号线110还可包含第一纵向图案112以及第二纵向图案116。第一纵向图案112及第二纵向图案116例如分别邻接于横向图案114的两端,且第一纵向图案112及第二纵向图案116分别相邻于不同的第一纵向信号线DL。在一些实施例中,第一纵向图案112可电性连接对应的栅极驱动垫GD;第二纵向图案116可电性连接对应的横向信号线GL。因此,来自栅极驱动源(未示出)的信号经由对应的栅极驱动垫GD传递至对应的第二纵向信号线110,再经由第二纵向信号线110将信号经由横向图案114或直接传递给横向信号线GL,再由横向信号线GL输入给位于同一列像素结构PX的栅极,借此开启或关闭该列像素结构PX的薄膜晶体管。举例来说,第二纵向信号线110-1的第一纵向图案112-1自栅极驱动垫GD1沿第一纵向信号线DL1延伸至横向图案114-1,横向图案114-1沿横向信号线GL2延伸至第二纵向图案116-1,第二纵向图案116-1再沿着第一纵向信号线DL7延伸至横向信号线GL1,并且第一纵向图案112、横向图案114及第二纵向图案116按序电性连接。

请参照图1B,图1B是图1A的像素阵列中沿剖线A-A’的剖面示意图。第一纵向图案112与第二纵向图案116位于相同膜层中,且横向图案114所在的膜层不同于第一纵向图案112与第二纵向图案116所在的膜层。举例来说,横向图案114可与横向信号线GL位于第一导体层M1,第一纵向图案112与第二纵向图案116可与第一纵向信号线DL位于第一导体层M1上方的第二导体层M2,但本发明不以此为限。在一些实施例中,第一导体层M1及第二导体层M2之间还夹设有第一绝缘层I1,在第二导体层M2上还覆盖有第二绝缘层I2。绝缘层I1具有第一通孔V1及第二通孔V2,在基板100的俯视方向上,第一通孔V1及第二通孔V2例如分别与第一纵向图案112及第二纵向图案116重叠,且第一通孔V1及第二通孔V2例如暴露出横向图案114的一部分。另外,第一转接结构120可设置于第一通孔V1内,第二转接结构122可设置于第二通孔V2内,换句话说,如图1A所示,第一转接结构120可设置于第一纵向图案112与横向图案114的相交处,第二转接结构122可设置于第二纵向图案116与横向图案114的相交处。因此,第一纵向图案112可通过第一转接结构120连接横向图案114,横向图案114可通过第二转接结构122连接第二纵向图案116。如此,栅极需要的信号可通过第二纵向信号线110的横向图案114在不同膜层之间传递,以跨越多条第一纵向信号线DL,使得第二纵向信号线110的布线设计较不受限,且可用于调整第二纵向信号线110与对应的横向信号线GL的电性连接处(例如导通结构CS的位置)。

在本实施例中,不包含横向图案114的第二纵向信号线110可散乱地穿插于同一第二纵向信号线110所具有的第一纵向图案112及第二纵向图案116之间。举例来说,如图1A所示,在基板100的俯视方向上,第二纵向信号线110-2例如位于第二纵向信号线110-1的第一纵向图案112-1及第二纵向图案116-1之间;第二纵向信号线110-4例如位于第二纵向信号线110-3的第一纵向图案112-3及第二纵向图案116-3之间。如此一来,多个导通结构CS可散乱地分布在像素阵列10上(例如图1A所示),使得由第一纵向信号线DL与第二纵向信号线110的耦合效应所引起的亮度异常(例如:偏亮)的多个像素结构PX也会散乱地分布在像素阵列10上。由于亮度异常(例如:偏亮)的多个像素结构PX是散乱地分布在像素阵列10上,因此人眼不易察觉由第一纵向信号线DL与第二纵向信号线110的耦合效应所引起的显示画面异常(例如呈现一对应于基板对角线的亮线)。此外,本实施例的像素阵列10通过有意地使导通结构CS散乱分布的布局设计,可以减少需于周边区BA额外设置周边电路走线来使第二纵向信号线110与横向信号线GL的导通结构CS乱序化的空间,实现窄边框的设计。

图2是依照本发明的第二实施例的一种像素阵列的俯视示意图。为方便说明,图2中省略示出绝缘层的位置及部分像素结构PX。在此必须说明的是,图2沿用图1A及图1B的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参照前述实施例,在此不赘述。

请参照图2,第二实施例的像素阵列20与第一实施例的像素阵列10的不同处为本实施例的像素阵列20还具有定电压线200。定电压线200可提供一固定电压。在本实施例中,定电压线200可提供例如源自驱动元件的低电平电压Vgl(例如相较于第二纵向信号线110所传递的高电平电压Vgh),但本发明不以此为限。在一些实施例中,定电压线200可具有横向延伸的主线段202及纵向延伸的支线段204。主线段202例如与横向信号线GL平行。支线段204例如自主线段202沿多条第一纵向信号线DL的其中一者延伸,且跨越c个像素结构PX,其中c为正整数。在一些实施例中,在基板100的主动区AA中,以图2中标示为110-p的第二纵向信号线为例,基板100的主动区AA沿纵向方向Y的长度D1相当于第二纵向信号线110沿纵向方向Y的长度D2与支线段204沿纵向方向Y的长度D3的总和,但本发明不以此为限。

在本实施例中,在纵向方向Y上,第二纵向信号线110例如仅延伸至导通结构CS处,支线段204可重叠于第二纵向信号线110的延伸方向上。在基板100的俯视方向上,支线段204的相对于主线段202的一端与第二纵向信号线110及横向信号线GL的电性连接处(例如导通结构CS)可相隔一距离D4,使得位于同一延伸线上的主线段202与第二纵向信号线110彼此电性分离,分别传送不同的信号。主线段202与第二纵向信号线110之间的距离D4例如小于一个像素结构PX的纵向长度Wy。举例来说,距离D4约为3μm~5μm,距离D4只要能使主线段202与第二纵向信号线110的信号不彼此干扰即可,本发明不以此为限。

因此,同一第一纵向信号线DL在紧邻于定电压线200的支线段204处例如感受到低电平电压Vgl,在紧邻于第二纵向信号线110处例如感受到高电平电压Vgh,如此可减少第一纵向信号线DL感受到高电平电压Vgh的范围,而可避免第一纵向信号线DL与第二纵向信号线110之间耦合效应的产生,且可确保第一纵向信号线DL维持一定电平的输出电压,进而改善像素阵列的品质。

图3A是依照本发明的第三实施例的一种像素阵列的俯视示意图;图3B是图3A的像素阵列中沿剖线A-A’的剖面示意图;图4是依照本发明的第三实施例的另一种像素阵列的俯视示意图。为方便说明,图3A及图4中省略示出绝缘层的位置及部分像素结构PX。在此必须说明的是,图3A、图3B及图4沿用图2的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参照前述实施例,在此不赘述。

请参照图3A及图4,第三实施例的像素阵列30A及像素阵列30B相较于第二实施例的像素阵列20的不同处为每一第二纵向信号线310包含横向图案314。亦即,前述实施例的像素阵列10与像素阵列20中的导通结构CS在综观上呈散乱分布,相对于此,第三实施例的像素阵列30A及像素阵列30B中的导通结构CS并非是散乱排列的,而是大致上排列于一直线上。在本实施例中,每一第二纵向信号线310的横向图案314可跨越同等数量的像素结构PX。举例来说,如图3A及图4所示,每一第二纵向信号线310的横向图案314跨越相当于三个像素结构PX的宽度。换言之,如图3B所示,第二纵向信号线310的横向图案314可跨越三条第一纵向信号线DL,但本发明不以此为限。在其他实施例中,每一第二纵向信号线310的横向图案314也可跨越不同数量的像素结构PX,可依据设计需求调整第二纵向信号线310的横向图案314所跨越的像素结构PX的数量。

在一些实施例中,每一第二纵向信号线310的第一纵向图案312在纵向方向Y上可跨越a个像素结构PX,第二纵向图案316在纵向方向Y上可跨越b个像素结构PX,其中a、b为正整数。换言之,在基板100的主动区AA中,第一纵向图案312在纵向方向Y上的长度La可大于或等于a个像素结构PX的纵向长度Wy的总和,第二纵向图案316在纵向方向Y上的长度Lb可大于或等于b个像素结构PX的纵向长度Wy的总和。

在一些实施例中,每一第二纵向信号线310的第一纵向图案312在纵向方向Y上的长度La可彼此不相同,但本发明不以此为限。在其他实施例中,每一第二纵向信号线310的第一纵向图案312在纵向方向Y上的长度La也可彼此相同,可依据设计需求调整第一纵向图案312在纵向方向Y上的长度La。

在一些实施例中,第二纵向图案316在纵向方向Y上的长度Lb可彼此相同。在一些实施例中,第二纵向图案316在纵向方向Y上的长度Lb可小于第一纵向图案312在纵向方向Y上的长度La。由于第二纵向信号线310的第二纵向图案316连接导通结构CS,当信号写入至紧邻于该导通结构CS的像素结构PX时容易因第二纵向信号线310与第一纵向信号线DL之间产生的耦合效应影响像素结构的栅极/漏极电容,因此第二纵向图案316的长度Lb小于第一纵向图案312的长度La可进一步避免第二纵向信号线310与第一纵向信号线DL之间产生耦合效应。举例来说,如图4所示,每一第二纵向信号线310的第二纵向图案316在纵向方向Y上可相当于跨越一个像素结构PX,即b可为1,换言之,第二纵向图案316在纵向方向Y上的长度Lb可相当于一个像素结构PX的纵向长度Wy,但本发明不以此为限。以图中第二纵向信号线310-2为例,第二纵向信号线310-2于预定时序中经由导通结构CS2开启图中像素列R1的像素结构PX,被开启的像素列R1的像素结构PX分别经由对应的第一纵向信号线DL7被输入对应的信号,此时,由于靠近正在信号写入的像素列R1像素结构PX的第二纵向图案316的长度Lb较短,使得第二纵向图案316的信号对与其相邻的第一纵向信号线DL7的信号耦合影响较为有限,故能有效降低第二纵向信号线310-2与第一纵向信号线DL7的耦合效应所引起的显示画面异常。

如此一来,通过每一第二纵向信号线310包含横向图案314,可减少第二纵向信号线310于第二纵向图案316的长度,而可避免第二纵向信号线310与第一纵向信号线DL之间产生耦合效应,而可减少栅极/漏极电容。另外,即使因第一纵向信号线DL与第二纵向信号线110的耦合效应造成多个像素结构PX的亮度异常,由于所产生的亮度变化量并不明显,因此人眼仍不易察觉由第一纵向信号线DL与第二纵向信号线110的耦合效应所引起的显示画面异常。

图5是依照本发明的第四实施例的一种像素阵列的局部俯视示意图。为方便说明,图5中省略示出绝缘层的位置。在此必须说明的是,图5沿用图1A的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参照前述实施例,在此不赘述。

请参照图5,第四实施例的像素阵列40与第一实施例的像素阵列10的不同处为像素阵列40还具有绝缘层覆盖第一纵向信号线DL与第二纵向信号线110,且所述绝缘层具有沟槽TR。在本实施例中,共用电极COM可覆盖沟槽TR的表面。因此,可用于屏蔽(shielding)第二纵向信号线110与第一纵向信号线DL彼此之间的干扰,以降低线路之间的耦合所造成的不良影响。举例来说,通过共用电极COM覆盖沟槽TR的表面且沟槽TR位于第二纵向信号线110与第一纵向信号线DL之间,使得第二纵向信号线110所产生的电场受到屏蔽,而不会耦合至第一纵向信号线DL,如此可确保第一纵向信号线DL维持一定电平的输出电压,进而改善像素阵列的品质(例如画面显示等)。

在本实施例中,沟槽TR沿第一纵向信号线DL与第二纵向信号线110的第二纵向图案116延伸。并且,沟槽TR在基板100的投影例如位于第二纵向信号线110的第二纵向图案116在基板100的投影与第一纵向信号线DL在基板100的投影之间。举例来说,沟槽TR的侧壁分别与第二纵向信号线110的第二纵向图案116的侧面及第一纵向信号线DL的侧面例如相隔一距离,且所述距离的下限优选为2.0μm,优选为3.0μm。另外,所述距离的上限优选为6.0μm,优选为5.0μm。在一些实施例中,沟槽TR可分别与第二纵向信号线110的第二纵向图案116及第一纵向信号线DL相距约2.0μm~6.0μm。值得说明的是,沟槽的实施形态可以依据设计需求而进行调整,本发明并不以此为限。

举例来说,以图1B的实施例为例,沟槽TR可位于第二绝缘层I2内。在一些实施例中,沟槽TR的深度可相当于第二绝缘层I2的膜厚。在一些实施例中,沟槽TR可自第二绝缘层I2延伸至第一绝缘层I1中。举例来说,沟槽TR的深度可大于第二绝缘层I2的膜厚,且小于第一绝缘层I1的膜厚。在其他实施例中,沟槽TR的深度可小于第二绝缘层I2的膜厚。另外,在一些实施例中,第二绝缘层I2可包括上部绝缘层及下部绝缘层(未示出),且沟槽TR的深度可相当于上部绝缘层的膜厚。在一些实施例中,沟槽TR可自上部绝缘层延伸至下部绝缘层中。举例来说,沟槽TR的深度可大于上部绝缘层的膜厚,且小于下部绝缘层的膜厚。在其他实施例中,沟槽TR的深度可小于上部绝缘层的膜厚。

综上所述,本发明的像素阵列通过其中一条第二纵向信号线包含横向图案,能够将第二纵向信号线在纵向方向上适度地分段,以减少第二纵向信号线紧邻于与横向信号线的电性连接处的长度,可降低第二纵向信号线与相邻的第一纵向信号线之间所产生的耦合效应,有助于在实现窄边框设计需求的同时,改善像素阵列的品质。

虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的构思和范围内,当可作些许的变动与润饰,故本发明的保护范围当视权利要求所界定者为准。

- 像素阵列、像素阵列的制造方法和显示装置

- 像素阵列和包括该像素阵列的图像传感器