对多平面存储器件进行编程的方法和多平面存储器件

文献发布时间:2023-06-19 11:26:00

本申请是申请日为2020年2月20号提交的题为“对多平面存储器件进行编程的方法”的申请号为202080000277.8的专利申请的分案申请。

技术领域

本发明涉及存储器控制,并且具体涉及对多平面存储器件进行编程的方法。

背景技术

非易失性存储器已广泛用于个人计算机、电信、消费电子和其它领域。电可擦除可编程只读存储器(EEPROM)和闪存是其中最广泛使用的非易失性存储器。

根据存储器阵列的结构配置,可以将存储器件分为单平面类型和多平面类型。单平面类型存储器件包括被组织成单个平面的存储器阵列,而多平面类型存储器件包括被组织成多个平面的存储器阵列。当对多平面类型存储器件进行编程时,可以同时对两个或更多个平面进行编程以提高编程效率。然而,当多平面类型存储器件包含有缺陷的平面时,普通平面和有缺陷的平面都将被重复编程,以试图将数据编程到有缺陷的平面中,从而降低编程速度、降低编程效率、并且增加正常平面中的程序干扰。

发明内容

根据一个实施例,一种存储器件包括多个平面、行驱动器和控制器。一种对存储器件进行编程的方法,包括:在编程操作中,行驱动器向多个平面中的第一平面的多个存储单元施加编程脉冲;在行驱动器向多个存储单元施加编程脉冲之后,控制器验证所述多个存储单元是否已经达到预定编程状态;以及,如果在所述多个存储单元已经被验证了预定次数之后,所述多个存储单元中的预定数量的存储单元还未达到预定的编程状态,则所述控制器禁用所述第一平面。

在阅读以下在各个附图和附图中示出的优选实施例的详细描述之后,本发明的这些和其它目的对于本领域普通技术人员无疑将变得明显。

附图说明

图1是根据本发明实施例的存储器件的框图。

图2是图1中的平面的存储单元的页面的示意图。

图3是图1中的列驱动器和控制器的框图。

图4是图1中的控制器的选择电路的示意图。

图5是对图1中的存储器件进行编程的方法的流程图。

图6是对图1中的存储器件进行编程的另一方法的流程图。

具体实施方式

尽管将参照二维NAND闪存器件来描述本发明的实施例,但是应当理解,本发明构思的实施例不限于此配置,而是还可应用于三维NAND闪存存储器件。另外,在不脱离本发明的范围的情况下,本发明可适用于其它非易失性存储器件,例如,电可擦除可编程只读存储器(EEPROM)、NOR闪存存储器、相变RAM(PRAM)、磁性RAM(MRAM)、电阻性RAM(RRAM)、铁电RAM(FRAM)等。

图1是根据本发明的实施例的存储器件1的框图。存储器件1具有双平面结构,并且可以包括控制器10、电压生成电路11、行解码器12、列驱动器131、132和平面141、142。尽管在该实施例中使用了双平面结构,但是应当理解,在本发明的范围内也可以采用其它数量的平面。可以同时对平面141、142进行编程。在进行编程之后,如果平面141或平面142被验证为失败达到预定次数,则行驱动器12可以禁止对失败的平面141或142进行后续编程。对失败的平面的禁止减少了尝试对其进行编程所花费的时间,并减少了操作平面中的程序干扰。

控制器10可以耦接到电压生成电路11和列驱动器131、132。电压生成电路11可以耦接到行驱动器12。行驱动器12可以经由串选择线SSL1、字线WL1(1)到WL1(N)以及接地选择线GSL1耦接到平面141,N是正整数,例如,N=64。行驱动器12可以经由串选择线SSL2、字线WL2(1)至WL2(N)以及接地选择线GSL2耦接到平面142。列驱动器131可以经由位线BL1(1)到BL1(M)耦接到平面141,M是正整数,例如,M=8192。列驱动器132可以经由位线BL2(1)至BL2(M)耦接到平面142。平面141、142中的每一个可以包含多个块,每个块可以包含多个页面,并且每个页面可以包含存储单元的阵列。平面141中的存储单元的阵列可以通过字线WL1(1)到WL1(N)以及位线BL1(1)至BL1(M)进行寻址,并且平面142中的存储单元的阵列可以通过字线WL2(1)至WL2(N)以及位线BL2(1)到BL2(M)进行寻址。

控制器10可以与外部主机进行通信以接收数据以便存储在平面141、142中并发送从平面141、142获取的数据。控制器10可以从外部主机接收命令、地址或数据并且生成列地址信号Scadr1、Scadr2、行地址信号Sradr以及电压控制信号Svc。响应于来自控制器10的电压控制信号Svc,电压生成电路11可以生成用于读取、编程、擦除和验证操作的电压。电压生成电路11生成的电压可能超过提供给存储器件1的电源电压。行驱动器12可以响应于来自控制器10的行地址信号Sradr而操作,以便选择用于读取、编程、擦除和验证操作的字线。列驱动器131、132可以响应于来自控制器10的列地址信号Scadr1、Scadr2而操作,以便生成位线信号以选择用于读取、编程、擦除和验证操作的位线。在编程操作中,电压生成电路11可以使用电源电压(例如,3.3V)来生成编程电压(例如,20V)和编程通过电压(例如,10V),行驱动器12可以向所选择的字线施加具有编程电压的幅度的编程脉冲,向未选定的字线施加编程通过电压,向串选择线SSL1、SSL2施加电源电压,以及向接地选择线GSL1、GSL2施加接地电压,并且列驱动器131、132可以向所选择的位线施加接地电压(例如,0V),以及向未选定的位线施加电源电压。在验证操作中,电压生成电路11可以生成合适的验证电压,行驱动器12可以将合适的验证电压施加到所选择的字线,将电源电压施加到串选择线SSL1、SSL2,并且将电源电压施加到接地选择线GSL1、GSL2,并且列驱动器131、132可以将接地电压施加到未选择的位线,并且将电源电压分别施加到平面141、142的被选择的位线以便在所选择的位线上从所选择的存储单元中读取数据。如果数据读取是不正确的,则控制器10可以将所选择的存储单元验证为失败,而如果数据读取是正确的,则控制器10可以将所选择的存储单元验证为通过。

图2是平面141、142中的页面的示意图。所述页面可以包括存储单元C(1,1)至C(M,N)、串选择单元Css(1)至Css(M)以及接地选择单元Cgs(1)至Cgs(M)。存储单元C(1,1)至C(M,N)可以是浮栅晶体管或电荷捕获晶体管,并且存储单元C(1,1)至C(M,N)、串选择单元Css(1)至Css(M)以及接地选择单元Cgs(1)至Cgs(M)中的每一个可以包括控制端、第一端和第二端。串选择线SSLn可以耦接到串选择单元Css(1)至Css(M)的控制端,并且位线BL(1)到BL(M)可以分别耦接到串选择单元Css(1)至Css(M)的第一端。存储单元C(1,1)至C(M,N)可以布置成耦接至相应字线WL(1)至WL(N)的存储单元的行。字线WL(1)至WL(N)可以分别耦接至第一行的存储单元C(1,1)至C(M,1)的控制端、耦接至第N行的存储单元C(1,N)至C(M,N)的控制端,并且存储单元C(1,1)至C(M,1)的第一端可以分别耦接到串选择单元Css(1)到Css(M)的第二端。接地选择线GSLn可以耦接到接地选择单元Cgs(1)至Cgs(M)的控制端,接地选择单元Cgs(1)至Cgs(M)的第一端可以分别耦接到存储单元C(1,N)至C(M,N)的第二端,并且接地选择单元Cgs(1)到Cgs(M)的第二端可以耦接到接地端。接地端可以提供接地电压。

存储单元C(1,1)至C(M,N)可以是单级单元(SLC)类型、多级单元(MLC)类型、三级单元(TLC)类型、四级单元(QLC)类型、五级单元(PLC)类型或更高级别类型。每个存储单元C(m,n)可以保持Q个可能的数据状态之一,其中,Q是等于或大于2的正整数,例如,对于SLC,Q=2,对于MLC,Q=4,对于TLC,Q=8,对于QLC,Q=16,并且对于PLC,Q=32。Q个可能的数据状态可以包括擦除状态S(0)和编程状态S(1)至S(Q-1),其中,编程状态S(1)是最低编程状态,而编程状态S(Q-1)处于最高编程状态。在一个示例中,TLC可以被编程为8种可能的数据状态之一,其中,编程状态S(1)是最低编程状态,而编程状态S(7)是最高编程状态。

存储单元C(1,1)至C(M,N)可以起初设置为擦除状态S(0),并且稍后,可以对存储单元C(1,1)至C(M,N)执行一系列编程验证操作,以便将其编程为相应的目标编程状态。一系列编程验证操作可以从最低编程状态S(1)开始,然后进行到较高的编程状态,直到所选择的存储单元的阈值电压达到相应的目标编程状态的相应验证电压电平为止。在一些实施例中,可以将验证电压分别选择作为编程状态S(1)至S(Q-1)的阈值电压分布曲线的最小阈值电压。每个编程验证操作可以包括编程操作和后续的验证操作。在编程操作中,可以选择存储单元C(1,1)至C(M,N)中的一些并且按照从第一行到第N行、或者从第N行到第一行的逐行方式编程到编程状态中。在后续的验证操作中,控制器10可以按照从第一行到第N行或者从第N行到第一行的逐行方式来验证所选择的存储单元是否已经达到编程状态。通过这种方式,可以将存储单元C(1,1)至C(M,N)编程到相应的目标编程状态中。

图3是列驱动器131、132和控制器10的框图。列驱动器131、132中的每一个可以包括页面缓冲器301至30n、失败比特计数器321至32n、以及列解码器341至34n。控制器10可以包括加法器36。在一些实施例中,列驱动器131、132还可以包括灵敏放大器,以检测来自所选择的位线的电流,从而分别从平面141、142读取数据。页面缓冲器301至30n可以分别耦接至失败比特计数器321至32n。失败比特计数器321至32n可以分别耦接至列解码器341至34n。列解码器341至34n可以耦接至加法器36。在一些实施例中,加法器36可以位于列驱动器131、132中的每一个中,并且可以耦接至控制器10。

当验证平面141、142的编程状态S(q)时,列解码器341至34n可以在列地址信号Scadr1、Scadr2中接收列地址,以选择平面141、142的位线,从而分别从平面141、142的页面中的被选择的存储单元中获取数据到页面缓冲器301至30n。失败比特计数器321至32n可以分别对平面141、142的页面中被验证为失败的存储单元的数量进行计数,以便生成页面失败比特计数。加法器36可以累加平面141的所有页面的页面失败比特计数以生成第一平面失败比特计数,并且累加平面142的所有页面的页面失败比特计数以生成第二平面失败比特计数。如果第一平面失败比特计数小于预设的平面失败比特计数,则控制器10可以将平面141验证为通过,而如果第一平面失败比特计数超过预设的平面失败比特计数,则控制器10可以将平面141验证为失败。类似地,如果第二平面失败比特计数小于预设的平面失败比特计数,则控制器10可以将平面142验证为通过,而如果第二平面失败比特计数超过预设的平面失败比特计数,则控制器10可以将平面142验证为失败。当平面141、142被验证为失败达到预定次数(例如,4次)时,控制器10可以禁用平面141、142。当平面141、142被验证为失败达到预定次数之前被验证为通过时,控制器10可以继续将平面141、142编程到下一编程状态S(q+1)中。

当平面141和/或平面142被验证为通过时,控制器10可以生成用于指示编程通过的失败比特通过信号,而当平面141和平面142都被验证为失败时,控制器10可以生成用于指示编程失败的失败比特通过信号。所述失败比特通过信号可以用于判断是否继续对存储器件1进行编程。在一些实施例中,控制器10可以将失败比特通过信号设置为逻辑高以继续对存储器件1进行编程,而将失败比特通过信号设置为逻辑低以停止对存储器件1进行编程。在一些实施例中,控制器10还可以在退出编程验证操作时生成用于指示编程结果的状态报告。当平面141、142中的至少一个平面完成最高状态S(Q-1)的编程时,状态报告可以指示编程通过。当在完成最高状态S(Q-1)的编程之前两个平面141、142都被禁用时,状态报告可以指示编程失败。当施加到存储器件1的编程脉冲超过最大编程脉冲计数时,状态报告可以指示编程失败。

图4是控制器10中的选择电路的示意图。控制器10可以包括与门41和42以分别控制对平面141和142的访问。与门41可以接收平面地址信号Sap1、失败比特通过信号Sfbp以及平面禁用信号Sdisp1,以生成平面选择信号Ssp1。与门42可以接收平面地址信号Sap2、失败比特通过信号Sfbp以及平面禁用信号Sdisp2,以生成平面选择信号Ssp2。控制器10可以根据平面选择信号Ssp1来生成列地址信号Scadr1,根据平面选择信号Ssp2来生成列地址信号Scadr2,以及根据平面选择信号Ssp1、Ssp2来生成行地址信号Sradr。在一些实施例中,当确定禁用平面141时,控制器10可以将平面禁用信号Sdisp1设置为逻辑低,与门41可以响应于平面禁用信号Sdisp1来通过将平面选择信号Ssp1设置为逻辑低来阻止平面选择信号Ssp1,并且控制器10可以生成行地址信号Sradr和列地址信号Scadr1以取消选择平面141的字线WL1(1)至WL1(N)以及位线BL1(1)至BL1(M)。同样,当确定禁用平面142时,控制器10可以将平面禁用信号Sdisp2设置为逻辑低,与门42可以响应于平面禁用信号Sdisp2通过将平面选择信号Ssp2设置为逻辑低来阻止平面选择信号Ssp2,并且控制器10可以生成行地址信号Sradr和列地址信号Scadr2以取消选择平面142的字线WL2(1)至WL2(N)以及位线BL2(1)至BL2(M)。

在一些实施例中,与门41可以接收第一块地址信号来代替平面地址信号Sap1以生成第一块选择信号,并且与门42可以接收第二块地址信号来代替平面地址信号Sap2以生成第二块选择信号。控制器10可以根据第一块选择信号来生成列地址信号Scadr1,根据第二块选择信号来生成列地址信号Scadr2,并且根据第一块选择信号和第二块选择信号来生成行地址信号Sradr。在一些实施例中,当确定禁用平面141时,控制器10可以将平面禁用信号Sdisp1设置为逻辑低,与门41可以响应于平面禁用信号Sdisp1,通过将第一块选择信号设置为逻辑低来阻止第一块选择信号,并且控制器10可以生成行地址信号Sradr和列地址信号Scadr1以取消选择平面141的字线WL1(1)至WL1(N)和位线BL1(1)至BL1(M)。类似地,当确定禁用平面142时,控制器10可以将平面禁用信号Sdisp2设置为逻辑低,与门42可以响应于平面禁用信号Sdisp2,通过将第二块选择信号设置为逻辑低来阻止第二块选择信号,并且控制器10可以生成行地址信号Sradr和列地址信号Scadr2以取消选择平面142的字线WL2(1)至WL2(N)以及位线BL2(1)至BL2(M)。

控制器10可以利用编程状态计数器q、失败验证计数Cvf1、Cvf2以及编程脉冲计数Cp来生成平面禁用信号Sdisp1、Sdisp2,以控制对平面141、142的访问。编程状态计数器q可以是范围介于1和(Q-1)之间的正整数。失败验证计数Cvf1、Cvf2可以是范围介于1和最大失败计数Cvmax(q)之间的正整数。最大失败计数Cvmax(q)可以定义在禁用平面之前执行对编程状态S(q)的验证的最大次数,并且可以专门针对编程状态S(q)。例如,可以为编程状态S(1)至S(7)分别分配最大失败计数Cvmax(1)至Cvmax(7)。最大失败计数Cvmax(q)可以是大于1的正整数,并且可以在制造建立期间设置。编程脉冲计数Cp可以是范围介于1和最大编程脉冲计数Cpmax之间的正整数。最大编程脉冲计数Cpmax可以定义向平面141、142施加编程脉冲的最大次数,并且可以是大于1的正整数并且在制造建立期间设置。

当平面141、142被验证为失败达到如由最大失败计数Cvmax(q)所定义的预定次数时,控制器10可以禁止平面141、14进行后续编程,从而加快数据编程并减少在操作平面中的程序干扰。

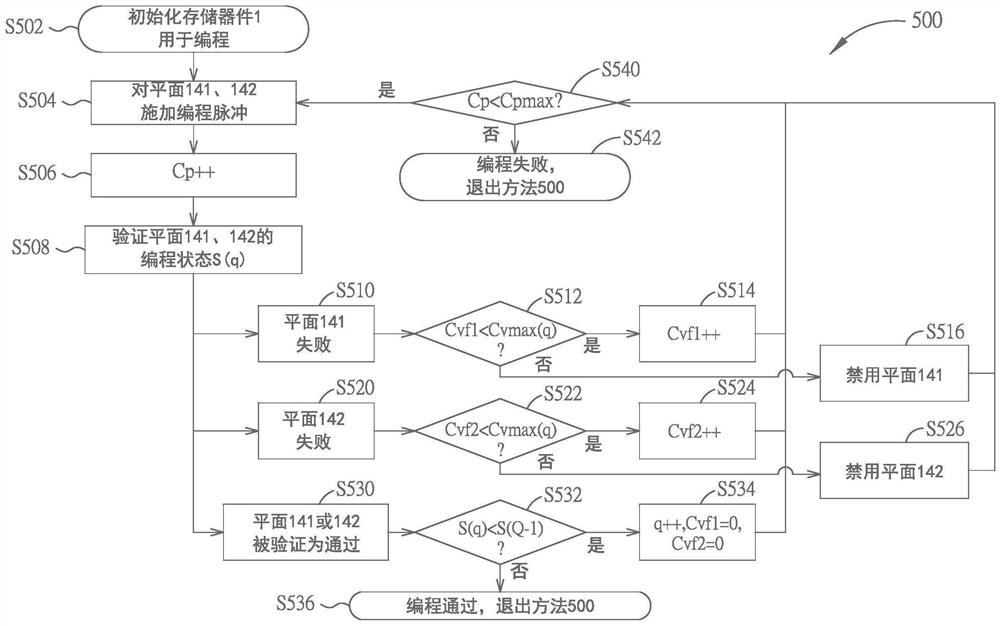

图5是对存储器件1进行编程的方法500的流程图。该方法500包括步骤S502至S542,对平面141、142执行多平面编程,并根据平面141、142的相应的失败验证计数Cvf1、Cvf2来禁用平面141、142。步骤S502至S508用于编程和验证存储器件1。步骤S512至S516用于判断是否禁用平面141。步骤S522至S526用于判断是否禁用平面142。步骤S532至S536用于完成对启用编程的平面141、142的编程。步骤S540和S542用于根据编程脉冲计数Cp来禁止对存储器件1进行编程。任何合理的步骤改变或调整都落在本公开内容的范围内。步骤S502至S542被如下解释:

步骤S502:控制器10对编程脉冲计数Cp、失败验证计数Cvf1、Cvf2和编程状态计数器q进行复位;

步骤S504:行驱动器12将编程脉冲施加到平面141、142;

步骤S506:控制器10递增编程脉冲计数Cp;

步骤S508:控制器10验证平面141、142的编程状态S(q);

步骤S510:控制器10已将平面141验证为失败;

步骤S512:控制器10判断失败验证次数Cvf1是否小于最大失败次数Cvmax(q);如果是,则执行步骤S514;而如果否,则执行步骤S516;

步骤S514:控制器10递增失败验证计数Cvf1;执行步骤S540;

步骤S516:控制器10禁用平面141;执行步骤S540;

步骤S520:控制器10已将平面142验证为失败;

步骤S522:控制器10判断失败验证计数Cvf2是否小于最大失败计数Cvmax(q);如果是,则执行步骤S524;而如果否,则执行步骤S526;

步骤S524:控制器10递增失败验证计数Cvf2;执行步骤S540;

步骤S526:控制器10禁用平面142;执行步骤S540;

步骤S530:控制器10已将平面141或142验证为通过;

步骤S532:控制器10判断编程状态S(q)是否小于最高编程状态S(Q-1)?如果是,则执行步骤S534,而如果否,则执行步骤S536;

步骤S534:控制器10递增编程状态S(q),并且对失败验证计数Cvf1、Cvf2进行复位;执行步骤S540;

步骤S536:控制器10生成用于指示编程通过的状态报告;退出方法500;

步骤S540:控制器10判断编程脉冲计数Cp是否小于最大编程脉冲计数Cpmax;如果是,则执行步骤S504,而如果否,则执行步骤S542;

步骤S542:控制器10生成用于指示编程失败的状态报告;退出方法500。

可以使用存储器件1和TLC存储单元来举例说明方法500,以描述步骤的细节。在启动多平面程序时,对平面141、142初始化以进行编程。控制器10将平面禁用信号Sdisp1、Sdisp2和失败比特通过信号Sfbp设置为逻辑高,并且设置编程脉冲计数Cp、失败验证计数Cvf1、Cvf2以及编程状态计数器q(S502)。在一些实施例中,编程脉冲计数Cp和失败验证计数Cvf1、Cvf2可以被复位为0(Cp=0,Cvf1=0,Cvf2=0),并且编程状态计数器q可以被复位为1(q=1)。接下来,行驱动器12将编程脉冲施加到平面141、142的被选择的字线(S504),并且控制器10将编程脉冲计数Cp递增1(Cp=1)(S506)。控制器10验证平面141、142的存储单元是否已经达到编程状态S(1)(S508)。如果多于预设数量的平面141、142的存储单元未能达到编程状态S(1),则控制器10将平面141、142验证为失败。如果少于平面141、142的存储单元的预设数量未能达到编程状态S(1),则控制器10将平面141、142验证为通过。

如果控制器10已经将平面141验证为失败(S510),则控制器10接下来判断失败验证计数Cvf1是否小于编程状态S(1)的最大失败计数Cvmax(1)(S512)。在一些实施例中,最大失败计数Cvmax(1)可以是4。如果失败验证计数Cvf1(Cvf1=0)小于最大失败计数Cvmax(1)(Cvmax(1)=4),则控制器10对失败验证计数Cvf1递增1(Cvf1=1)(S514)。在步骤S540中,控制器10判断编程脉冲计数Cp是否小于最大编程脉冲计数Cpmax。在一些实施例中,最大编程脉冲计数Cpmax可以是20。如果编程脉冲计数Cp(Cp=1)小于最大编程脉冲计数Cpmax(Cpmax=20),则控制器10在步骤S504至S514以及步骤S540上进行重复,直到当失败验证计数Cvf1达到4时平面141仍然验证失败。当控制器10确定失败验证计数Cvf1(Cvf1=4)不小于最大失败计数Cvmax(1)(Cvmax(1)=4)时,控制器10将平面禁用信号Sdisp1设置为逻辑低,同时将失败比特通过信号Sfbp保持为逻辑高以禁用平面141(S516)。

类似地,如果控制器10已经将平面142验证为失败(S520),则控制器10接下来判断失败验证计数Cvf2(Cvf2=0)是否小于编程状态S(1)的最大失败计数Cvmax(1)(Cvmax(1)=4)(S522)。如果是,则控制器10对失败验证计数Cvf2递增1(Cvf2=1)(S524)。在步骤S540中,控制器10判断编程脉冲计数Cp(Cp=1)是否小于最大编程脉冲计数Cpmax(Cpmax=20)。如果是,则控制器10在步骤S504至S508、步骤S520至S524和步骤S540上进行重复,直到当失败验证计数Cvf2达到4时平面142仍然被验证为失败。当控制器10确定失败验证计数Cvf2(Cvf2)=4)不小于最大失败计数Cvmax(1)(Cvmax(1)=4),控制器10将平面禁用信号Sdisp2设置为逻辑低,同时将失败比特通过信号Sfbp保持为逻辑高,以禁用平面142(S526)。

如果控制器10在相应的失败验证计数Cvf1、Cvf2达到最大失败计数Cvmax(1)之前已经将平面141、142都验证为通过,或者在相应的失败验证计数Cvf1、Cvf2达到最大失败计数Cvmax(1)之前已经将平面141、142中的一个平面验证为通过并且禁用平面141、142中的另一个平面(S530),则控制器10接下来判断编程状态S(1)是否小于最高编程状态S(7)(S532)。例如,在施加第四编程脉冲(Cp=4,Cvf1=3,Cvf2=4)时,控制器10可以将平面141验证为通过并且将平面142验证为失败,禁用平面142(S526),并执行将平面141编程到下一编程状态S(2)。如果编程状态S(1)小于最高编程状态S(7),则控制器10将编程状态计数器q递增1(q=2),并将失败验证计数Cvf1、Cvf2复位到0(Cvf1=0,Cvf2=0)(S534),并且判断编程脉冲计数Cp(Cp=4)是否小于最大编程脉冲计数Cpmax(Cpmax=20)(S540)。如果是,则由于已经禁用了平面142,所以控制器10在S504至S514、步骤S530至S534、以及步骤S540上进行重复,直到禁用平面141、达到最高编程状态S(7)或者编程脉冲计数Cp达到最大编程脉冲计数Cpmax为止。当平面141和平面142都被禁用时,控制器10将平面禁用信号Sdisp1和失败比特通过信号Sfbp设置为逻辑低,生成用于指示编程失败的状态报告并退出方法500(S516)。当达到最高编程状态S(7)时,控制器10生成用于指示编程通过的状态报告并退出方法500(S536)。当编程脉冲计数Cp(Cp=20)达到最大编程脉冲计数Cpmax(Cpmax=20)时,控制器10将失败比特通过信号Sfbp设置为逻辑低,生成用于指示编程失败的状态报告并退出方法500(S542)。

在步骤S512和S522中,最大失败计数Cvmax(q)可以与其它最大失败计数Cvmax(1)至Cvmax(q-1)、Cvmax(q+1)至Cvmax(Q-1)相同或不同。例如,最大失败计数Cvmax(1)到Cvmax(7)中的两个或更多个可以相同,例如Cvmax(1)=Cvmax(2)=……=Cvmax(7)=4。在其它实施例中,最大失败计数Cvmax(1)至Cvmax(7)中的两个或更多个可以不同,例如,Cvmax(1)=4和Cvmax(2)=3。

在步骤S516和S526中,将平面禁用信号Sdisp1、Sdisp2设置为逻辑低,以将平面选择信号Ssp1、Ssp2设置为逻辑低,将第一块选择信号或第二块选择信号设置为逻辑低,或者设置用于控制字线WL1(1)至WL1(N)、WL2(1)至WL2(N)、位线BL1(1)至BL1(M)、BL2(1)至BL2(M)的其它信号,并且将串选择线SSL1、SSL2以及接地选择线GSL1、GSL2设置为逻辑低。当平面141、142中的一个平面被验证为通过时,失败比特通过信号Sfbp可以被设置为逻辑高,以继续对存储器件1进行编程。

方法500用于在平面被验证为失败达到预定次数后识别失败的平面,并且禁用所述失败的平面同时继续对正在操作的平面进行编程,从而加速数据编程并减少操作的平面中的程序干扰。

图6是对存储器件1进行编程的方法600的流程图。方法600包括:根据平面141/142的各个失败验证计数Cvf1、Cvf2,用于禁用平面141、142的步骤S602至S616。步骤S602和S604用于编程和验证存储器件1。步骤S606至S610用于判断是否禁用平面141/142。步骤S612至S616用于继续完成对启用编程的平面141、142的编程。任何合理的步骤改变或调整都落在本公开内容的范围内。步骤S602至S616被如下解释:

步骤S602:行驱动器12将编程脉冲施加到平面141、142的多个存储单元;

步骤S604:控制器10验证多个存储单元是否已经达到预定的编程状态S(q);如果是,则执行步骤S612;而如果否,则执行步骤S606。

步骤S606:控制器10判断所述多个存储单元中的预设数量的存储单元是否已有预定次数Cvmax(q)未达到预定编程状态S(q);如果是,则执行步骤S608;而如果否,则执行步骤S610。

步骤S608:控制器10禁用平面141、142;退出方法600。

步骤S610:控制器10将失败验证次数Cvf1、Cvf2递增;执行步骤S602;

步骤S612:控制器10判断预定编程状态S(q)是否是最高编程状态S(Q-1)?如果是,则执行步骤S614;而如果否,则执行步骤S616;

步骤S614:控制器10禁用平面141、142;退出方法600。

步骤S616:控制器10将预定的编程状态S(q)设置为下一编程状态S(q+1);执行步骤S602。

在先前的段落中已经提供了对步骤S602至S616的解释,并且在此将不再复述。在方法600中,当平面141、142被验证为失败达到预定次数时,控制器10可以禁用失败的平面141、142以用于后续编程,从而加速数据编程并减少操作的平面中的程序干扰。

本领域技术人员将容易地观察到,在保持本发明的教导的同时,可以对器件和方法进行多种修改和变更。相应地,以上公开内容应当被解释为仅由所附权利要求的边界和范围来限定。

- 对多平面存储器件进行编程的方法和多平面存储器件

- 对存储器件进行编程和验证的方法以及相关的存储器件