适用于哈希算法的电路系统

文献发布时间:2023-06-19 11:29:13

【技术领域】

本发明是关于一种电路系统,特别是一种适用于哈希算法的电路系统。

【背景技术】

哈希(hash)算法在计算器领域当中有非常广泛的应用,特别是用在信息安全的部分。传统的做法,都是以软件来执行哈希算法。而目前兴起的区块链与虚拟货币,也大量使用哈希算法。

请参考图1所示,其为用于执行哈希算法的现有计算器系统100的一方块示意图。计算器系统100包含一中央处理器101,以及与中央处理器101相连接的一或多个动态随机存取内存140。上述的中央处理器101与各个动态随机存取内存140都是独立封装,安装在同一块或不同块的电路板上。目前流行的内存连接规格是JEDEC固态电子协会规定的双倍率同步动态随机存取内存(DDR SDRAM)的各式规格。

上述的中央处理器101包含一或多个计算核心110,各自连接到一内存管理器120,内存管理器120连接到高速缓存(cache)130与多个动态随机存取内存140。当上述的一或多个计算核心110执行哈希算法时,需要将内容存取到系统内存当中,也就是动态随机存取内存140当中。

无论内存管理器120是否将所欲存取的系统内存内容快取到高速缓存130当中,也无论高速缓存130的管理方式采用直写(write-through)或是写回(write-back),由于内存管理器120与动态随机存取内存140之间的联机线路是在芯片封装体的外面,暴露在外界的电磁干扰信号当中,所以在高速缓存130与动态随机存取内存140之间的存取动作无法使用中央处理器101内所采用的高速频率信号,例如1GHz以上的频率信号,而必须采用较慢的频率信号,例如100~200MHz。

由此可知,利用中央处理器101执行哈希算法就会受限于上述内存存取的瓶颈。因此,亟需一种可以无需通过瓶颈就能够在芯片内部高速执行哈希算法的电路系统,以便提高计算的效率。

【发明内容】

根据一实施例,本发明提供一种适用于哈希算法的电路系统,包含:多排内存电路单元,每一排内存电路单元均包含多个位元与一组存取端口以存取多个位元的部分,其中每一组存取端口包含多个数据存取端口与多个地址存取端口;逻辑运算单元,用于执行逻辑运算以取得一哈希值,哈希值是用于指定存取多排内存电路单元当中的某一排内存电路单元当中的部分位元;以及内存管理逻辑电路,用于分别连接逻辑运算单元与多排内存电路单元所分别对应的存取端口。

在一实施例中,为了调整不同线路长度所造成的延迟与频率不匹配,电路系统更包含:暂存缓冲器单元,用于分别连接至少一排内存电路单元与内存管理逻辑电路,以便暂存自至少一排内存电路单元所存取的内容。

在一实施例中,为了适应不同种类的同步与异步芯片实作技术,多排内存电路单元包含下列其中一种电路或其任意组合:静态随机存取内存(SRAM);正反器(flip-flop);以及锁存器(latch)。

在一实施例中,为了同时提供多个逻辑运算单元以增进执行效率,其中逻辑运算单元更包含多个第二逻辑运算单元,其中每一个第二逻辑运算单元分别连接至内存管理逻辑电路,并且用于执行第二逻辑运算以分别产生一第二哈希值,其中第二哈希值是用于存取多排内存电路单元当中的某一排内存电路单元当中的部分位元。

在一实施例中,为了同时提供多个逻辑运算单元以增进执行效率,逻辑运算单元更包含多个第一逻辑运算单元,其中每一个第一逻辑运算单元用于执行第一逻辑运算,以分别令多个第二逻辑运算单元其中之一执行第二逻辑运算。在该实施例中,逻辑运算单元更包含一交换器电路(crossbar),用于分别连接多个第二逻辑运算单元与多个第一逻辑运算单元。

在一实施例中,为了替多个不冲突的存取指令进行排程,内存管理逻辑电路更包含先进先出的序列,当有多个第二逻辑运算单元欲存取不同排的内存电路单元时,是依照存取的先后顺序,排入序列依序进行处理。

在一实施例中,为了替多个不冲突的存取指令进行排程,当有多个第二逻辑运算单元欲存取不同排的内存电路单元时,内存管理逻辑电路是不依照存取的先后顺序(out-of-order)的方式进行处理。

在一实施例中,为了替冲突的存取指令进行排程,内存管理逻辑电路更包含仲裁逻辑电路,当有多个第二逻辑运算单元产生欲存取相同排的内存电路单元时,仲裁逻辑电路是依照多个第二逻辑运算单元所各自对应的编号的优先级进行处理。

在一实施例中,逻辑运算包含以太币(Ethereum)中计算伪随机数(nonce)的算法。

在一实施例中,为了方便安排绕线与尽可能让线路的长度一致,多排内存电路单元与逻辑运算单元位于同一芯片,其中逻辑运算单元被多排内存电路单元包围在芯片当中。

根据本发明所提供的电路系统,可以无需通过传统的内存存取瓶颈就能够在芯片内部高速执行哈希算法,进而提高计算的效率。

本发明所采用的具体技术,将通过以下的实施例及附呈图式作进一步的说明。

【附图说明】

图1为用于执行哈希算法的现有计算器系统的一方块示意图。

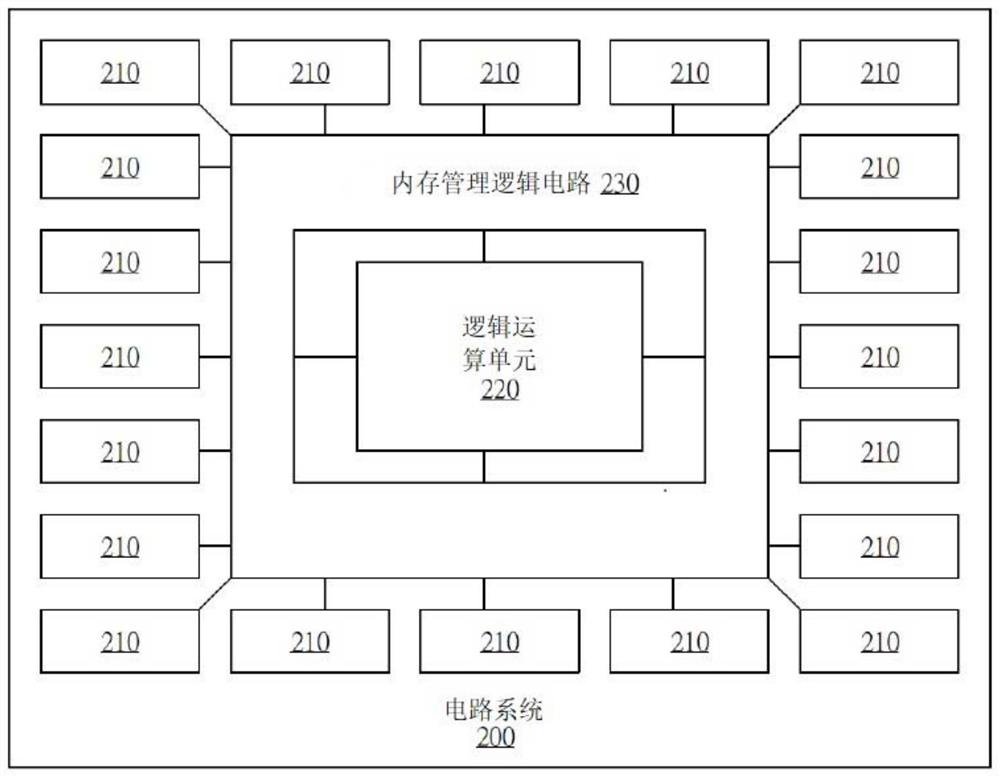

图2为根据本发明一实施例的一电路系统的一方块示意图。

图3为根据本发明一实施例的一电路系统的一方块示意图。

图4为根据本发明一实施例的一电路系统的一方块示意图。

主要组件符号说明:

100 计算器系统

101 中央处理器

110 计算核心

120 内存管理器

130 高速缓存

140 动态随机存取内存

200 电路系统

210 内存电路单元

220 逻辑运算单元

230 内存管理逻辑电路

300 电路系统

310 暂存缓冲器单元

320 第二逻辑运算单元

330 内存管理逻辑电路

331 逻辑运算单元接口

333 排程逻辑电路

335 仲裁逻辑电路

339 内存接口

400 电路系统

410 第一逻辑运算单元

420 交换器电路

【具体实施方式】

本发明将详细描述一些实施例如下。然而,除了所揭露的实施例外,本发明亦可以广泛地运用在其他的实施例施行。本发明的范围并不受这些实施例的限定,乃以权利要求范围为准。而为提供更清楚的描述及使熟悉这项技艺者能理解本发明的发明内容,图示内各部分并没有依照其相对的尺寸而绘图,某些尺寸与其他相关尺度的比例会被突显而显得夸张,且不相关的细节部分亦未完全绘出,以求图示的简洁。此外,本发明的各流程图所示的各个步骤当中,可以插入其他与本发明无关的其他步骤。除非有因果依存关系,本发明也不限定各个步骤的执行顺序。

请参考图2所示,其为根据本发明一实施例的一电路系统200的一方块示意图。电路系统200包含多排内存电路单元210,逻辑运算单元220,以及用于分别连接逻辑运算单元220与多排内存电路单元210的内存管理逻辑电路230。

在一实施例中,电路系统200可以实施在同一芯片上,包含在同一封装体内。在另一实施例中,电路系统200可以实施在多个芯片上,但同样包含在同一封装体内。为了抵抗外界的电磁干扰,封装体可以包含金属外壳或其他屏蔽电磁干扰的措施。在该实施例中,多排内存电路单元210与逻辑运算单元220可以位于不同的芯片上。

在一实施例中,如图2所示,多排内存电路单元210与逻辑运算单元220位于同一芯片,其中逻辑运算单元220被多排内存电路单元210包围在芯片当中。然而,由于绕线的缘故,可能有某些内存电路单元210无法完全包围逻辑运算单元220。在一实施例中,本发明对于包围的定义是:电路系统200中有八成的内存电路单元210较逻辑运算单元220更靠近芯片的边缘。

每一排内存电路单元210包含多个位元,并且具有一组存取端口。该组存取端口包含多个数据存取端口与多个地址存取端口以指定其内含的多个位元。该组存取端口还可以包含指令存取端口,用于对该排内存电路单元210下达读取或写入的指令。该排内存电路单元210也可以通过指令存取端口来回复本身的状态。本发明并不限定有几排内存电路单元210,也不限定每一排内存电路单元210包含多少个位元,也不限定上述组存取端口所包含的数据存取端口、地址存取端口与指令存取端口的个数。

在一实施例中,内存电路单元210可以包含静态随机存取内存(static randomaccess memory,SRAM),例如以金属氧化物半导体场效晶体管(MOSFET)、双极性晶体管(bipolar transistor)等元器件实作的静态随机存取内存。在另一实施例中,内存电路单元210可以包含各种形式的正反器(flip-flop),例如RS正反器、D正反器、JK正反器、T正反器、同步正反器、主从正反器等元器件。在更一实施例中,内存电路单元210可以包含各种闩锁电路(latch),例如RS闩锁、门控D闩锁等。

逻辑运算单元220可以包含逻辑运算与/或数值运算的电路,内含一个缓存器档案,用于暂存逻辑运算与/或数值运算所需的数值。在一实施例中,逻辑运算单元220可以执行逻辑运算以得到一哈希值,哈希值是用于指定存取多排内存电路单元210当中的某一排内存电路单元210当中的部分位元。逻辑运算包含以太币(Ethereum)中计算伪随机数(nonce)的算法。

存取指令是传送至内存管理逻辑电路230。内存管理逻辑电路230是通过被指定的内存电路单元210的该组存取端口对被指定的部分位元进行储存或读取。由于上述的逻辑运算,存取指令的传送与处理均使用同一芯片或同一封装体内部的高速频率信号运行,比起图1所示的现有技术相比,图2所示实施例的内存访问速度要远高于图1范例中对动态随机存取内存140的访问速度。据此,本发明所提供的实施例可以提供无需通过瓶颈就能够在芯片内部高速执行哈希算法的电路系统,进而提高计算的效率。

请参考图3所示,其为根据本发明一实施例的一电路系统300的一方块示意图。电路系统300包含了多排内存电路单元210、一内存管理逻辑电路330,以及多个暂存缓冲器单元310。每一个暂存缓冲器单元310用于分别连接至少一排内存电路单元210与内存管理逻辑电路330,以便暂存自至少一排内存电路单元210所存取的内容。由于在实作上,每一排内存电路单元210与内存管理逻辑电路330的线路并不是等长,所以某些排的内存电路单元210需要对应的暂存缓冲器单元310来暂存内容,以便对应到下一个或下几个频率信号。图3的实施例所包含的多个暂存缓冲器单元310所暂存的时间可以相同,但也可以不同,端赖其所连接的内存电路单元210与内存管理逻辑电路330的线路长度而定。

电路系统300包含了多个第二逻辑运算单元320,分别连接到内存管理逻辑电路330。这些第二逻辑运算单元320的集合可以被视为图2所示的逻辑运算单元220。而前述关于逻辑运算单元220的叙述,可以适用于这些第二逻辑运算单元320。

第二逻辑运算单元320用于执行第二逻辑运算以分别产生一第二哈希值,其中第二哈希值是用于存取多排内存电路单元210当中的某一排内存电路单元210当中的部分位元。在一实施例中,第二逻辑运算包含以太币(Ethereum)中计算伪随机数(nonce)的算法或是其部分。因此,电路系统300可以同时计算多个伪随机数(nonce)。

每一个第二逻辑运算单元320可以具有独特的编号,用于识别第二逻辑运算单元320。在一实施例中,第二逻辑运算单元320的编号也可以用于表示第二逻辑运算单元320的存取指令的优先度。当有两个或以上的第二逻辑运算单元320要对同一排内存电路单元210进行存取时,即发生存取冲突(collision),内存管理逻辑电路330可以根据造成存取冲突的多个第二逻辑运算单元320的编号大小,来决定那一个第二逻辑运算单元320所发出的存取指令具有优先执行的权利。举例来说,可以令编号较大的第二逻辑运算单元320的存取指令优先执行,也可以令编号较小的第二逻辑运算单元320的存取指令优先执行。上述的编号可以是利用硬件决定,也可以利用软件进行设定。本发明并不限定利用软件重新设定各个第二逻辑运算单元320编号的时机与次数。

当这些第二逻辑运算单元320所产生的多个第二哈希值指定存取不同排内存电路单元210的时候,内存管理逻辑电路330可以同时执行多个存取动作,而增进计算效率。在某些实施例中,电路系统300的计算效率可以用每秒执行多少个哈希运算(hash rate persecond)作为指标。当电路系统300具有越多排内存电路单元210时,越不容易发生存取冲突(collision),亦即内存存取的效率就越高,每秒可以执行更多个哈希运算。然而,内存电路单元210的排数越多,其绕线的复杂程度也就随即增加。付出的代价可能是要增加前述的暂存缓冲器单元310数量,以及其所要占用的芯片面积。在一实施例中,第二逻辑运算单元320的数量约为内存电路单元210的排数的6-10倍之间。

图3所示的内存管理逻辑电路330包含一逻辑运算单元接口331,用于分别连接到上述的多个第二逻辑运算单元320,以便接收存取指令与回复存取结果。逻辑运算单元接口331可以包含一交换器电路(crossbar)与/或一多任务器电路(MUX)。

图3所示的内存管理逻辑电路330包含一内存接口339,用于分别连接到上述的多排内存电路单元210,以便储存或提取内存内容。内存接口339可以包含交换器电路(crossbar)与/或多任务器电路(MUX)。

内存管理逻辑电路330可以包含一排程逻辑电路333与一仲裁逻辑电路335。当有多个没有冲突的存取指令进入逻辑运算单元接口331之后,这些存取指令会进入排程逻辑电路333进行处理。在一实施例中,排程逻辑电路333可以包含一或多个先进先出的序列,依照存取指令的先后顺序,排入一或多个序列中进行处理。在另一实施例中,由于这些存取指令没有造成冲突,因此排程逻辑电路333可以利用乱序或是不依照先后顺序(out-of-order)的方式进行处理。

当有冲突的多个存取指令进入仲裁逻辑电路335之后,如前所述,仲裁逻辑电路335可以根据发出这些存取指令的第二逻辑运算单元320的标号进行仲裁,决定哪一个存取指令优先存取冲突的该排内存电路单元210。

排程逻辑电路333与仲裁逻辑电路335当前所决定处理的多个存取指令会同时进入到内存接口339,以便储存或提取内存内容。所提取的内存内容则会反向回到逻辑运算单元接口331。储存或提取内容或许会经过前面所提到的暂存缓冲器单元310。

请参考图4所示,其为根据本发明一实施例的一电路系统400的一方块示意图。与图3所示的电路系统300相比,电路系统400更包含了多个第一逻辑运算单元410与一交换器(crossbar)电路420。电路系统400所包含的其余元器件均和电路系统300相似,故不在此赘叙。

电路系统400的多个第一逻辑运算单元410、多个第二逻辑运算单元320与交换器电路420的集合可以被视为图2所示的逻辑运算单元220。而前述关于逻辑运算单元220的叙述,可以适用于多个第一逻辑运算单元410、多个第二逻辑运算单元320与交换器电路420的集合。

每一个第一逻辑运算单元410用于执行第一逻辑运算,以分别令多个第二逻辑运算单元320其中之一执行第二逻辑运算。在一实施例中,第一逻辑运算与第二逻辑运算各自包含以太币(Ethereum)中计算伪随机数(nonce)的算法的部分。因此,电路系统400可以同时计算多个伪随机数(nonce)。在一实施例中,第二逻辑运算可以是计算伪随机数的算法的DAG page(改良版的DAGGER hashimoto算法)的部分,而第一逻辑运算则是计算伪随机数的算法的其余部分。由于第一逻辑运算所需要的回合次数约为第二逻辑运算所需要回合次数的四分之一,因此第一逻辑运算单元410的数量可以约为第二逻辑运算单元320的四分之一。举例来说,第一逻辑运算需要做一次64回的循环与固定时间长度的运算,其所花的时间约为64个单位时间加上某一常数时间。而第二逻辑运算需要做256回的循环与另一固定时间长度的运算,其所花的时间约为256个单位时间加上另一常数时间。若不计这些固定时间长度的运算,则两者的单位时间约为64:256,亦即1:4。

交换器电路420是用于连接每一个第一逻辑运算单元410与每一个第二逻辑运算单元320,其可以同时允许多对第一逻辑运算单元410与第二逻辑运算单元320的连接。

根据一实施例,本发明提供一种适用于哈希算法的电路系统,包含:多排内存电路单元,每一排内存电路单元均包含多个位元与一组存取端口以存取多个位元的部分,其中每一组存取端口包含多个数据存取端口与多个地址存取端口;逻辑运算单元,用于执行逻辑运算以取得一哈希值,哈希值是用于指定存取多排内存电路单元当中的某一排内存电路单元当中的部分位元;以及内存管理逻辑电路,用于分别连接逻辑运算单元与多排内存电路单元所分别对应的存取端口。

在一实施例中,为了调整不同线路长度所造成的延迟与频率不匹配,电路系统更包含:暂存缓冲器单元,用于分别连接至少一排内存电路单元与内存管理逻辑电路,以便暂存自至少一排内存电路单元所存取的内容。

在一实施例中,为了适应不同种类的同步与异步芯片实作技术,多排内存电路单元包含下列其中一种电路或其任意组合:静态随机存取内存(SRAM);正反器(flip-flop);以及锁存器(latch)。

在一实施例中,为了同时提供多个逻辑运算单元以增进执行效率,其中逻辑运算单元更包含多个第二逻辑运算单元,其中每一个第二逻辑运算单元分别连接至内存管理逻辑电路,并且用于执行第二逻辑运算以分别产生一第二哈希值,其中第二哈希值是用于存取多排内存电路单元当中的某一排内存电路单元当中的部分位元。

在一实施例中,为了同时提供多个逻辑运算单元以增进执行效率,逻辑运算单元更包含多个第一逻辑运算单元,其中每一个第一逻辑运算单元用于执行第一逻辑运算,以分别令多个第二逻辑运算单元其中之一执行第二逻辑运算。在该实施例中,逻辑运算单元更包含一交换器电路(crossbar),用于分别连接多个第二逻辑运算单元与多个第一逻辑运算单元。

在一实施例中,为了替多个不冲突的存取指令进行排程,内存管理逻辑电路更包含先进先出的序列,当有多个第二逻辑运算单元欲存取不同排的内存电路单元时,是依照存取的先后顺序,排入序列依序进行处理。

在一实施例中,为了替多个不冲突的存取指令进行排程,当有多个第二逻辑运算单元欲存取不同排的内存电路单元时,内存管理逻辑电路是不依照存取的先后顺序(out-of-order)的方式进行处理。

在一实施例中,为了替冲突的存取指令进行排程,内存管理逻辑电路更包含仲裁逻辑电路,当有多个第二逻辑运算单元产生欲存取相同排的内存电路单元时,仲裁逻辑电路是依照多个第二逻辑运算单元所各自对应的编号的优先级进行处理。

在一实施例中,逻辑运算包含以太币(Ethereum)中计算伪随机数(nonce)的算法。

在一实施例中,为了方便安排绕线与尽可能让线路的长度一致,多排内存电路单元与逻辑运算单元位于同一芯片,其中逻辑运算单元被多排内存电路单元包围在芯片当中。

根据本发明所提供的电路系统,可以无需通过传统的内存存取瓶颈就能够在芯片内部高速执行哈希算法,进而提高计算的效率。

虽然本发明的实施例揭露如上所述,然并非用以限定本发明,任何熟习相关技艺者,在不脱离本发明的精神和范围内,举凡依本发明权利要求所述的形状、构造、特征、方法及数量当可做些许的变更,因此本发明的专利保护范围须视本说明书所附的权利要求范围所界定者为准。

- 适用于哈希算法的电路系统

- 一种适用于普速铁路的发送器1+1冗余轨道电路系统