形成贯穿衬底通孔的方法以及包括贯穿衬底通孔的半导体器件

文献发布时间:2023-06-19 11:32:36

贯穿衬底通孔是贯穿半导体衬底的电互连。其包括穿透衬底的导通孔和布置在导通孔中的金属化部。

能够通过首先在衬底的主表面上方的介电材料中形成金属层来制造贯穿衬底通孔。覆盖金属层的不同含金属的材料的层改善了介电材料的粘附力。然后从相对的表面,通过衬底,蚀刻导通孔,直到到达介电材料。作为绝缘部提供的氧化硅层被布置在导通孔的侧壁和底部上。通过各向异性蚀刻步骤从导通孔的底部去除氧化硅和介电材料,以便氧化硅保留在侧壁上以覆盖半导体材料,并且在底部暴露金属层的接触区域。在导通孔中施加金属化部,以便其与金属层接触并形成电互连。

US 2015/0102497 A1公开了一种制造包括贯穿硅通孔的集成电路器件的方法。着落垫由Cu、W、Ta、Ti、Co、Mn、Al或其组合的金属层以及由Ta、Ti、TaN、TiN、AlN、WN或其组合的阻挡膜形成。

本发明的目的是提供一种形成贯穿衬底通孔的方法,该方法改善了蚀刻和绝缘步骤的应用,以及提供一种具有贯穿衬底通孔的半导体器件,该通孔与嵌入电介质中的金属层可靠地接触。

该目的通过根据权利要求1的形成贯穿衬底通孔的方法以及根据权利要求12的半导体器件来实现。该方法的变型和其他实施例从从属权利要求得出。

形成贯穿衬底通孔的方法包括提供:具有布置在衬底上的电介质的衬底;嵌入在该电介质中的金属层;以及布置在该金属层上的含金属层,该含金属层设置在衬底与金属层之间。在金属层上方形成穿透衬底的导通孔。在导通孔中施加绝缘层并且从金属层的接触区域上方将其去除。在导通孔中施加金属化部,该金属化部在接触区域中与金属层接触并通过绝缘层与衬底绝缘。在施加金属化部之前将含金属层从接触区域完全去除。

在该方法的变型中,在施加绝缘层并将其从接触区域上方去除之后,从接触区域上方去除电介质。

在该方法的另一变型中,在施加绝缘层之前,从含金属层上方去除电介质,以便导通孔到达含金属层,将绝缘层施加在含金属层上,并且将绝缘层从接触区域上方去除,使得含金属层的一部分留在金属层与绝缘层之间。

在该方法的另一变型中,在施加绝缘层之前,从金属层上方去除电介质和含金属层,以便导通孔到达金属层,在导通孔的内部暴露金属层的接触区域,并且将绝缘层施加在金属层上。从接触区域上方去除绝缘层之后,施加金属化部以与接触区域电接触并且通过绝缘层与含金属层绝缘。

在该方法的另一变型中,通过蚀刻以及通过使用相对于含金属层非选择性的配方,从金属层上方去除电介质。

在该方法的另一变型中,通过蚀刻从金属层上方去除电介质和绝缘层,并且在这些蚀刻步骤的每一个中使用相同的蚀刻配方。

在该方法的另一变型中,在形成导通孔之前施加具有开口的掩模。通过开口蚀刻导通孔,并且在施加绝缘层之前去除掩模。

金属层可以包括与含金属层的材料不同的材料。金属层可以例如是铝。含金属层可以包括例如钛或铝。含金属层还可以包括氮化物。

半导体器件包括:具有贯穿衬底通孔的衬底;贯穿衬底通孔的导通孔;在导通孔中的绝缘层;贯穿衬底通孔的金属化部,所述绝缘层使金属化部与衬底绝缘;衬底上方的金属层,金属化部与金属层接触;金属层上的含金属层,含金属层布置在衬底与金属层之间,含金属层包括与金属层的材料不同的材料,并且金属化部与金属层的接触区域接触。

在半导体器件的一实施例中,含金属层的一部分被布置在金属层与绝缘层之间。

在半导体器件的另一实施例中,金属化部通过绝缘层与含金属层完全分离。

在半导体器件的另一实施例中,含金属层包括钛或铝。

在半导体器件的另一实施例中,含金属层包括氮化物。

下面结合附图对该方法和器件的示例进行详细说明。

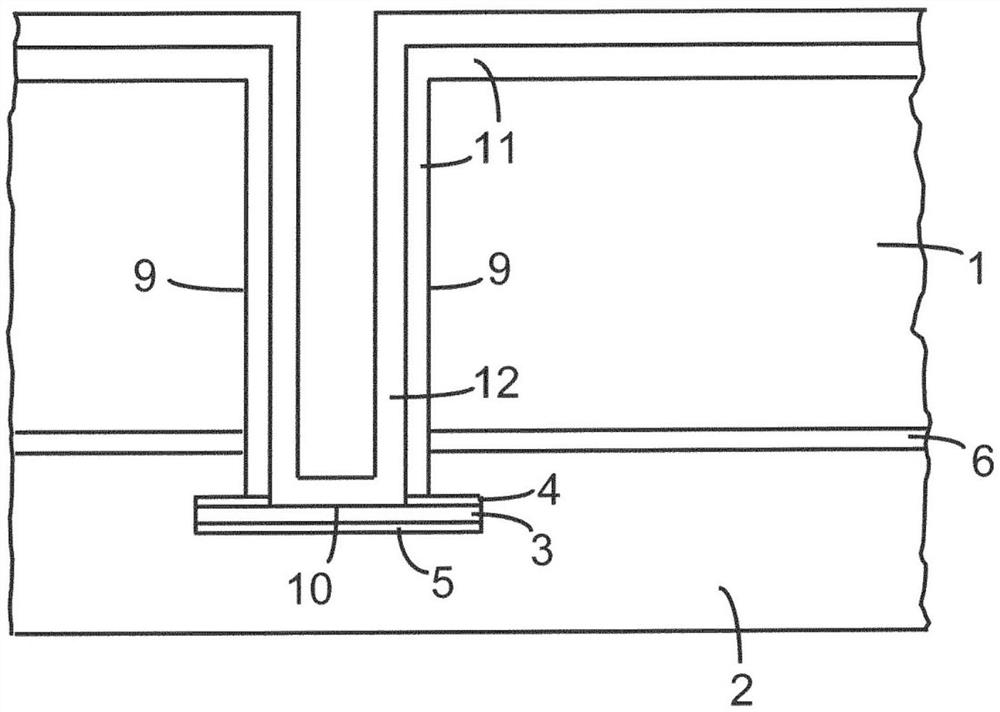

图1是在蚀刻导通孔之前的中间产物的横截面;

图2是根据图1的在蚀刻导通孔之后的横截面;

图3是根据图2的在施加绝缘层之后的横截面;

图4是根据图3的从导通孔的底部去除绝缘层之后的横截面;

图5是根据图4的在施加金属化部之后的横截面;

图6是根据图5的在施加顶部金属之后的横截面;

图7是在蚀刻导通孔之前的替代的方法的中间产物的横截面;

图8是根据图7的在蚀刻导通孔之后的横截面;

图9是根据图8的在施加绝缘层之后的横截面;

图10是根据图9的从导通孔的底部去除绝缘层之后的横截面;

图11是根据图10的在施加金属化部之后的横截面;

图12是根据图11的在施加顶部金属之后的横截面;

图13是根据图2的在蚀刻导通孔之后的替代的方法的截面图;

图14是根据图13的在施加绝缘层之后的横截面;

图15是根据图14的从导通孔的底部去除绝缘层之后的横截面;

图16是根据图15的在施加金属化部之后的横截面;以及

图17是根据图16的在施加顶部金属之后的横截面。

图1是可以通过该方法获得的中间产物的示例的横截面。半导体材料的衬底1,例如可以是硅,其设置有电介质2,该电介质尤其可以是金属间电介质,例如氧化硅。与电介质2不同的另一电介质6可以可选地布置在衬底1与电介质2之间。

金属层3嵌入在电介质2中。金属层3尤其可以是布线的一部分,例如布线可以包括多个金属层。这种由CMOS技术本身已知的布线的细节与本发明无关,并且在附图中未示出。金属层3尤其可以例如是铝。

含金属层4布置在金属层3的面对衬底1的主表面上。可选的另一含金属层5可以布置在金属层3的背离衬底1的主表面上。含金属层4和/或另一含金属层5尤其可以包括钛或铝。特别地,含金属层4和/或另一含金属层5例如可以包括氮化钛或氮化铝。

嵌入金属间电介质中的布线的金属层通常设置有氮化钛的覆盖物,特别地是在CMOS技术中,以增强电介质材料对金属层的粘附力。可以将金属层3、含金属层4和另一含金属层5施加为这种布线的一部分。

将例如可以是抗蚀剂掩模或硬掩模的掩模7施加在衬底1的与电介质2相对的背面上。掩模7具有与金属层3相对的开口8,并且位于要形成贯穿衬底通孔的区域的上方。

图2是根据图1的横截面,并且示出了在形成导通孔9之后的另一中间产物。在衬底1中蚀刻通过掩膜7的开口8的导通孔9。继续蚀刻通过电介质2、6直到到达含金属层4。当蚀刻电介质2、6时掩模7仍然存在。含金属层4可以用作终止电介质2、6的蚀刻的蚀刻停止层。

图3是根据图2的横截面,并且示出了在施加绝缘层11之后的另一中间产物。将例如可以是氧化硅的绝缘层11设置作为绝缘部,其位于衬底1的半导体材料与随后将被施加以形成贯穿衬底通孔的导电部分的金属化部之间。可以例如通过沉积来施加绝缘层11。绝缘层11的部分通常也可以覆盖金属层3的接触区域10和衬底1的在导通孔9外部的背面。

图4是根据图3的横截面,并且示出了在部分去除绝缘层11之后的另一中间产物。施加由蚀刻间隔物而本身已知的各向异性蚀刻工艺,从导通孔9的底部处去除绝缘层11,在该位置暴露含金属层4。含金属层4也被部分地去除,以便暴露金属层3的接触区域10。绝缘层11的被施加在导通孔9外部的部分可以完全去除。替代地,如图4通过示例所示,衬底1的背面仍然可以由绝缘层11覆盖。

图5是根据图4的横截面,并且示出了在施加金属化部12之后的另一中间产物,该金属化部被设置用于贯穿衬底通孔的导电部分。金属化部12能够被施加为层,尤其是保形层。该金属化部被施加在金属层3的接触区域10上,以便其与接触区域10电接触。因此形成了从金属层3到衬底1的背面的电连接。金属化部12可以包括多于一种金属,并且尤其可以施加为金属层列,该金属层列例如可以包括钛层和钨层。金属化部12与在绝缘层11的底部下方的含金属层4的保留部分接触。

图6是根据图5的在另外的工艺步骤之后的横截面。可选地将金属化部12从衬底1的背面去除,并且可以将顶部金属13施加在背面上并与金属化部12接触。以这种方式,例如可以在背面上形成再分布层。顶部金属13可以覆盖有覆盖层14,该覆盖层例如可以是另一电介质。覆盖层14中的至少一个开口可以提供通向顶部金属13的通路,以施加例如块形连接或类似的外部电端子。可以形成在背面上的电导体的细节与本发明无关并且未在图6中示出。

图7至图12是根据图1至图6的方法的变型的横截面。图7示出了与图1中所示的中间产物相对应的中间产物。相应的元件用相同的附图标记表示。如结合图1所描述的,例如,诸如硅的半导体材料的衬底1设置有电介质2以及嵌入在电介质2中的金属层3。含金属层4布置在金属层3的面向衬底1的表面上,并且可以将可选的另一含金属层5布置在金属层3的相对表面上。含金属层4和/或另一含金属层5尤其可以包括钛或铝,特别是例如氮化钛或氮化铝。

例如可以是抗蚀剂掩模或硬掩模的掩模7被施加在衬底1的与电介质2相对的背面上。掩模7具有与金属层3相对的开口8,并且位于要形成贯穿衬底通孔的区域的上方。

图8是根据图7的横截面,并且示出了在形成导通孔9之后的另一中间产物。在衬底1中蚀刻通过掩模7的开口8的导通孔9。该方法的这种变型的根本特征是继续蚀刻通过电介质2、6直到到达金属层3。当蚀刻电介质2、6时掩模7仍然存在。由于掩模7的材料改变了化学环境,当掩模7仍然存在时,可以更容易地去除在蚀刻过程中形成的聚合物。

含金属层4可以用作终止电介质2、6的蚀刻的蚀刻停止层。替代地,能够继续蚀刻以到达含金属层4。这意味着不必相对于含金属层4选择蚀刻工艺。因此能够从低聚合度的角度来选择蚀刻配方。

在任何情况下,从导通孔9的底部去除含金属层4,以暴露金属层3的表面的接触区域10。在该步骤中也可以去除金属层3的一些材料,而不会对另外的工艺步骤,特别是对稍后在金属层3上形成的电接触部产生不利地影响。

图9是根据图8的横截面,并且示出了在施加绝缘层11之后的另一中间产物。将例如可以是氧化硅的绝缘层11设置为绝缘部,其位于衬底1的半导体材料与随后将被施加以形成贯穿衬底通孔的导电部分的金属化部之间。可以例如通过沉积来施加绝缘层11。绝缘层11的部分通常也可以覆盖金属层3的接触区域10和衬底1的在导通孔9外部的背面。

图10是根据图9的横截面,并且示出了在部分去除绝缘层11之后的另一中间产物。施加各向异性蚀刻工艺,从导通孔9的底部去除绝缘层11,以便再次暴露金属层3的接触区域10。能够再次从低聚合度的角度选择蚀刻配方。绝缘层11的被施加在导通孔9外部的部分可以完全去除。替代地,如图10通过示例所示,衬底1的背面仍然可以由绝缘层11覆盖。

图11是根据图10的横截面,并且示出了在施加金属化部12之后的另一中间产物,该金属化部被设置用于贯穿衬底通孔的导电部分。金属化部12能够以如上所述的方式施加,尤其可以将其施加为金属层列,该金属层列例如可以包括钛层和钨层。在该方法的变型中,金属化部12通过绝缘层11的底部与含金属层4的保留部分分离。

图12是根据图11的在另外的工艺步骤之后的横截面。如上所述,可选地将金属化部12从衬底1的背面去除,并且顶部金属13可以被施加在背面上与金属化部12接触,并且设置有覆盖层14。

根据图7至图12的方法的变型具有的优点是,金属层3能够用作蚀刻停止层,并且在施加绝缘层11之前从接触区域10去除含金属层4。因此,在蚀刻之后所需的湿法清洗步骤期间,不存在含金属层4变得多孔的风险。以这种方式防止了所施加的清洗剂渗透和侵蚀金属层3的表面。因此,即使将含金属层4制成例如CMOS器件的布线所需的薄度,接触区域10也足够光滑,以用于施加金属化部12。能够对电介质2、6的蚀刻以及绝缘层11的蚀刻单独地优化。能够选择低聚合度的蚀刻配方以有助于清洗步骤。

图13至图17是根据图2至图6的用于方法的另一变型的横截面,其从根据图1的中间产物开始。相应的元件用相同的附图标记表示。

图13示出了衬底1被蚀刻直到到达另一电介质6。然后如图14所示,施加绝缘层11。然后执行各向异性蚀刻步骤,通过绝缘层11的底部、另一电介质6、电介质2和含金属层4,该步骤可以是反应离子蚀刻。蚀刻的结果在图15中示出。含金属层4的一部分保留在金属层3与绝缘体之间,绝缘体包括电介质2的部分和另一电介质6的部分以及绝缘层11。

在该方法的这种变型中,绝缘部的下部不是由绝缘层11形成的,而是由电介质2的部分和另一电介质6的部分形成。这具有的优点是,含金属层4的最终保留部分始终由绝缘材料覆盖。该方法的这种变型的其他步骤与以上结合图5和图6描述的方法步骤类似,并且在图16和图17中示出。

附图标记说明

1 衬底

2 电介质

3 金属层

4 含金属层

5 另一含金属层

6 另一电介质

7 掩膜

8 开口

9 导通孔

10 接触区域

11 绝缘层

12 金属化部

13 顶部金属

14 覆盖层

- 形成贯穿衬底通孔的方法以及包括贯穿衬底通孔的半导体器件

- 带有贯穿衬底通孔的半导体器件