半导体器件的制备方法和半导体器件

文献发布时间:2023-06-19 11:32:36

技术领域

本发明属于半导体制作技术领域,尤其涉及一种半导体器件的制备方法和半导体器件。

背景技术

在目前的BCD(双极性CMOS-DMOS)工艺中,与CMOS(互补金属氧化物半导体)工艺的兼容是一个平衡的过程。

标准180nm(纳米)工艺中,标准BCD工艺和标准CMOS工艺中栅氧的指标对比如下表:

Vgs为栅源电压,Vds为漏源电压,电压单位为V(伏特),厚度单位为A(埃)。

通常情况下,Vgs越大,导通电阻越小,导通电流越大,寄生电容越小;反之亦然。因此,与标准BCD工艺相比,标准CMOS工艺的Vgs小,导通电阻大,导通电流小,寄生电容大。

发明内容

本发明要解决的技术问题是为了克服现有技术中存在的CMOS的导通电阻大,导通电流小,寄生电容大,电气性能比DENMOS差的缺陷,提供一种半导体器件的制备方法和半导体器件。

本发明是通过下述技术方案来解决上述技术问题:

本发明提供一种半导体器件的制备方法,包括以下步骤:

提供一衬底;

所述衬底上形成栅极;

使用所述栅极作为阻挡层并以垂直方向为基准进行第一预设角度的硼离子注入,以在所述栅极的底部形成沟道;

使用所述栅极作为阻挡层并以垂直方向为基准进行第二预设角度的磷离子注入以形成Halo-implant(晕环离子注入)区域,所述Halo-implant区域与所述栅极相邻;

所述Halo-implant区域内进行NPS(N型源漏注入)注入,以形成接触区域的欧姆接触,所述接触区域为NPS注入区域与所述Halo-implant区域的接触区域,所述NPS注入区域至所述栅极之间形成硅化金属阻挡区。

较佳地,对所述衬底进行浅沟槽隔离,以在所述衬底的两侧形成梯形沟槽;

注入离子,以在所述衬底上形成HVDNW(High voltage Deep N Well,深N型阱)阱;

注入离子,以在所述HVDNW阱上形成IOPW(Input Output P Well,输入输出P型阱)阱。

较佳地,所述使用所述栅极作为阻挡层并以垂直方向为基准进行第一预设角度的硼离子注入,以在所述栅极的底部形成沟道的步骤中,所述第一预设角度的设定范围为30度~40度,所述硼离子的浓度范围为5e13/cm

较佳地,所述使用所述栅极作为阻挡层并以垂直方向为基准进行第二预设角度的磷离子注入以形成Halo-implant区域的步骤中,所述第二预设角度的设定范围为6度~8度。

较佳地,在所述离子注入,以在所述衬底上形成HVDNW阱的步骤中,以不低于500Kev(千电子伏特)的条件进行离子注入;和/或,

在所述注入离子,以在所述HVDNW阱上形成IOPW阱的步骤中,以不低于500Kev的条件进行离子注入。

较佳地,所述制备方法应用于BCD工艺。

较佳地,所述BCD工艺包括180nm、130nm、65nm、40nm工艺中的任意一种或多种。

较佳地,所述半导体器件为DENMOS(n沟道漏极延伸金属氧化物半导体)。

较佳地,所述衬底为P型衬底;和/或,

所述DENMOS的工作电压范围为4V~6V。

本发明还提供一种半导体器件,所述半导体器件通过前述的半导体器件的制备方法制备。

本发明的积极进步效果在于:通过所述半导体器件的制备方法制作出的DENMOS可以代替CMOS,同时降低了导通电阻(Rdson),提高了驱动门限(Vth),在不改变Vgs的情况下,提高了电流负载能力,降低了过驱动电压(Vod)。

附图说明

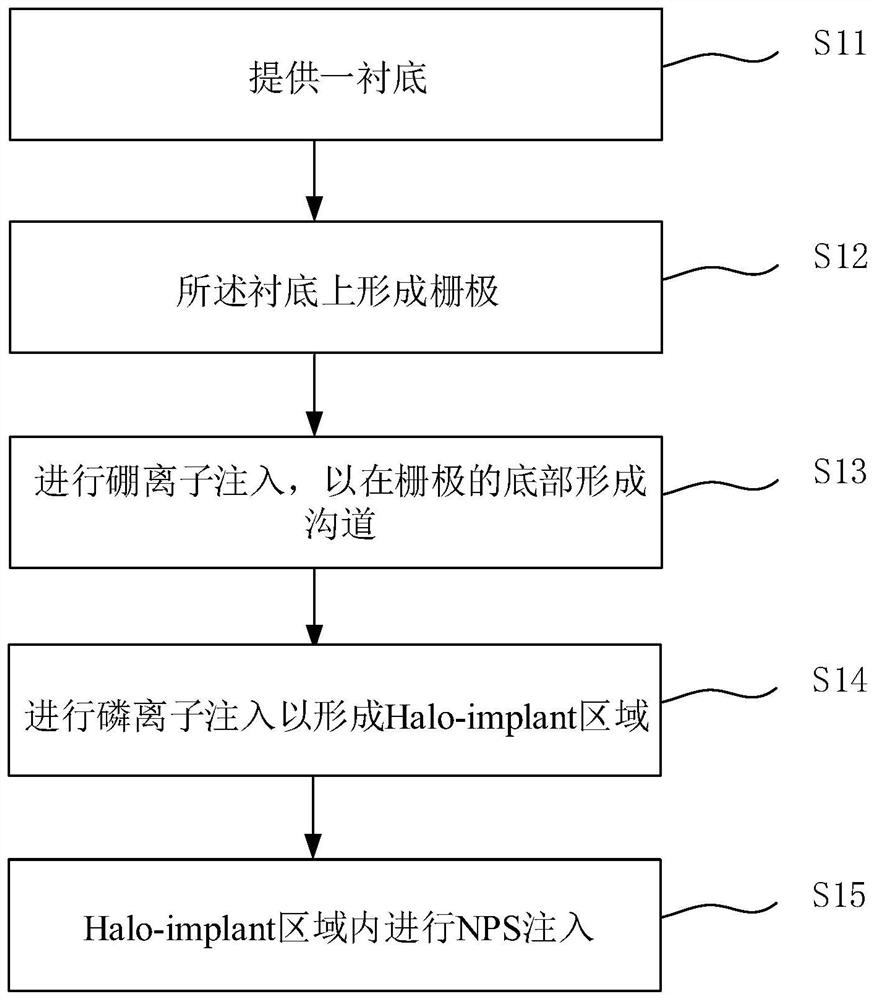

图1为本发明的实施例1的半导体器件的制备方法的流程示意图。

图2为本发明的实施例1的半导体器件的制备方法的半导体器件的截面示意图。

图3为本发明的实施例1的半导体器件的制备方法的磷离子注入步骤后半导体器件的截面示意图。

图4为本发明的实施例1的半导体器件的制备方法的NPS注入步骤后半导体器件的截面示意图。

图5为本发明的实施例1的半导体器件的制备方法的标注电压后半导体器件的截面示意图。

图6为本发明的实施例2的半导体器件的制备方法的半导体器件的截面示意图。

具体实施方式

下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

实施例1

本实施例提供一种半导体器件的制备方法。参照图1,所述制备方法包括以下步骤:

步骤S11、参照图2,提供一衬底1;

衬底1优选为P型衬底,但并不仅限于此类型的衬底,可以根据需要选择衬底的类型;

步骤S12、衬底1上形成栅极2;

步骤S13、进行硼离子注入,以在栅极2的底部形成沟道;

使用栅极2作为阻挡层并以垂直方向为基准进行第一预设角度的硼离子注入,以在栅极2的底部形成沟道;

步骤S14、参照图3,进行磷离子注入以形成Halo-implant区域3;

使用栅极2作为阻挡层并以垂直方向为基准进行第二预设角度的磷离子注入以形成Halo-implant区域3,所述Halo-implant区域3与栅极2相邻;

步骤S15、参照图4,Halo-implant区域3内进行NPS注入;

Halo-implant区域3内进行NPS注入,以形成接触区域的欧姆接触,所述接触区域为NPS注入区域4与Halo-implant区域3的接触区域,NPS注入区域4至所述栅极2之间形成硅化金属阻挡区。

本实施例中,利用CMOS标准工艺中的I/O(输入/输出)栅氧构建低压5.0V的半导体器件,所述半导体器件为DENMOS。DENMOS通常用于电源管理,如开关等,具有较大的电流负载能力及低压扩展能力,同时导通电阻低,漏电小,电气性能比CMOS好。本实施例的DENMOS中,栅氧5在栅极2的底部,栅氧5的厚度为65A,比标准BCD工艺中的栅氧的厚度小。

参照图5,半导体器件的Vds为5.0V,Vgs为3.3V,与标准CMOS工艺中相应指标相比,Vds更大,Vgs没有改变。

参见下表,与标准CMOS的参数相比,本实施例中半导体器件的驱动门限(Vth)更大,导通电阻(Rdson)更小,击穿电压(Bvoff)不变,整体上电气性能更好。

本实施例通过所述半导体器件的制备方法制作出的DENMOS可以代替CMOS,同时降低了导通电阻(Rdson),提高了驱动门限(Vth),在不改变Vgs的情况下,提高了电流负载能力,降低了过驱动电压(Vod)。

实施例2

本实施例的半导体器件的制备方法是在实施例1的基础上进一步改进,具体地:

参照图6,在步骤S12和步骤S13之间,包括以下步骤:

步骤S16、对衬底1进行浅沟槽隔离,以在衬底1的两侧形成梯形沟槽6;

步骤S17、注入离子,以在衬底1上形成HVDNW阱7;

以不低于500Kev的条件进行离子注入;

步骤S18、注入离子,以在HVDNW阱7上形成IOPW阱8;

以不低于500Kev的条件进行离子注入。

步骤S13中,所述第一预设角度的设定范围为30度~40度,所述硼离子的浓度范围为5e13/cm

但并不仅限于此第一预设角度的设定范围或硼离子的浓度范围,可以根据需要设定第一预设角度的设定范围和/或硼离子的浓度范围。

步骤S14中,所述第二预设角度的设定范围为6度~8度,优选为7度;

但并不仅限于此第二预设角度的设定范围,可以根据需要设定第二预设角度的设定范围。

本实施例的半导体制备方法制作出的DENMOS的工作电压范围为4V~6V,但并不仅限于此工作电压范围,可以根据需要调整工作电压范围。

本实施例的半导体制备方法应用于BCD工艺。所述BCD工艺包括180nm、130nm、65nm、40nm工艺中的任意一种或多种,进一步降低了Rdson,提高了Vth,在不改变Vgs的情况下,进一步提高了电流负载能力,降低了Vod,拓宽了半导体器件的制备方法的适用范围。

本实施例通过所述半导体器件的制备方法制作出的DENMOS可以代替CMOS,同时进一步降低了Rdson,提高了Vth,在不改变Vgs的情况下,进一步提高了电流负载能力,降低了Vod,拓宽了半导体器件的制备方法的适用范围。

实施例3

本实施例提供一种半导体器件,通过包括实施例1或实施例2中的任意一个实施例中的半导体器件的制备方法制备。

本实施例制作出的半导体器件DENMOS可以代替CMOS,同时进一步降低了Rdson,提高了Vth,在不改变Vgs的情况下,进一步提高了电流负载能力,降低了Vod,拓宽了半导体器件的适用范围。

虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置

- 半导体器件的制造方法、半导体器件的制造装置、半导体器件、半导体器件的制造程序、半导体用处理剂以及转印用部件