一种基于等价取模测试的高级综合工具缺陷检测方法

文献发布时间:2023-06-19 11:32:36

技术领域

本发明属于检测技术以及软件测试技术领域,尤其涉及一种基于等价取模测试的高级综合工具缺陷检测方法。

背景技术

近年来,随着数字化、网络化和智能化的发展,FPGA(Field Programmable GateArray)的应用领域得到快速扩张。FPGA作为通信、航天、军工等领域的关键核心器件,是保障国家战略安全的重要支撑基础。因此,高效完成FPGA设计开发工作至关重要。

在FPGA设计开发过程中,高级综合(High-level synthesis,HLS)技术至关重要。高级综合技术是将电路设计规范的算法级或行为级描述在一定的约束条件下转化为电路结构描述的方法和过程。高级综合设计过程较传统的RTL(Register Transfer Level)设计过程,降低了FPGA开发人员的开发成本,使得不精通微体系结构和数字电路的软件或者算法工程师能够高效地完成FPGA设计工作,提高了FPGA设计开发工作的效率。高级综合工具则在高级综合设计过程起到了重要的支撑作用,高级综合工具可以将高级语言编写的算法代码(如C/C++代码)转为硬件描述语言(Hardware Description Language,HDL)代码,例如Verilog代码、VHDL代码等。高级综合工具能否正确地运行,影响着FPGA设计的准确性。现有的一些发明专利中,如实现SystemC验证的方法和验证平台组件架构(专利申请号:202011129206.6)通过TLI接口实现待验证SystemC设计与已有VerilogRTL验证平台的连接,以完成SystemC验证工作,进而保证最终电路的正确性,而此方法未针对由于高级综合工具的缺陷所导致的电路设计缺陷进行检验。又如一种支持EDA软件的自动化测试并记录的方法及系统(专利号:CN202010130642.9)主要针对于FPGA逻辑综合软件进行测试。在FPGA设计过程中,FPGA逻辑综合是高级综合完成之后的设计过程,高级综合的输出可作为FPGA逻辑综合的输入。针对于FPGA逻辑综合软件的测试,仍无法保证经过高级综合工具处理后的FPGA设计的正确性。综合上述现有发明专利情况,可发现鲜有针对于高级综合工具进行缺陷检测的发明专利。目前,主流的商用高级综合工具有VivadoHLS、IntelHLSCompiler等等,开源高级综合工具有LegUp、Bambu等等,这些工具仍在不断地迭代以修补被遗漏的缺陷。因此,对于高级综合工具进行严格的测试工作十分的急迫且必要。

等价取模测试(Equivalence Modulo Inputs)方法在编译器测试领域起到了举足轻重的作用。等价取模测试通过构建变异程序,比较种子程序与变异程序在相同测试输入下是否有相同的输出来发现编译器存在的缺陷。对于高级综合工具来说,其输入是高级语言代码,如C/C++代码,其输出则是HDL代码,例如Verilog、VHDL等代码。随机生成的高级语言代码作为测试用例,产生的有效测试用例数量较少,而等价取模测试在种子程序中删除未执行代码或插入代码的变异操作产生的测试用例数量较少,依赖于种子程序的数量,也较难构建出可供高级综合工具可优化的测试用例,造成对于高级综合工具测试效率低下。那么如何高效产生高级综合工具测试用例是一个急需解决的问题。同时,由于高级综合工具的输出是HDL代码,如何判断测试输出结果的正确性,进而判断高级综合工具是否存在缺陷,这也是一个亟待解决的问题。

发明内容

本发明的目的在于提供一种基于等价取模测试的高级综合工具缺陷检测方法,以解决在测试高级综合工具过程中有效测试用例产生以及测试输出结果验证等问题。本发明采用了等价取模测试思路,但针对于高级综合工具特点,在等价取模测试在种子代码中删除未执行代码或插入代码的变异操作基础上,增加了对种子代码进行转换的变异操作,并使用仿真器模拟仿真种子代码和变异后代码被待测试高级综合工具综合后所得到的两个HDL代码,比较两个HDL代码是否有相同的仿真输出结果来判断待测试高级综合工具是否存在缺陷。

本发明的技术方案:

一种基于等价取模测试的高级综合工具缺陷检测方法,具体步骤如下:

步骤1:搜集已有C语言测试用例程序,构建测试用例种子池;

使用爬虫技术,从AnghaBench库和CHStoneHLS用例库中获取测试用例程序,过滤掉无效的程序,构建测试用例种子池。

步骤2:检测是否达到测试次数;若未达到,则从步骤1所构建的种子池中随机选取程序文件作为测试用例种子P,并依据测试用例种子生成相应的TestBench文件;若已达到,则停止测试。

其中,TestBench文件包含测试输入、待测设计和测试输出;测试输入为待测模块提供输入数据,待测设计则为待测试的模块,测试输出为待测试模块在当前测试输入下的输出结果。

步骤3:脚本生成程序根据种子代码P以及TestBench文件所存储的位置情况生成并存储TCL(Tool Command Language)脚本,由脚本执行程序通过终端命令行调用待测试的高级综合工具根据TCL脚本对测试用例种子P进行高级综合,以获取到HDL代码HP;

具体为:首先,脚本生成程序根据种子代码P以及TestBench文件所存储的位置生成并存储TCL脚本,以通过TCL脚本为待测试高级综合工具指定新工程名称、测试用例种子P以及TestBench文件、设置顶层函数、设置解决方案名称、定义技术和时钟速率、指定综合过程、设置优化命令、运行待测试高级综合工具进行综合;然后,由脚本执行程序通过Linux终端调用待测试高级综合工具执行TCL脚本进行高级综合,以获取到HDL代码HP。

步骤4:使用高级语言编译器和数字电路仿真模拟器进行协同仿真,在相同TestBench下,获取并保存P的覆盖率C、P的输出结果HLO以及HP的输出结果O;

具体为:使用高级语言编译器编译运行程序P,利用数字电路仿真模拟器对程序HP进行模拟,使用TestBench测试程序P,使用被高级综合工具综合后的TestBench文件测试程序HP,获取并保存P的覆盖率信息C、P的输出结果HLO以及HP的输出结果O。

步骤5:检测测试用例种子P以及高级综合后得到的代码HP是否通过仿真;

具体为:对比步骤4中对于相同的TestBench下,P的输出结果HLO与HP输出结果O;如果两者一致则表示通过仿真,继续进行后续测试步骤;如果两者不一致,则表示未通过仿真,则保存P、TestBench、HP、HLO、O以及相应的TCL文件,生成并存储Bug报告,测试次数增加1,跳转至步骤2继续执行;若通过仿真,则继续执行下一测试步骤;

步骤6:检测测试用例种子P是否可变异;

具体为:检测种子程序已经变异次数,若变异次数已经超过设定值,则不可再变异,测试次数增加1,跳至步骤2继续执行;若未超过,则继续进行后续测试。

步骤7:根据步骤4中获取到的测试用例种子程序P的覆盖率信息C,代码变异程序对测试用例种子P进行代码删除、插入、转换等变异操作,获取到变异后新的测试用例P′;

其中,代码删除是删除测试用例种子代码中没有被TestBench测试所覆盖的代码,代码插入是在测试用例种子代码局部插入不影响程序输出且符合电路设计规范的代码,代码转换则是根据待测工具综合过程中可选的功能,对测试用例种子代码中的for循环进行合并、数据流化、并行化等操作,对数组进行分割、映射以及重组等操作,对函数进行内联、重组等操作。

步骤8:脚本修改程序修改原有TCL脚本并另存为新的TCL脚本,脚本执行程序通过终端命令行调用待测试的高级综合工具根据新的TCL脚本对步骤7中所得到的变异后的测试用例P′进行高级综合,以获取到HDL代码HP′;

具体为:首先,脚本修改程序获取到与种子代码所对应的原有TCL文件,修改其中的工程名称、测试用例以及解决方案名称,使新的TCL文件与变异后的测试用例P′所对应,并将修改后的TCL文件另存为新的TCL文件。然后,由脚本执行程序通过Linux终端命令行调用待测试的高级综合工具根据新的TCL脚本对步骤7中所得到的变异后的测试用例P′进行高级综合,以获取到HDL代码HP′;

步骤9:使用高级语言编译器和数字电路仿真模拟器对P′与HP′进行协同仿真,使用步骤4中的TestBench,获取P′的输出HLO′和HP′的输出O′;

具体为:使用高级语言编译器编译运行程序P′,利用数字电路仿真模拟器对程序HP′进行模拟,使用步骤4中的TestBench测试P′,使用被高级综合工具综合后的TestBench文件测试HP′,获取程序P′的输出HLO′和程序HP′的输出O′。

步骤10:检测步骤4中的结果O与步骤9中的结果O′是否相同;若结果不同则保存P′、HLO′、TestBench、HP′、O′以及相应的TCL文件,生成并存储Bug报告,变异次数增加1,跳转至步骤6继续执行;若结果相同,则直接使变异次数增加1,跳转至步骤6继续执行。

本发明的有益效果:本发明方法能够产生有效的高级综合工具测试的测试用例,能够有效检测高级综合工具中存在的缺陷,并能够自动化生成Bug报告,以供开发人员快速修复缺陷。

附图说明

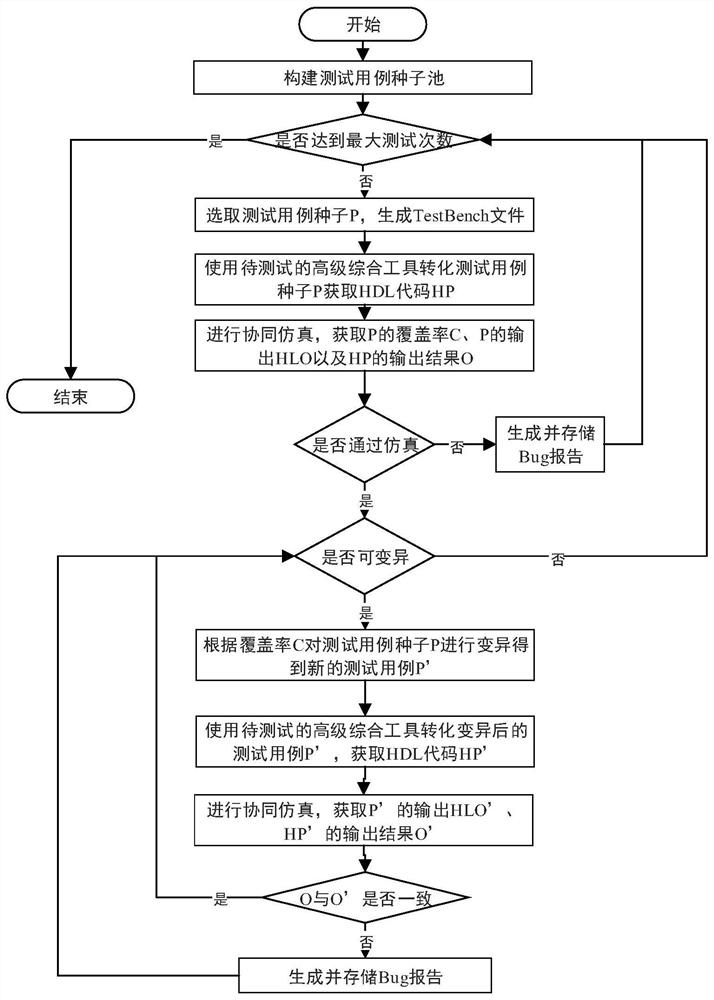

图1是本发明的一种基于等价取模测试的高级综合工具缺陷检测方法工作流程示意图。

具体实施方式

以下结合附图、技术方案以及实施例对本发明方法进行详细说明。

本实施例中,本发明的方法部署在一台Linux服务器上,服务器具体配置如表1所示。根据实验需求安装对应的GCC编译器、Iverilog电路仿真模拟器等工具软件以及待测试软件Xilinx Vivado HLSv2019.2,并对Xilinx Vivado HLSv2019.2进行测试。本发明方法由构建测试用例种子池、代码变异、脚本处理(生成与修改)与执行、协同仿真模拟等程序构成。

表1:Linux服务器配置信息表

如图1所示,本发明的一种基于等价取模测试的高级综合工具缺陷检测方法按如下流程进行。构建测试用例种子池,选择测试用例种子,进行高级综合、协同仿真,记录相应结果。对测试用例种子进行变异,获取变异后的测试用例,并对变异后的测试用例,进行高级综合、协同仿真,记录相应结果,对比前后仿真结果差异性,以发现高级综合工具所存在的缺陷。具体步骤如下:

步骤1:利用爬虫技术,搜集已有C语言测试用例程序,构建测试用例种子池;

具体为:从AnghaBench库和CHStoneHLS库中获取测试用例程序,过滤掉无效的程序,构建测试用例种子池。AnghaBench是一个公开的可获得的C语言测试用例集合,它从开源存储库挖掘了超过100万个C程序,官方网站为:http://cuda.dcc.ufmg.br/angha/home。CHStoneHLS用例库是一个基于C语言的高级合成基准程序集合,可从GitHub上获取,具体网址为:https://github.com/lesterhuang/CHStone。本方法使用爬虫技术,分别从AnghaBench库中选择了CSmith集合和Liveness-Driven Random Generated Programs(ldrgen)集合以及CHStoneHLS库中全部的测试用例进行下载,均存储于服务器/home/hls/seed_programs路径下。经本方法过滤处理,构建出具有2万程序的测试用例种子池。

步骤2:检测是否达到测试次数。若未达到,则从步骤1所构建的种子池中随机选取程序文件作为测试用例种子P,并依据测试用例种子生成相应的TestBench文件。若已达到,则停止测试;

具体为:本方法根据种子池中种子程序数量,自动设置测试次数为2万次。若未达到测试次数限制,则从种子池中随机选取程序文件作为测试用例种子P,重命名为Test_xxx_Seed.c,另存于/home/hls/TestCases/Test_xxx/Test_Seed路径下。从Test_xxx_Seed.c提取main()函数生成TestBench文件,命名为Test_xxx_TB.c,同样另存于/home/hls/TestCases/Test_xxx/Test_Seed路径下,删除Test_xxx_Seed.c中的main()函数。若已达到测试次数限制,则停止测试。上述文件名和路径中的“xxx”使用测试次数填充。

步骤3:由脚本生成程序生成并存储TCL脚本,由脚本执行程序通过终端命令行调用Vivado HLS根据TCL脚本对测试用例种子P进行高级综合,以获取到HDL代码HP;

具体为:本步骤的脚本生成程序根据种子用例P以及TestBench文件位置生成TCL脚本。通过TCL文件为Vivado HLS指定新工程名称,具体生成的代码为:open_project-reset proj_test_xxx_seed,为Vivado HLS指定测试用例种子P以及TestBench文件,具体生成的代码为:add_filesTest_xxx_Seed.c和add_files-tbTest_xxx_TB.c,设置顶层函数,具体生成的代码为:set_topmaintest(),设置解决方案名称,具体生成的代码为:open_solution-reset solution_test_xxx_seed,定义技术和时钟速率,具体生成的代码为:set_partzynq和create_clock–period“75MHz”,指定综合过程,具体生成的代码为:sethls_exec 1,设置优化命令,具体生成的代码为:setdirective_pipeline“VectoerAdd/myloop”,运行待测试高级综合工具进行综合,具体生成的代码为:csynth_design和exit。将上述代码存储为TCL文件,命名为“test_xxx_run_hls.tcl”,并将TCL文件存储于/home/hls/TestCases/Test_xxx/Test_Seed路径下。脚本执行程序通过Linux终端调用VivadoHLS执行TCL脚本进行高级综合,终端执行的命令为:vivado_hls-f/home/hls/TestCases/Test_xxx/Test_Seed/test_xxx_run_hls.tcl。高级综合后所得到的HDL代码HP存放于/home/hls/TestCases/Test_xxx/Test_Seedproj_test_xxx_seed/solution_test_xxx_seed/syn/Verilog路径下,命名为“Test_xxx_Seed.v”。上述文件名和路径中的“xxx”使用测试次数填充。

步骤4:使用GCC编译器和Iverilog仿真模拟器对P与HP进行协同仿真,在相同TestBench下,获取并保存P的覆盖率情况C、P的输出结果HLO以及HP的输出结果O;

具体为:使用GCC编译器编译运行P,具体执行的命令为:gccTest_xxx_Seed.cTest_xxx_TB.c-oTest_xxx_Seed和./Test_xxx_Seed,获取到输出结果HLO,利用Iverilog仿真模拟器对HP进行模拟,使用TestBench测试P,具体代码为:iverilogTest_xxx_Seed.vTest_xxx_TB.v,获取到HP的输出结果O。使用gcov工具获取P的覆盖率情况C。其中,GCC是一种开源编译器,可以用于编译执行C/C++、java等高级语言代码。Iverilog是一个轻量、免费、开源的Verilog编译器,能够对verilog代码进行编译和仿真。gcov是一个命令行方式的控制台程序,伴随GCC编译器发布,配合GCC共同实现对C/C++文件的语句覆盖和分支覆盖测试。Test_xxx_TB.v表示被Vivado HLS转换后TestBench文件。本方法中使用的高级语言编译器和数字电路仿真模拟器也可由用户自行选择,用户只需完成相应软件安装并修改本方法中的调用函数即可。上述文件名和路径中的“xxx”使用测试次数填充。

步骤5:检测是否测试用例种子P及其转换后的代码HP是否通过仿真;若未通过则保存P、TestBench、HP、HLO、O以及相应的TCL文件,生成并存储Bug报告,测试次数增加1,并跳转至步骤2继续执行。若通过仿真,则继续执行下一步骤;

具体为:对比步骤4中对于相同的TestBench下,P的输出结果HLO与HDL输出结果O。如果两者一致则表示通过仿真,继续进行后续测试步骤。如果两者不一致,则表示未通过仿真,则保存P、TestBench、HP、HLO、O以及相应的TCL文件,生成并存储Bug报告,测试次数增加1,跳转至步骤2继续执行。若通过仿真,则继续执行下一步骤;其中,本发明中所涉及到的Bug报告主要包括种子测试用例代码P、TestBench文件、HP、HLO、O以及相应的TCL文件等内容。Bug报告具体内容,可以由测试人员根据需求进行配置。

步骤6:检测测试用例种子P是否可变异;

具体为:本实施例设置种子程序最大变异次数为10,此步骤检测种子程序已经变异次数,若变异次数已经超过10次则不可再变异,测试次数加1,并跳至步骤2。若未超过,则继续进行后续测试。

步骤7:根据步骤4中获取到的测试用例种子程序P覆盖率情况C,代码变异程序对测试用例种子P进行代码删除、插入、转换等变异操作,获取到变异后的测试用例P′;

具体为:根据步骤4中所获取到的测试用例种子程序P的覆盖率C,代码变异程序对P随机选择代码删除、插入、转换等变异操作,获取到变异后新的测试用例P′,文件命名为“Test_xxx_Mutation_yy.c”,另存于/home/hls/TestCases/Test_xxx/Test_xxx_Mutation_yy路径下。其中,代码删除是删除测试用例种子代码中没有被TestBench覆盖的代码,代码插入是在测试用例种子代码局部插入不影响程序输出且符合电路设计的代码,代码转换则是根据待测工具综合过程中可选功能,对测试用例种子代码中的for循环进行合并、数据流化、并行化等操作,对数组进行分割、映射以及重组等操作、对函数进行内联、重组等操作。上述文件名和路径中的“xxx”使用测试次数填充,“yy”使用变异次数填充;

步骤8:脚本修改程序修改原有TCL脚本并另存为新的TCL脚本,脚本执行程序通过终端命令行调用Vivado HLS根据新的TCL脚本对步骤7中所得到的变异后的测试用例P′进行高级综合,以获取到HDL代码HP′;

具体为:首先,脚本修改程序获取到与种子代码所对应的原有TCL文件“test_xxx_run_hls.tcl”,修改其中的工程名称为“proj_test_xxx_mutation_yy”、修改测试用例为“Test_xxx_Mutation_yy.c”、修改解决方案名称为“solution_test_xxx_mutation_yy”,使得修改后的新TCL文件与变异后的测试用例P′所对应,并将修改后的TCL文件另存为新的TCL文件,命名为“test_xxx_mutation_yy_run_hls.tcl”,另存于/home/hls/TestCases/Test_xxx/Test_xxx_Mutation_yy路径下。然后,由脚本执行程序通过Linux终端命令行调用Vivado HLS根据新的TCL脚本对步骤7中所得到的变异后的测试用例P′进行高级综合,终端执行命令为:vivado_hls-f/home/hls/TestCases/Test_xxx/Test_xxx_Mutation_yy/test_xxx_mutation_yy_run_hls.tcl,获取到HDL代码HP′。所获取到的HDL代码HP′存放于/home/hls/TestCases/Test_xxx/proj_test_xxx_mutation_yy/solution_test_xxx_mutation_yy/syn/Verilog路径下,名为“Test_xxx_Mutation_yy.v”。上述文件名和路径中的“xxx”使用测试次数填充,“yy”使用变异次数填充;

步骤9:使用GCC编译器和Iverilog模拟器对P′与HP′进行协同仿真,获取P′的输出HLO′和HP′的输出O′;

具体为:本步骤使用GCC编译器编译运行P′,具体执行的代码为:gccTest_xxx_Mutation_yy.cTest_xxx_TB.c-oTest_xxx_Mutation_yy以及./Test_xxx_Mutation_yy,获取到输出结果HLO′,利用Iverilog仿真模拟器对HP′进行模拟,使用步骤4中的TestBench测试P′,使用被高级综合工具综合后TestBensh文件测试HP′,具体执行的代码为:iverilogTest_xxx_Mutation_yy.vTest_xxx_TB.v,获取到HP′输出结果O′。上述文件名和路径中的“xxx”使用测试次数填充,“yy”使用变异次数填充;

步骤10:检测步骤4中的结果O与步骤9中的结果O′是否相同;若不同则保存P′、HLO′、TestBench、HP′、O′以及相应的TCL文件,生成并存储Bug报告,变异次数增加1,跳转至步骤6继续执行。若结果相同则直接使变异次数增加1,跳转至步骤6继续执行。

当上述过程达到限制的测试次数时,则停止测试工作。本发明方法通过自动化运行上述过程,完成了对于高级综合工具的测试工作。本发明方法收集到大量种子程序,并通过多次变异操作,可得到大量的测试用例,大大增加了测试次数,提高了高级综合工具缺陷检测的效率。本发明方法通过协同仿真,能够有效地检测出高级综合工具所存在的缺陷。

- 一种基于等价取模测试的高级综合工具缺陷检测方法

- 一种基于差异测试的FPGA综合工具缺陷检测方法