一种时钟管理装置、时钟分频模块以及片上系统

文献发布时间:2023-06-19 11:35:49

技术领域

本申请涉及集成电路技术领域,尤其涉及一种时钟管理装置、时钟分频模块以及片上系统。

背景技术

片上系统(SoC:System-on-a-chip)是指在单个芯片上集成一个完整的系统,对所有或部分必要的电子电路进行包分组的技术。当前片上系统芯片为了满足低功耗的要求,会将各个功能模块划分为不同的时钟域。不同的时钟域工作在不同的时钟频率,并且可以根据当前任务负载选择对某一时钟域的工作时钟频率进行调整,或者关闭不参与当前任务的模块的时钟。然而时钟的关断和频率的调整往往会导致不同时钟域时钟之间相位的偏移,使得跨时钟域信号的传输出现比较大的电路和时序上的开销,导致芯片面积增加、性能降低。

针对该情况,现有的一种调整方法为:在各个时钟进行开关或进行频率调整时,先将所有的时钟关闭,等待频率调整设定完成后再一起打开,从而达到相位一致的目的。该方法在调整过程中时钟被关闭,且过程复杂,影响了系统的性能。

因此,提供一种方案以解决片上系统各时钟域的工作时钟在调频或者开关之后出现的相位偏移的问题是非常有必要的。

发明内容

为解决上述问题,本申请提供了一种时钟管理装置,包括:

时钟同步信号发生器、多个时钟门控单元以及多个时钟分频模块;

其中,所述时钟同步信号发生器被配置为产生预定周期的同步信号;

所述多个时钟门控单元与所述多个时钟分频模块一一对应,所述多个时钟门控单元的一个与所述多个时钟分频模块的一个串联,以构成信号处理支路;多个所述信号处理支路并联连接,被配置为接收源时钟信号,所述时钟门控单元被配置为控制所述信号处理支路的开关,所述时钟分频模块被配置为在接收到所述时钟同步信号发生器输出的同步信号后,对所述信号处理支路的时钟信号进行相位调整,将多个所述信号处理支路中的时钟信号由非同步状态调整为同步状态。

可选地,多个所述信号处理支路输出的时钟信号作为多个时钟域的工作时钟。

可选地,所述预定周期为所述多个时钟域的工作时钟的周期的公倍数。

可选地,所述时钟分频模块包括:状态机、同步信号延迟电路以及时钟产生电路;

其中,所述同步信号延迟电路被配置为接收到所述时钟同步信号发生器输出的同步信号后,对所述同步信号进行延迟;

所述状态机被配置为接收到延迟后的同步信号后,若当前多个所述信号处理支路中的时钟信号处于非同步状态,则控制所述时钟产生电路对输出时钟的相位进行调整。

可选地,所述时钟分频模块还包括:计数器以及比较器;

其中,所述计数器被配置为在所述状态机的控制下进行周期性计数,确定当前计数值;

所述比较器被配置为将所述当前计数值与所述时钟分频模块的最大计数阈值进行比较,输出当前状态是否同步的状态信息;在所述当前计数值与所述最大计数阈值一致时,输出当前状态为同步状态的状态信息;在所述当前计数值与所述最大计数阈值不一致时,输出当前状态为非同步状态的状态信息;

所述状态机被配置为接收所述比较器发送的状态信息;

其中,所述最大计数阈值为所述时钟分频模块的预设分频比率减一后的数值。

可选地,所述时钟分频模块还包括:被配置为存储所述最大计数阈值的分频比率寄存器。

可选地,所述预设分频比率的数值被调整时,所述分频比率寄存器中存储的最大计数阈值的数值在所述时钟信号处于同步状态且所述时钟分频模块收到所述同步信号的情况下,对所述最大计数阈值的数值进行修改。

可选地,所述状态机被配置为接收到当前状态为非同步状态的状态信息后,切换至非同步状态,控制所述时钟产生电路关闭时钟输出;在所述计数器计数到所述最大计数阈值后,所述状态机被配置为切换到相位调整状态,所述计数器记录同步信号发生时的当前计数值,作为相位偏移值;在所述计数器继续计数至所述相位偏移值时,所述状态机控制所述时钟产生电路开启时钟输出。

可选地,所述时钟产生电路采用时钟门控单元或触发器翻转实现。

可选地,在所述时钟门控单元对应的信号使能或复位时,所述状态机跳转为非同步状态。

可选地,所述同步信号延迟电路被配置为接收到所述同步信号发生器输出的同步信号后,根据预设分频时钟相位偏移值,以所述源时钟的周期为单位对所述同步信号进行延迟。

本申请还提供了一种时钟分频模块,包括:状态机、同步信号延迟电路以及时钟产生电路;

其中,所述同步信号延迟电路被配置为接收到同步信号后,对所述同步信号进行延迟;

所述状态机被配置为接收到延迟后的同步信号后,若当前时钟信号与其他时钟信号处于非同步状态,则控制所述时钟产生电路对输出时钟的相位进行调整。

可选地,还包括:计数器以及比较器;

其中,所述计数器被配置为在所述状态机的控制下进行周期性计数,确定当前计数值;

所述比较器被配置为将所述当前计数值与所述时钟分频模块的最大计数阈值进行比较,输出当前状态是否同步的状态信息;在所述当前计数值与所述最大计数阈值一致时,输出当前状态为同步状态的状态信息;在所述当前计数值与所述最大计数阈值不一致时,输出当前状态为非同步状态的状态信息;

所述状态机被配置为接收所述比较器发送的状态信息;

其中,所述最大计数阈值为所述时钟分频模块的预设分频比率减一后的数值。

本申请还提供了一种片上系统,包括上述任一种所述的时钟管理装置,所述时钟管理装置输出的时钟信号用于所述片上系统的相同或不同功能模块。

本申请提供的时钟管理装置、时钟分频模块以及片上系统,时钟管理装置包括时钟同步信号发生器、多个时钟门控单元以及多个时钟分频模块;通过时钟同步信号发生器产生预定周期的同步信号;多个时钟门控单元与多个时钟分频模块一一对应,多个时钟门控单元的一个与多个时钟分频模块的一个串联,以构成信号处理支路;多个信号处理支路并联连接来接收源时钟信号,时钟门控单元控制信号处理支路的开关,时钟分频模块被配置为在接收到时钟同步信号发生器输出的同步信号后,对信号处理支路的时钟信号进行相位调整,将多个信号处理支路中的时钟信号由非同步状态调整为同步状态。本申请提供的时钟管理装置、时钟分频模块以及片上系统,实现了对各时钟域的工作时钟相位可控,不需要关闭系统即可实现调整,简化了调整过程,提升了系统的性能。

附图说明

在下文中,将基于实施例参考附图进一步解释本申请。

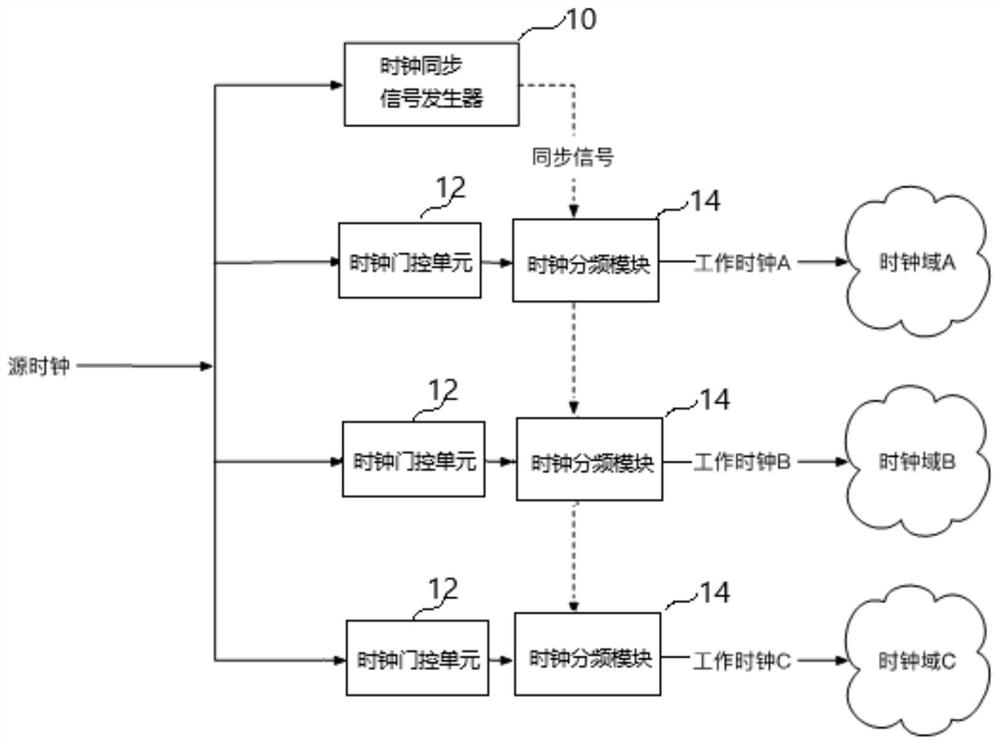

图1示意性地示出本申请所提供的时钟管理装置的一种具体实施方式的结构框图;

图2示意性地示出本申请所提供的时钟分频模块的示意图;

图3示意性地示出时钟分频模块中状态机的状态示意图;

图4示意性地示出本申请所提供的时钟管理装置的相位调整示意图。

具体实施方式

以下将结合附图和具体的实施方式,对本申请的装置进行详细说明。应理解,附图所示以及下文所述的实施例仅仅是说明性的,而不作为对本申请的限制。

图1示出了本申请所提供的时钟管理装置的一种具体实施方式的结构框图。本实施例中,时钟管理装置1包括时钟同步信号发生器10、多个时钟门控单元12以及多个时钟分频模块14。

其中,所述时钟同步信号发生器10被配置为产生预定周期的同步信号;所述多个时钟门控单元12与所述多个时钟分频模块14一一对应,所述多个时钟门控单元12的一个与所述多个时钟分频模块14的一个串联,以构成信号处理支路;多个所述信号处理支路并联连接,被配置为接收源时钟信号,所述时钟门控单元12被配置为控制所述信号处理支路的开关,所述时钟分频模块14被配置为在接收到所述时钟同步信号发生器10输出的同步信号后,对所述信号处理支路的时钟信号进行相位调整,将多个所述信号处理支路中的时钟信号由非同步状态调整为同步状态。

可以理解的是,各个时钟域的工作时钟由源时钟经过时钟门控单元的开关控制以及时钟分频模块得到。即,多个信号处理支路输出的时钟信号作为多个时钟域的工作时钟。

其中,时钟同步信号发生器可以由源时钟驱动计数器构成,可以按照软件配置产生预定周期的脉冲同步信号,可以作为全片时钟的统一的参照物。预定周期可以为多个时钟域的工作时钟的周期的公倍数。可以理解的是,各个时钟域的工作时钟的周期是可调节的。

本申请提供的时钟管理装置,实现了对各时钟域的工作时钟相位可控,不需要关闭系统即可实现调整,简化了调整过程,提升了系统的性能。

作为一种具体实施方式,本申请所提供的时钟分频模块14可以包括:状态机140、同步信号延迟电路142以及时钟产生电路144。如图2本申请所提供的时钟分频模块的示意图所示。其中,所述同步信号延迟电路142被配置为接收到所述同步信号发生器10输出的同步信号后,对所述同步信号进行延迟;所述状态机140被配置为接收到延迟后的同步信号后,若当前多个所述信号处理支路中的时钟信号处于非同步状态,则控制所述时钟产生电路144对输出时钟的相位进行调整。

进一步地,本申请所提供的时钟分频模块14还可以包括:计数器146以及比较器148。其中,所述计数器146被配置为在所述状态机的控制下进行周期性计数,确定当前计数值;所述比较器148被配置为将所述当前计数值与所述时钟分频模块的最大计数阈值进行比较,输出当前状态是否同步的状态信息;在所述当前计数值与所述最大计数阈值一致时,输出当前状态为同步状态的状态信息;在所述当前计数值与所述最大计数阈值不一致时,输出当前状态为非同步状态的状态信息;所述状态机140被配置为接收所述比较器148发送的状态信息。其中,最大计数阈值为时钟分频模块的预设分频比率减一后的数值。例如,对于工作时钟为五分频的时钟,其对应的预设分频比率为5,则最大计数阈值为5-1=4。

其中,时钟分频模块还可以进一步包括:分频比率寄存器150,用于存储上述最大计数阈值。预设分频比率的数值可以根据实际进行设置。作为一种具体实施方式,预设分频比率的数值被调整时,所述分频比率寄存器中存储的最大计数阈值的数值在所述时钟信号处于同步状态且所述时钟分频模块收到所述同步信号的情况下,对所述最大计数阈值的数值进行修改。当分频器分频比率调整时,新的分频系数须在分频器处于同步状态且收到同步信号时,才会更新分频比率寄存器中存储的最大计数阈值。

其中,状态机140可以为有限状态机,其被配置为对时钟分频模块进行控制。计数器146根据预设分频比率进行周期性计数,确定出当前计数值。比较器将当前计数值与最大计数阈值进行比较,以判断当前状态为同步状态或非同步状态。在当前计数值与最大计数阈值一致时,当前状态为同步状态。在当前计数值与最大计数阈值不一致时,当前状态为非同步状态。状态机140根据比较器得到的状态信息,控制时钟产生电路144对输出时钟的相位进行调整。

状态机被配置为接收到当前状态为非同步状态的状态信息后,切换至非同步状态,控制所述时钟产生电路关闭时钟输出;在所述计数器计数到所述最大计数阈值后,所述状态机被配置为切换到相位调整状态,所述计数器记录同步信号发生时的当前计数值,作为相位偏移值;在所述计数器继续计数至所述相位偏移值时,所述状态机控制所述时钟产生电路开启时钟输出。时钟产生电路可以采用时钟门控单元实现,也可以采用触发器翻转实现。这均不影响本申请的实现。

参照图3时钟分频模块中状态机的状态示意图,如图3所示,时钟分频模块中状态机的状态包括同步状态、非同步状态以及相位调整状态。在所述时钟门控单元对应的信号使能或复位时,状态机的状态跳转为非同步状态。时钟分频模块接收到同步信号并且计数器计数达到最大计数阈值时,状态机的状态跳转为同步状态。非同步状态经过相位调整,状态机的状态跳转为同步状态。

具体地,当芯片复位或者时钟关闭时,状态机处于非同步状态。当收到同步信号发生器输出的同步信号后,同步信号延迟电路会对同步信号进行延迟。比较器根据当前计数器的计数值判断当前是否为同步状态。如果判定为同步状态则状态机转为同步状态。如果为非同步状态,则计数器记录当前计数值作为相位偏移值,并进入相位调整状态。计数器的计数限调整为相位偏移值,待相位调整完成后,状态机进入同步状态。

参照图4本申请所提供的时钟管理装置的相位调整示意图,工作时钟A和工作时钟B皆为源时钟的五分频,且相位有偏差。经过同步信号校准后,实现了相位同步。如图4所示,最初工作时钟A与工作时钟B均五分频的周期信号,其对应计数器从0计数到4为一个周期,在计数器计数为0时对应信号上升沿,在计数器计数为3时对应信号下降沿。可以看出工作时钟A与工作时钟B存在相位偏差,对应的预设分频比率均为5,最大计数阈值均为4。

如图4所示,时钟分频模块在接收到同步信号后,对于分频器A,通过计数器记录的当前计数值为3,通过比较器比较当前计数值与最大计数阈值4是否一致。而对于分频器B,通过计数器记录的当前计数值为2,通过比较器比较当前计数值与最大计数阈值4是否一致。在本实施例中是不一致的,则判定当前状态为非同步状态。

在判定当前状态为非同步状态后,状态机由同步状态切换为非同步状态,并且关闭时钟输出。参照图4,工作时钟A与工作时钟B对应的时钟信号输出为0。在计数器这一轮计数完成,即计数达到最大计数阈值4后,状态机切换为相位调整状态。计数器记录同步信号发生时的当前计数值,作为相位偏移值。在本实施例中,对于分频器A,在同步信号发生时分频器A对应的当前计数值为3,则相位偏移值为3。分频器A计数器在上一轮从0计数到最大值4之后,按照相位偏移值为3进行相位调整,即在下一轮继续从0计数到3。对于分频器B,在同步信号发生时分频器B对应的当前计数值为2,则相位偏移值为2。分频器B计数器在上一轮从0计数到最大值4之后,按照相位偏移值为2进行相位调整,即在下一轮继续从0计数到2。在分频器A以及分频器B的计数器计数到各自的相位偏移值后,状态机切换至同步状态,此时再打开时钟输出,此时输出的工作时钟A与工作时钟B即可实现同步。

同步信号延迟电路被配置为接收到所述同步信号发生器输出的同步信号后,根据预设分频时钟相位偏移值,以所述源时钟的周期为单位对所述同步信号进行延迟。本申请中通过对同步信号进行延迟以实现相位可控。例如若第一时钟域的时钟与第二时钟域的时钟之间存在一个相位差,则将第一时钟域收到的同步信号延迟一个周期,这样时钟分频模块再跟延迟后的同步信号保持同步的话,则第一时钟域输出的时钟与第二时钟域也相差一个周期的相位差。

此外,本申请还提供了一种时钟分频模块。参照图2所示,本申请所提供的时钟分频模块14可以包括:状态机140、同步信号延迟电路142以及时钟产生电路144。如图2本申请所提供的时钟分频模块的示意图所示。其中,所述同步信号延迟电路142被配置为接收到同步信号后,对所述同步信号进行延迟,通过延迟同步信号可以实现实现相位可控。例如,如果本领域技术人员希望时钟域A的时钟信号跟别的时钟域相比有一个相位差,则可以设置分频器A的相位偏移值,将时钟域A收到的同步信号延迟一个周期,从而时钟域A就会和别的时钟域存在一个周期的相位差了。所述状态机140被配置为接收到延迟后的同步信号后,若当前多个所述信号处理支路中的时钟信号处于非同步状态,则控制所述时钟产生电路144对输出时钟的相位进行调整。

进一步地,本申请所提供的时钟分频模块14还可以包括:计数器146以及比较器148。其中,所述计数器146被配置为在所述状态机的控制下进行周期性计数,确定当前计数值;所述比较器148被配置为将所述当前计数值与时钟分频模块的最大计数阈值进行比较,输出当前状态是否同步的状态信息;在所述当前计数值与所述最大计数阈值一致时,输出当前状态为同步状态的状态信息;在所述当前计数值与所述最大计数阈值不一致时,输出当前状态为非同步状态的状态信息;所述状态机140被配置为接收所述比较器148发送的状态信息。

可以理解的是,本申请实施例所提供的时钟分频模块可以独立使用,也可以作为上述时钟管理装置的其中一个模块,其具体结构和功能参照上述内容,在此不再赘述。

此外,本申请还提供了一种片上系统,包括上述任一种所述的时钟管理装置,该时钟管理装置输出的时钟信号用于片上系统的相同或不同功能模块。

本申请提供的时钟管理装置、时钟分频模块以及片上系统,实现了对各时钟域的工作时钟相位可控,不需要关闭系统即可实现调整,简化了调整过程,提升了系统的性能。

虽然出于本公开的目的已经描述了本申请各方面的各种实施例,但是不应理解为将本公开的教导限制于这些实施例。在一个具体实施例中公开的特征并不限于该实施例,而是可以和不同实施例中公开的特征进行组合。例如,在一个实施例中描述的根据本申请的方法的一个或多个特征和/或操作,亦可单独地、组合地或整体地应用在另一实施例中。本领域技术人员应理解,还存在可能的更多可选实施方式和变型,可以对上述系统进行各种改变和修改,而不脱离由本申请权利要求所限定的范围。

- 一种时钟管理装置、时钟分频模块以及片上系统

- 时钟分频方法、装置、系统、片上系统及存储介质