衰减器芯片

文献发布时间:2023-06-19 11:35:49

技术领域

本发明属于衰减器技术领域,尤其涉及一种衰减器芯片。

背景技术

随着科学技术的快速发展,通信产品的不断更新换代,终端设备发展也是日新月异,电子产品逐渐的向小型化、高集成度的方向发展。薄膜IPD技术不仅集成度高,功耗低,而且可靠性高,性能稳定。伴随着现代无线通信系统如5G的发展,在为用户带来更快速的无线数据传输的同时,薄膜IPD技术的使用也越来越多,而且具有高可靠性、高稳定性、高抗干扰性能、产品性能一致性好和大量生产成本少等特点,因而IPD技术在微波/射频电路中扮演了重要的角色。

衰减器作为一种可以控制功率增益的元件,衰减器主要用来控制电路传输功率的大小,正广泛应用于各种电路中,无论是在通信技术,雷达相控技术,射频技术,还是其他电子电路方面,只要有放大电路,几乎都离不开衰减器。目前市场上的衰减器主要有两种:一种是组合电路,最简单的纯电阻型衰减电路也需要三个电阻,对于一些精度、稳定性等要求不高的电路,可以使用纯电阻电路、阻容电路或者阻抗电路组合的衰减电路;另外一种是使用IPD衰减器芯片:主要应用在单片微波电路中,用于微波电路的IPD衰减器的设计与研究,要求分布参数小,应用频带范围宽,性能稳定可靠,指标重复性好,具有较强的抗干扰能力。

电子元件的小型化成为研制微波无源衰减器的关键问题之一。由于我国的IPD发展的比较缓慢,自主研发的产品比较少,目前使用的IPD衰减器,大多数都是从国外进口,这样就出现了购货成本高,周期长的问题,给微波/射频电路的发展以及高科技武器的进步带来了很大的困难和阻碍,因此自主设计和研发IPD衰减器成为一件迫在眉睫的技术。

发明内容

本发明的目的在于提供一种衰减器芯片,旨在实现信号衰减功能同时解决衰减器小型化的问题。

本发明实施例提出了一种衰减器芯片,包括介质基板和生长于所述介质基板上的输入端、输出端、第一薄膜电阻、第二薄膜电阻、第三薄膜电阻、第一接地焊盘、第二接地焊盘、第一接地端、第二接地端、第三接地端和多条传输线,所述输入端、所述输出端、所述第一薄膜电阻、所述第二薄膜电阻、所述第三薄膜电阻、所述第一接地焊盘、所述第二接地焊盘、所述第一接地端、所述第二接地端和所述第三接地端均呈方形结构;

所述输入端通过第一传输线与所述第一薄膜电阻的第一端连接,所述第一薄膜电阻的第二端、所述第二薄膜电阻的第一端和所述第三薄膜电阻的第一端共接,所述第二薄膜电阻通过第二传输线与所述输出端连接,所述第三薄膜电阻的第二端通过第三传输线与所述第一接地焊盘连接且通过第四传输线与所述第二接地焊盘连接以及通过第五传输线与所述第三接地端连接,所述第一接地焊盘还通过第六传输线与所述第一接地端连接,所述第二接地焊盘还通过第七传输线与所述第二接地端连接。

在一个实施例中,所述衰减器芯片还包括呈方形结构的第三接地焊盘、第四接地焊盘、第四接地端和第五接地端;

所述第三接地焊盘通过第八传输线与所述第四接地端连接,所述第四接地焊盘通过第九传输线与所述第五接地端连接。

在一个实施例中,所述输入端、所述第一薄膜电阻、所述第二薄膜电阻和所述输出端沿第一方向平行设置,所述第一接地焊盘和所述第二接地焊盘沿与第一方向平行的第二方向平行设置,所述第一薄膜电阻与所述第二薄膜电阻与所述第三薄膜电阻垂直设置并对称设置于所述第三薄膜电阻的两侧,所述第一薄膜电阻和所述第二薄膜电阻的尺寸相同。

在一个实施例中,所述第一接地焊盘、所述输入端和所述第三接地焊盘沿与第一方向垂直的第三方向平行设置,所述第一接地焊盘和所述第三接地焊盘对称设置于所述输入端的两侧;

所述第二接地焊盘、所述输出端和所述第四接地焊盘沿与第三方向平行的第四方向平行设置,所述第二接地焊盘和所述第四接地焊盘对称设置于所述输出端的两侧。

在一个实施例中,所述第一接地焊盘和所述第三接地焊盘与所述输入端之间的距离均为140um~160um;

所述第二接地焊盘和所述第四接地焊盘均与所述输出端之间的距离为140um~160um。

在一个实施例中,各所述传输线呈直线连接,所述第一传输线、所述第二传输线、所述第三传输线和所述第四传输线等长等宽;

所述输入端和所述输出端的尺寸相等,所述第一接地端、所述第二接地端、所述第三接地端和所述第四接地端尺寸相等。

在一个实施例中,所述第一传输线和所述第二传输线的长度范围为100um~150um且宽度范围为25um~35um;

所述第三传输线和所述第四传输线的长度范围为170um~180um且宽度范围为25um~35um;

所述第一薄膜电阻和所述第二薄膜电阻的长度范围为2um~10um且宽度范围为30um~50um,所述第三薄膜电阻的长度范围为120um~140um且宽度范围为10um~20um。

在一个实施例中,所述第一传输线和所述第二传输线的长度范围为100um~150um且宽度范围为25um~35um;

所述第三传输线和所述第四传输线的长度范围为165um~175um且宽度范围为25um~35um;

所述第一薄膜电阻和所述第二薄膜电阻的长度范围为2um~10um且宽度范围为25um~35um,所述第三薄膜电阻的长度范围为100um~110um且宽度范围为20um~30um。

在一个实施例中,所述第一传输线和所述第二传输线的长度范围为120um~170um且宽度范围为35um~45um;

所述第三传输线和所述第四传输线的长度范围为175um~185um且宽度范围为25um~35um;

所述第一薄膜电阻和所述第二薄膜电阻的长度范围为2um~10um且宽度范围为35um~45um,所述第三薄膜电阻的长度范围为105um~115um且宽度范围为35um~45um。

在一个实施例中,所述介质基板的材料为砷化镓材料,所述第一薄膜电阻、所述第二薄膜电阻和所述第三薄膜电阻的材料为氮化钽材料。

本发明实施例与现有技术相比存在的有益效果是:上述的衰减器芯片通过介质基板和生长于所述介质基板上的输入端、输出端、第一薄膜电阻、第二薄膜电阻、第三薄膜电阻、第一接地焊盘、第二接地焊盘、第一接地端、第二接地端、第三接地端和多条传输线组成,第一薄膜电阻、第二薄膜电阻和第三薄膜电阻组成T型纯电阻衰减器,以对信号源输出的信号进行信号处理,通过采用集成无源器件工艺将各元器件集成于同一芯片上,具有集成度高、版图面积小、衰减精度高、设计简单、可靠性高的特点。

附图说明

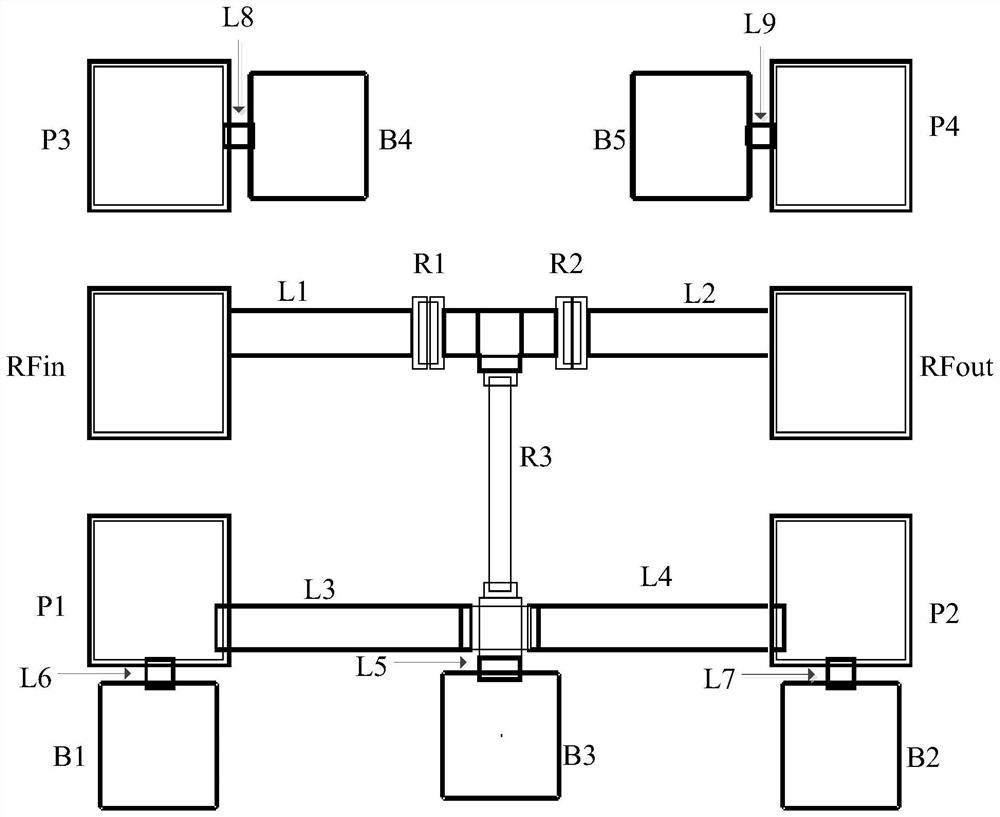

图1为本发明实施例提供的衰减器芯片的结构示意图;

图2为本发明实施例提供的衰减器芯片的衰减器精度的仿真曲线示意图;

图3为本发明实施例提供的衰减器芯片的驻波比的仿真曲线示意图。

具体实施方式

为了使本发明所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

本发明实施例提出了一种衰减器芯片。

如图1所示,图1为本发明实施例提供的衰减器芯片的结构示意图,本实施例中,衰减器芯片包括介质基板和生长于介质基板上的输入端RFin、输出端RFout、第一薄膜电阻R1、第二薄膜电阻R2、第三薄膜电阻R3、第一接地焊盘P1、第二接地焊盘P2、第一接地端B1、第二接地端B2、第三接地端B3和多条传输线,输入端RFin、输出端RFout、第一薄膜电阻R1、第二薄膜电阻R2、第三薄膜电阻R3、第一接地焊盘P1、第二接地焊盘P2、第一接地端B1、第二接地端B2和第三接地端B3均呈方形结构;

输入端RFin通过第一传输线L1与第一薄膜电阻R1的第一端连接,第一薄膜电阻R1的第二端、第二薄膜电阻R2的第一端和第三薄膜电阻R3的第一端共接,第二薄膜电阻R2通过第二传输线L2与输出端RFout连接,第三薄膜电阻R3的第二端通过第三传输线L3与第一接地焊盘P1连接且通过第四传输线L4与第二接地焊盘P2连接以及通过第五传输线L5与第三接地端B3连接,第一接地焊盘P1还通过第六传输线L6与第一接地端B1连接,第二接地焊盘P2还通过第七传输线L7与第二接地端B2连接。

本实施例中,衰减器芯片采用IPD(Integrated Passive Devices,集成无源器件)工艺,采用介质基板为衬底,在衬底上通过曝光、显影、镀膜、扩散、刻蚀等薄膜制程生长出整个衰减器电路,衰减器电路包括输入端RFin、输出端RFout、第一薄膜电阻R1、第二薄膜电阻R2、第三薄膜电阻R3、第一接地焊盘P1、第二接地焊盘P2、第一接地端B1、第二接地端B2、第三接地端和多条传输线,其中,输入端RFin、输出端RFout和接地端构成衰减器芯片的信号引脚,用于信号输入、信号输出和接地,其中,输入端RFin用于连接信号源,输出端RFout用于连接后端电路或者负载,接地端用于接地,第一薄膜电阻R1、第二薄膜电阻R2和第三薄膜电阻R3构成T型纯电阻衰减器,通过将输入端RFin输入的信号进行衰减处理并从输出端RFout输出,实现信号转换和阻抗匹配功能。

介质基板用于承载衰减器电路,其中,介质基板为单层的介质板,为了顺应当前射频无源器件的发展趋势,在一个实施例中,介质基板的材料为砷化镓(GaAs)材料,接地焊盘用于传递公共地信号,实现薄膜电阻与接地端的连接及接地。

可以理解的是,衰减器芯片的衰减量由薄膜电阻的阻值决定,而薄膜电阻的阻值由其尺寸决定,因此,本实施例中,第一薄膜电阻R1、第二薄膜电阻R2和第三薄膜电阻R3的尺寸可根据需求对应设置,以得到不同衰减量的衰减器芯片。

同时,各信号端、接地焊盘、薄膜电阻呈方形结构,其位置和尺寸可根据工艺需求和信号处理需求对应设置,在此不做具体限制。

在一个实施例中,输入端RFin、第一薄膜电阻R1、第二薄膜电阻R2和输出端RFout沿第一方向平行设置,第一接地焊盘P1和第二接地焊盘P2沿与第一方向平行的第二方向平行设置,第一薄膜电阻R1与第二薄膜电阻R2与第三薄膜电阻R3垂直设置并对称设置于第三薄膜电阻R3的两侧,第一薄膜电阻R1和第二薄膜电阻R2的尺寸相同。

本实施例中,第一薄膜电阻R1和第二薄膜电阻R2垂直对称设置于第三薄膜电阻R2的两端,形成对称T型纯电阻衰减器,从而保证两个端口的发射系数和传输系数保持一致。

薄膜电阻的材料可根据工艺需求和应用场景对应选择,在一个实施例中,第一薄膜电阻R1、第二薄膜电阻R2和第三薄膜电阻R3的材料为氮化钽材料,氮化钽材料可应用恶劣环境中。

本发明实施例与现有技术相比存在的有益效果是:上述的衰减器芯片通过介质基板和生长于介质基板上的输入端RFin、输出端RFout、第一薄膜电阻R1、第二薄膜电阻R2、第三薄膜电阻R3、第一接地焊盘P1、第二接地焊盘P2、第一接地端B1、第二接地端B2、第三接地端B3和多条传输线组成,第一薄膜电阻R1、第二薄膜电阻R2和第三薄膜电阻R3组成T型纯电阻衰减器,以对信号源输出的信号进行信号处理,通过采用集成无源器件工艺将各元器件集成于同一芯片上,芯片尺寸可达0.62mm*0.73mm*0.1mm,具有集成度高、版图面积小、衰减精度高、设计简单、可靠性高的特点。

请继续参阅图1,在一个实施例中,衰减器芯片还包括呈方形结构的第三接地焊盘、第四接地焊盘、第四接地端B4和第五接地端B5;

第三接地焊盘通过第八传输线L8与第四接地端B4连接,第四接地焊盘通过第九传输线L9与第五接地端B5连接。

本实施例中,其中,第四接地端B4和第五接地端B5用于接地,第三接地焊盘P3和第四接地焊盘P4用于方便探针台测试需要以及起接地作用。

第三接地焊盘P3、第四接地焊盘P4、第四接地端B4和第五接地端B5的位置和尺寸可根据制造工艺和测试需求对应设置,在一个实施例中,第一接地焊盘P1、输入端RFin和第三接地焊盘沿与第一方向垂直的第三方向平行设置,第一接地焊盘P1和第三接地焊盘对称设置于输入端RFin的两侧;

第二接地焊盘P2、输出端RFout和第四接地焊盘沿与第三方向平行的第四方向平行设置,第二接地焊盘P2和第四接地焊盘对称设置于输出端RFout的两侧。

通过将接地焊盘对称设置,方便探针台对衰减器进行对称测试,同时,为了满足当前测试装配需求,在一个实施例中,第一接地焊盘P1和第三接地焊盘与输入端RFin之间的距离均为140um~160um;

第二接地焊盘P2和第四接地焊盘均与输出端RFout之间的距离为140um~160um。

进一步地,为了达到匹配阻抗,提高电压驻波比性能的作用,在一个实施例中,各传输线呈直线连接,第一传输线L1、第二传输线L2、第三传输线L3和第四传输线L4等长等宽;

输入端RFin和输出端RFout的尺寸相等,第一接地端B1、第二接地端B2、第三接地端B3和第四接地端B4尺寸相等。

为了获取不同的衰减量,可对传输线和薄膜电阻的尺寸对应设置,在一个实施例中,第一传输线L1和第二传输线L2的长度范围为100um~150um且宽度范围为25um~35um;

第三传输线L3和第四传输线L4的长度范围为170um~180um且宽度范围为25um~35um;

第一薄膜电阻R1和第二薄膜电阻R2的长度范围为2um~10um且宽度范围为30um~50um,第三薄膜电阻R3的长度范围为120um~140um且宽度范围为10um~20um。

通过仿真设计,本实施例中,衰减器芯片的衰减量为1dB,如图2所示,通带范围为DC 0GHz~40GHz,衰减器的衰减精度在±0.2dB,波动越小,衰减器的衰减器精度越高,如图3所示,本实施例中,带内驻波比均优于1.2,具有良好的频率选择性,其中,驻波比指波腹电压与波谷电压之比,驻波比是一个数值,当比值等于1时,信号传输没有任何反射全部发射出去,是最理想的情况,比值越大信号反射的越多。

在另一个实施例中,第一传输线L1和第二传输线L2的长度范围为100um~150um且宽度范围为25um~35um;

第三传输线L3和第四传输线L4的长度范围为165um~175um且宽度范围为25um~35um;

第一薄膜电阻R1和第二薄膜电阻R2的长度范围为2um~10um且宽度范围为25um~35um,第三薄膜电阻R3的长度范围为100um~110um且宽度范围为20um~30um。

通过仿真设计,本实施例中,衰减器芯片的衰减量为2dB,如图2所示,通带范围为DC 0GHz~40GHz,衰减器的衰减精度在±0.2dB,波动越小,衰减器的衰减器精度越高,如图3所示,本实施例中,带内驻波比均优于1.2,具有良好的频率选择性,其中,驻波比指波腹电压与波谷电压之比,驻波比是一个数值,当比值等于1时,信号传输没有任何反射全部发射出去,是最理想的情况,比值越大信号反射的越多。

在又一个实施例中,第一传输线L1和第二传输线L2的长度范围为120um~170um且宽度范围为35um~45um;

第三传输线L3和第四传输线L4的长度范围为175um~185um且宽度范围为25um~35um;

第一薄膜电阻R1和第二薄膜电阻R2的长度范围为2um~10um且宽度范围为35um~45um,第三薄膜电阻R3的长度范围为105um~115um且宽度范围为35um~45um。

通过仿真设计,本实施例中,衰减器芯片的衰减量为3dB,如图2所示,通带范围为DC 0GHz~40GHz,衰减器的衰减精度在±0.2dB,波动越小,衰减器的衰减器精度越高,如图3所示,本实施例中,带内驻波比均优于1.2,具有良好的频率选择性,其中,驻波比指波腹电压与波谷电压之比,驻波比是一个数值,当比值等于1时,信号传输没有任何反射全部发射出去,是最理想的情况,比值越大信号反射的越多。

进一步地,为了匹配制造工艺,在一个实施例中,输入端RFin与输出端RFout的尺寸相同均为100um*100um,接地端的尺寸为84um*84um。

通过采用集成无源器件工艺将各元器件集成于同一芯片上,芯片尺寸可达0.62mm*0.73mm*0.1mm,在实现了信号衰减功能的同时,降低了衰减器芯片的整体尺寸,实现了芯片小型化。

以上所述实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围,均应包含在本发明的保护范围之内。

- 一种用于CMOS宽带幅相多功能芯片的衰减器电路

- 衰减器芯片