包括具有中介桥的层叠子封装的半导体封装

文献发布时间:2023-06-19 11:35:49

技术领域

本公开涉及半导体封装技术,更具体地,涉及包括层叠的子封装的半导体封装,各个子封装具有一个或更多个半导体芯片和中介桥(interposing bridge)。

背景技术

近来,大量努力集中在将多个半导体芯片集成到单个半导体封装中。即,已尝试增加封装集成密度以实现利用多功能操作高速处理大量数据的高性能半导体封装。例如,系统封装(SiP)技术可被视为实现高性能半导体封装的有吸引力的候选。

随着高性能移动系统的发展,对更大的大容量电池的需求日益增加,移动系统中包括的其它组件的尺寸和厚度已减小,以维持可取的形状因子。因此,寻求紧凑的系统封装或紧凑的半导体封装以实现高性能移动系统。

发明内容

根据实施方式,一种半导体封装包括互连层、设置在互连层上的第一子封装以及依次层叠在第一子封装上的第二子封装和第三子封装。第一子封装包括第一半导体芯片和第一中介桥。第一中介桥与第一半导体芯片间隔开并且被配置为包括第一层通孔。第二子封装包括第二半导体芯片、第二中介桥和第一再分布线。第二中介桥与第二半导体芯片间隔开并且被配置为包括第二层通孔,所述第二层通孔与所述第一层通孔中的相应通孔交叠并且电连接到所述第一层通孔中的相应通孔。第一再分布线将第二半导体芯片电连接到所述第二层通孔中的第一通孔。第三子封装包括第三半导体芯片、第三中介桥和第二再分布线。第三中介桥与第三半导体芯片间隔开并且被配置为包括第三层通孔,所述第三层通孔与所述第二层通孔中的相应通孔交叠并且电连接到所述第二层通孔中的相应通孔。第二再分布线将第三半导体芯片电连接到所述第三层通孔中的第二通孔。

根据另一实施方式,一种半导体封装包括互连层、第一子封装、第二子封装、第三子封装、第四子封装和第五子封装。第一子封装设置在互连层上。第二子封装、第三子封装、第四子封装和第五子封装依次层叠在第一子封装上。第一子封装包括第一半导体芯片和第一中介桥。第一中介桥与第一半导体芯片间隔开并且被配置为包括第一层通孔。第二子封装和第三子封装中的每一个包括第二半导体芯片、第二中介桥和第一再分布线。第二中介桥与第二半导体芯片间隔开并且被配置为包括第二层通孔,所述第二层通孔与所述第一层通孔中的相应通孔交叠并且电连接到所述第一层通孔中的相应通孔。第一再分布线将第二半导体芯片电连接到所述第二层通孔中的第一通孔。第四子封装和第五子封装中的每一个包括第三半导体芯片、第三中介桥和第二再分布线。第三中介桥与第三半导体芯片间隔开并且被配置为包括第三层通孔,所述第三层通孔与所述第二层通孔中的相应通孔交叠并且电连接到所述第二层通孔中的相应通孔。第二再分布线将第三半导体芯片电连接到所述第三层通孔中的第二通孔。

根据另一实施方式,一种半导体封装包括互连层、在互连层上的第一子封装以及依次层叠在第一子封装上的第二子封装和第三子封装。第一子封装、第二子封装和第三子封装中的每一个包括半导体芯片和中介桥。中介桥与半导体芯片间隔开并且被配置为包括第一通孔和第二通孔。第二子封装还包括将第二子封装的半导体芯片电连接到第一通孔的第一再分布线。第三子封装还包括将第三子封装的半导体芯片电连接到第二通孔的第二再分布线。

附图说明

图1是示出根据实施方式的半导体封装的横截面图。

图2是示出图1的半导体封装中包括的中介桥的层叠部分的放大图。

图3是示出图1的半导体封装中包括的第一子封装的横截面图。

图4、图5和图6示出图1的半导体封装中包括的第二子封装。

图7和图8示出图1的半导体封装中包括的第三子封装。

图9和图10示出图1的半导体封装中包括的第四子封装。

图11和图12示出图1的半导体封装中包括的第五子封装。

图13和图14是示出设置在图1的半导体封装的子封装之间的支撑件的横截面图。

图15是示出根据另一实施方式的半导体封装的横截面图。

图16是示出图15的半导体封装中包括的第一子封装的横截面图。

图17和图18示出图15的半导体封装中包括的第二子封装和第三子封装。

图19和图20示出图15的半导体封装中包括的第四子封装和第五子封装。

图21是示出根据另一实施方式的半导体封装的平面图。

图22是示出采用包括根据实施方式的半导体封装中的至少一个的存储卡的电子系统的框图。

图23是示出包括根据实施方式的半导体封装中的至少一个的另一电子系统的框图。

具体实施方式

本文所使用的术语可对应于考虑其在所呈现的实施方式中的功能而选择的词语,术语的含义可被解释为根据实施方式所属领域的普通技术人员而不同。如果详细定义,则可根据定义来解释术语。除非另外定义,否则本文所使用的术语(包括技术术语和科学术语)具有实施方式所属领域的普通技术人员通常理解的相同含义。

将理解,尽管本文中可使用术语“第一”、“第二”、“第三”等来描述各种元件,但是这些元件不应受这些术语限制。这些术语仅用于将一个元件与另一元件相区分,而非用于指示元件的特定顺序或数量。

还将理解,当元件或层被称为在另一元件或层“上”、“上方”、“下面”、“下方”或“外侧”时,该元件或层可与另一元件或层直接接触,或者可存在中间元件或层。用于描述元件或层之间的关系的其它词语应该以类似的方式解释(例如,“在...之间”与“直接在...之间”或者“相邻”与“直接相邻”)。

诸如“在...之下”、“在...下面”、“下”、“上面”、“上”、“顶部”、“底部”等的空间相对术语可用于描述元件和/或特征与另一元件和/或特征的关系(例如,如图中所示)。将理解,除了附图中所描绘的取向之外,空间相对术语旨在涵盖装置在使用和/或操作中的不同取向。例如,当附图中的装置翻转时,被描述为在其它元件或特征下面和/或之下的元件将被取向为在其它元件或特征上面。装置可按照其它方式取向(旋转90度或处于其它取向)并且相应地解释本文中所使用的空间相对描述符。

根据各种实施方式的半导体封装可包括诸如半导体芯片或半导体管芯的电子装置。半导体芯片或半导体管芯可通过使用划片工艺将诸如晶圆的半导体基板分离成多片来获得。半导体芯片可对应于存储器芯片、逻辑芯片、专用集成电路(ASIC)芯片、应用处理器(AP)、图形处理单元(GPU)、中央处理单元(CPU)或系统芯片(SoC)。存储器芯片可包括集成在半导体基板上的动态随机存取存储器(DRAM)电路、静态随机存取存储器(SRAM)电路、NAND型闪存电路、NOR型闪存电路、磁随机存取存储器(MRAM)电路、电阻式随机存取存储器(ReRAM)电路、铁电随机存取存储器(FeRAM)电路或相变随机存取存储器(PcRAM)电路。逻辑芯片可包括集成在半导体基板上的逻辑电路。半导体封装可用在诸如移动电话的通信系统、与生物技术或保健关联的电子系统或可穿戴电子系统中。半导体封装可适用于物联网(IoT)。

贯穿说明书,相同的标号表示相同的元件。即使标号可能未参照一幅图提及或描述,该标号也可参照另一幅图提及或描述。另外,即使标号可能未在一幅图中示出,其也可在另一幅图中示出。

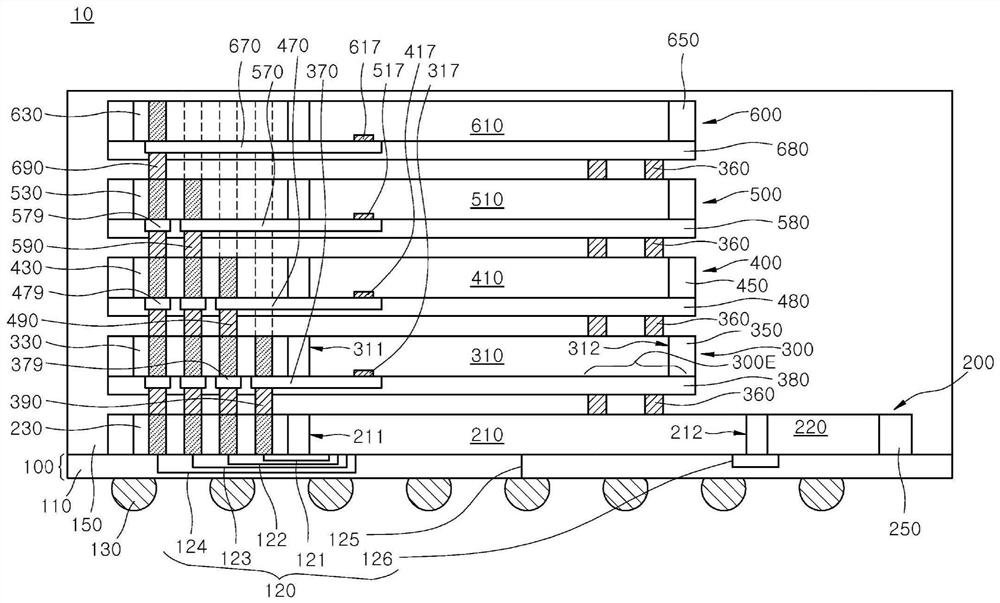

图1是示出根据实施方式的半导体封装10的横截面图。图2是示出图1的半导体封装10中包括的中介桥230、330、430、530和630的层叠部分的放大图。

参照图1和图2,半导体封装10可被配置为包括设置在互连层100上的第一子封装200以及依次层叠在第一子封装200上的第二子封装300和第三子封装400。半导体封装10还可包括依次地且垂直地层叠在第三子封装400上的第四子封装500和第五子封装600。

第一至第五子封装200、300、400、500和600可构成一个模块。由于第一至第五子封装200、300、400、500和600构成一个模块,所以可使用模块的组装工艺来制造半导体封装10。第一至第五子封装200、300、400、500和600可垂直地层叠以提供具有层叠封装结构的半导体封装10。垂直层叠的第一至第五子封装200、300、400、500和600的结构可与堆叠式封装(PoP)的结构类似。

半导体封装10可被配置为还包括第六密封剂150。第六密封剂150可设置在互连层100上以覆盖第一至第五子封装200、300、400、500和600。第六密封剂150可包括各种密封剂材料中的至少一种。第六密封剂150可由模制层(例如,环氧模塑料(EMC)层)形成。

图3是示出图1的半导体封装10中包括的第一子封装200的横截面图。

参照图1和图3,第一子封装200可被配置为包括第一半导体芯片210、辅助半导体芯片220(以下,称为第六半导体芯片)、第一中介桥230和第一密封剂250。第一半导体芯片210可以是诸如应用处理器(AP)的处理器芯片。第六半导体芯片220可以是缓冲存储器芯片,其提供当半导体封装10或第一半导体芯片210操作时用作高速缓存存储器的缓冲存储器。第六半导体芯片220可以是DRAM装置。

第一中介桥230可被设置为与第一半导体芯片210的第一边缘211横向间隔开。

第六半导体芯片220可设置在第一半导体芯片210的与第一中介桥230相反的一侧。

第六半导体芯片220可被设置为与第一半导体芯片210的第二边缘212横向间隔开。第一半导体芯片210的第二边缘212可被设置为与第一半导体芯片210的第一边缘211相反。

第一中介桥230可以是将互连层100垂直地电连接到第二子封装300的垂直连接构件。第一中介桥230可包括设置在第一水平处的第一层通孔231、232、233和234。第一层通孔231、232、233和234可对应于垂直地穿透第一中介桥230的主体的硅通孔(TSV)。第一中介桥230的第一层通孔231、232、233和234可形成为包括诸如金属材料(例如,铜材料)的导电材料。由于第一层通孔231、232、233和234由TSV形成,所以可使设置在有限区域中的通孔231、232、233和234的数量最大化。第一中介桥230的主体可以是硅管芯或硅芯片。

第一半导体芯片210与第一层通孔231、232、233和234中的第一通孔231之间的距离可小于第一半导体芯片210与第一层通孔231、232、233和234中的第二通孔232之间的距离。第一半导体芯片210与第一层通孔231、232、233和234中的第三通孔233之间的距离可大于第一半导体芯片210与第一层通孔231、232、233和234中的第二通孔232之间的距离。第一半导体芯片210与第一层通孔231、232、233和234中的第四通孔234之间的距离可大于第一半导体芯片210与第一层通孔231、232、233和234中的第三通孔233之间的距离。

第一密封剂250可被设置为部分地覆盖第一半导体芯片210、第六半导体芯片220和第一中介桥230。如图3所示,第一密封剂250可被设置为暴露第一中介桥230的顶表面230T。因此,第一层通孔231、232、233和234可由第一密封剂250露出。第一密封剂250还可被设置为暴露第一半导体芯片210的顶表面210T和第六半导体芯片220的顶表面220T。在实施方式中,尽管图中未示出,第一密封剂250可延伸以覆盖第一半导体芯片210的顶表面210T和第六半导体芯片220的顶表面220T。

第一密封剂250可被设置为填充第一半导体芯片210、第六半导体芯片220和第一中介桥230之间的间隙区域。第一密封剂250可被设置为提供第一子封装200的主体形状。第一密封剂250可形成为包括各种密封剂材料中的至少一种。第一密封剂250可通过模制EMC材料来形成。

再参照图1和图3,第一层通孔231、232、233和234可被设置为彼此电绝缘。互连层100可被配置为包括介电层110以及设置在介电层110中的导电互连图案120。介电层110可形成为包括各种介电材料中的至少一种。介电层110可形成为包括层叠的多个介电层。可在执行封装工艺的同时使用再分布工艺将互连层100形成为包括多个再分布线。

第一水平互连图案121、第二水平互连图案122、第四水平互连图案123和第五水平互连图案124可设置在介电层110中。第一水平互连图案121可以是用于将第一通孔231电连接到第一半导体芯片210的导电图案。第二水平互连图案122可以是用于将第二通孔232电连接到第一半导体芯片210的导电图案。第四水平互连图案123可以是用于将第三通孔233电连接到第一半导体芯片210的导电图案。第五水平互连图案124可以是用于将第四通孔234电连接到第一半导体芯片210的导电图案。第一水平互连图案121、第二水平互连图案122、第四水平互连图案123和第五水平互连图案124可提供用于将第一至第四通孔231、232、233和234电连接到第一半导体芯片210的独立路径。

外连接器130可附接到互连层100。外连接器130可以是用于将半导体封装10连接到外部装置或外部系统的电连接构件。外连接器130可以是例如焊球。互连层100还可包括将第一半导体芯片210电连接到外连接器130的垂直互连图案125。互连层100还可包括将第一半导体芯片210电连接到第六半导体芯片220的第三水平互连图案126。

在实施方式中,互连层100可以是将第一至第五子封装200、300、400、500和600电连接到外部电子装置、外部模块板等的互连构件。当互连层100被配置为包括再分布线时,互连层100的厚度可小于一般印刷电路板(PCB)的厚度。因此,可减小半导体封装10的总厚度。

图4是示出图1的半导体封装10中包括的第二子封装300的横截面图。图5是示出图4的第二子封装300中包括的第二半导体芯片310和第二中介桥330的布局M1的平面图。图6是示出图4的第二子封装300中包括的第一再分布线370的布局M2的平面图。图4是沿着图6的线X1-X1’截取的横截面图。

参照图1和图4,第二子封装300可被配置为包括第二半导体芯片310、第二中介桥330和第二密封剂350。第二半导体芯片310可充当存储由第一半导体芯片210计算的数据的存储芯片。第一半导体芯片210可被配置为包括处理芯片,并且第二半导体芯片310可被配置为包括DRAM装置。

第二中介桥330可被设置为与第二半导体芯片310的第一边缘311横向间隔开。第二中介桥330可以是将图1的第三子封装400垂直地电连接到图1的第一子封装200的第一中介桥230的垂直连接构件。第二中介桥330可包括设置在第二水平处的第二层通孔331、332、333和334。第二层通孔331、332、333和334可对应于垂直地穿透第二中介桥330的主体的硅通孔(TSV)。

参照图4和图5,在第二中介桥330中,第二半导体芯片310与第二层通孔331、332、333和334中的第一通孔331之间的距离可小于第二半导体芯片310与第二层通孔331、332、333和334中的第二通孔332之间的距离。第二层通孔331、332、333和334中的第一通孔331可排列在面向第二半导体芯片310的第一边缘311的第一列中。第二层通孔331、332、333和334中的第二通孔332可排列在第二列中,该第二列位于第一列的与第二半导体芯片310相反的一侧。第二层通孔331、332、333和334中的第三通孔333可排列在第三列中,并且第二层通孔331、332、333和334中的第四通孔334可排列在第四列中。第二半导体芯片310与第二层通孔331、332、333和334中的第三通孔333之间的距离可大于第二半导体芯片310与第二层通孔331、332、333和334中的第二通孔332之间的距离。第二半导体芯片310与第二层通孔331、332、333和334中的第四通孔334之间的距离可大于第二半导体芯片310与第二层通孔331、332、333和334中的第三通孔333之间的距离。

参照图4,第二子封装300的第二密封剂350可被设置为部分地覆盖第二半导体芯片310和第二中介桥330。第二密封剂350可被设置为暴露第二中介桥330的顶表面330T和第二半导体芯片310的顶表面310T。在实施方式中,尽管图中未示出,第二密封剂350可延伸以覆盖第二半导体芯片310的顶表面310T。第二密封剂350可被设置为填充第二半导体芯片310和第二中介桥330之间的间隙区域。第二密封剂350可被设置为提供第二子封装300的主体形状。第二密封剂350可形成为包括各种密封剂材料中的至少一种。第二密封剂350可通过模制EMC材料来形成。

参照图4、图5和图6,第二子封装300还可包括第一再分布线370。第一再分布线370可以是用于将第二半导体芯片310连接到第二层通孔331、332、333和334中的第一通孔331的导电图案。第一再分布线370可延伸,使得第一再分布线370的第一部分与第二半导体芯片310的芯片焊盘317中的相应芯片焊盘交叠,并且第一再分布线370的第二部分与第一通孔331中的相应通孔交叠。因此,第一再分布线370可将第二半导体芯片310电连接到第二层通孔331、332、333和334中的第一通孔331。第一再分布线370可延伸以越过填充第二半导体芯片310和第二中介桥330之间的间隙区域的第二密封剂350的表面,并且可到达并接触第一通孔331。

第二层通孔331、332、333和334当中的第二通孔332、第三通孔333和第四通孔334可与第一再分布线370断开,以与第二半导体芯片310电隔离。当形成第一再分布线370时,还可形成通孔焊盘379以与第二层通孔331、332、333和334当中的第二通孔332、第三通孔333和第四通孔334中的相应通孔交叠。

参照图5和图6,第二半导体芯片310的芯片焊盘317可在平面图中排列成一些列。第二半导体芯片310的焊盘区域314可被定义为第二半导体芯片310的面向第二中介桥330的第一边缘311与第二半导体芯片310的与第二中介桥330相反的第二边缘312之间的区域。第二半导体芯片310的焊盘区域314可被定义为使得焊盘区域314与第一边缘311之间的距离小于焊盘区域314与第二边缘312之间的距离。

由于芯片焊盘317被设置在第二半导体芯片310的焊盘区域314上,所以第一边缘311与芯片焊盘317之间的距离可小于第二边缘312与芯片焊盘317之间的距离。因此,可减小第二半导体芯片310的芯片焊盘317与第二中介桥330的第一通孔331之间的距离。如果第二半导体芯片310的芯片焊盘317与第二中介桥330的第一通孔331之间的距离减小,则第一再分布线370的长度可减小,以降低第一再分布线370的电阻值。

再参照图1和图4,第二子封装300可垂直地层叠在第一子封装200上,使得第二层通孔331、332、333和334与第一层通孔231、232、233和234中的相应通孔交叠。第二层通孔331、332、333和334可通过第一内连接器390电连接到第一层通孔231、232、233和234中的相应通孔。第一内连接器390可以是诸如导电凸块的连接构件。第一内连接器390可穿透覆盖第一再分布线370以将第一再分布线370彼此电隔离的介电层380,并且可电连接到与第二通孔332、第三通孔333和第四通孔334交叠的通孔焊盘379中的相应通孔焊盘以及与第一通孔331交叠的第一再分布线370。

第二半导体芯片310可通过包括第一再分布线370、第一内连接器390、第一层通孔中的第一通孔231和第一水平互连图案121的电路径电连接到第一半导体芯片210。即,第一半导体芯片210和第二半导体芯片310可通过包括第一再分布线370、第一内连接器390、第一层通孔中的第一通孔231和第一水平互连图案121的电路径彼此独立地通信,而与第三至第五子封装400、500和600无关。

图7是示出图1所示的第三子封装400的横截面图。图8是示出图7的第三子封装400中包括的第二再分布线470的布局M3的平面图。图7是沿着图8的线X2-X2’截取的横截面图。

参照图1和图7,第三子封装400可被配置为包括第三半导体芯片410、第三中介桥430和第三密封剂450。第三半导体芯片410可充当存储由第一半导体芯片210计算的数据的存储芯片。

第三中介桥430可被设置为与第三半导体芯片410横向间隔开。第三中介桥430可以是将图1的第四子封装500垂直地电连接到图1的第二子封装300的第二中介桥330的垂直连接构件。第三中介桥430可包括设置在第三水平处的第三层通孔431、432、433和434。

第三半导体芯片410与第三层通孔431、432、433和434中的第一通孔431之间的距离可小于第三半导体芯片410与第三层通孔431、432、433和434中的第二通孔432之间的距离。第三半导体芯片410与第三层通孔431、432、433和434中的第三通孔433之间的距离可大于第三半导体芯片410与第三层通孔431、432、433和434中的第二通孔432之间的距离。第三半导体芯片410与第三层通孔431、432、433和434中的第四通孔434之间的距离可大于第三半导体芯片410与第三层通孔431、432、433和434中的第三通孔433之间的距离。

参照图7,第三子封装400的第三密封剂450可被设置为部分地覆盖第三半导体芯片410和第三中介桥430。第三密封剂450可被设置为暴露第三中介桥430的顶表面430T和第三半导体芯片410的顶表面410T。在实施方式中,尽管图中未示出,第三密封剂450可延伸以覆盖第三半导体芯片410的顶表面410T。第三密封剂450可被设置为填充第三半导体芯片410和第三中介桥430之间的间隙区域。

参照图1、图7和图8,第三子封装400还可包括第二再分布线470。第二再分布线470可以是用于将第三半导体芯片410连接到第三层通孔431、432、433和434中的第二通孔432的导电图案。第二再分布线470可延伸,使得第二再分布线470的第一部分与第三半导体芯片410的芯片焊盘417中的相应芯片焊盘交叠,并且第二再分布线470的第二部分与第二通孔432中的相应通孔交叠。因此,第二再分布线470可将第三半导体芯片410电连接到第三层通孔431、432、433和434中的第二通孔432。第二再分布线470可延伸以越过填充第三半导体芯片410和第三中介桥430之间的间隙区域的第三密封剂450的表面,并且可到达并接触第二通孔432。第二再分布线470可被设置为绕开第一通孔431以与第一通孔431电断开。

第三层通孔431、432、433和434当中的第一通孔431、第三通孔433和第四通孔434可与第二再分布线470断开,以与第三半导体芯片410电隔离。当形成第二再分布线470时,还可形成通孔焊盘479以与第三层通孔431、432、433和434当中的第一通孔431、第三通孔433和第四通孔434中的相应通孔交叠。

再参照图1和图7,第三子封装400可垂直地层叠在第二子封装300上,使得第三层通孔431、432、433和434与第二层通孔331、332、333和334中的相应通孔交叠。第三层通孔431、432、433和434可通过第二内连接器490电连接到第二层通孔331、332、333和334中的相应通孔。第二内连接器490可穿透覆盖第二再分布线470以将第二再分布线470彼此电隔离的介电层480,并且可电连接到与第一通孔431、第三通孔433和第四通孔434交叠的通孔焊盘479中的相应通孔焊盘以及与第二通孔432交叠的第二再分布线470。

再参照图2,第三半导体芯片410可通过包括第二再分布线470、第二内连接器490、第二层通孔中的第二通孔332、第一内连接器390、第一层通孔中的第二通孔232和第二水平互连图案122的电路径电连接到第一半导体芯片210。即,第一半导体芯片210和第三半导体芯片410可通过包括第二再分布线470、第二内连接器490、第二层通孔中的第二通孔332、第一内连接器390、第一层通孔中的第二通孔232和第二水平互连图案122的电路径彼此独立地通信,而与第二子封装300、第四子封装500和第五子封装600无关。尽管第三层通孔中的第一通孔431电连接到第二层通孔中的第一通孔331,但是第三层通孔中的第一通孔431可与第三半导体芯片410电断开。由于第三层通孔中的第一通孔431与第三半导体芯片410电隔离或绝缘,所以第三层通孔中的第一通孔431可被视为第三中介桥430的虚设通孔。

图9是示出图1所示的第四子封装500的横截面图。图10是示出图9的第四子封装500中包括的第三再分布线570的布局M4的平面图。图9是沿着图10的线X3-X3’截取的横截面图。

参照图1和图9,第四子封装500可被配置为包括第四半导体芯片510、第四中介桥530和第四密封剂550。第四半导体芯片510可充当存储由第一半导体芯片210计算的数据的存储芯片。

第四中介桥530可被设置为与第四半导体芯片510横向间隔开。第四中介桥530可以是将图1的第五子封装600垂直地电连接到图1的第三子封装400的第三中介桥430的垂直连接构件。第四中介桥530可包括设置在第四水平处的第四层通孔531、532、533和534。

参照图1、图2、图9和图10,第四子封装500还可包括第三再分布线570。第三再分布线570可以是用于将第四半导体芯片510连接到第四层通孔531、532、533和534中的第三通孔533的导电图案。第三再分布线570可延伸,使得第三再分布线570的第一部分与第四半导体芯片510的芯片焊盘517中的相应芯片焊盘交叠,并且第三再分布线570的第二部分与第三通孔533中的相应通孔交叠。因此,第三再分布线570可将第四半导体芯片510电连接到第四层通孔531、532、533和534中的第三通孔533。第三再分布线570可被设置为绕开第一通孔531和第二通孔532以与第一通孔531和第二通孔532电断开。

第三层通孔531、532、533和534当中的第一通孔531、第二通孔532和第四通孔534可与第三再分布线570断开,以与第四半导体芯片510电隔离。当形成第三再分布线570时,还可形成通孔焊盘579以与第四层通孔531、532、533和534当中的第一通孔531、第二通孔532和第四通孔534中的相应通孔交叠。

再参照图1和图9,第四子封装500可垂直地层叠在第三子封装400上,使得第四层通孔531、532、533和534与第三层通孔431、432、433和434中的相应通孔交叠。第四层通孔531、532、533和534可通过第三内连接器590电连接到第三层通孔431、432、433和434中的相应通孔。第三内连接器590可穿透覆盖第三再分布线570以将第三再分布线570彼此电隔离的介电层580,并且可电连接到与第一通孔531、第二通孔532和第四通孔534交叠的通孔焊盘579中的相应通孔焊盘以及与第三通孔533交叠的第三再分布线570。

再参照图2,第四半导体芯片510可通过包括第三再分布线570、第三内连接器590、第三层通孔中的第三通孔433、第二内连接器490、第二层通孔中的第三通孔333、第一内连接器390、第一层通孔中的第三通孔233和第四水平互连图案123的电路径电连接到第一半导体芯片210。即,第一半导体芯片210和第四半导体芯片510可通过包括第三再分布线570、第三内连接器590、第三层通孔中的第三通孔433、第二内连接器490、第二层通孔中的第三通孔333、第一内连接器390、第一层通孔中的第三通孔233和第四水平互连图案123的电路径彼此独立地通信,而与第二子封装300、第三子封装400和第五子封装600无关。尽管第四层通孔中的第一通孔531和第二通孔532电连接到第三层通孔中的第一通孔431和第二通孔432,但是第四层通孔中的第一通孔531和第二通孔532可与第四半导体芯片510电断开。由于第四层通孔中的第一通孔531和第二通孔532与第四半导体芯片510电隔离或绝缘,所以第四层通孔中的第一通孔531和第二通孔532可被视为第四中介桥530的虚设通孔。

图11是示出图1的第五子封装600的横截面图。图12是示出图11的第五子封装600中包括的第四再分布线670的布局M5的平面图。图11是沿着图12的线X4-X4’截取的横截面图。

参照图1和图11,第五子封装600可被配置为包括第五半导体芯片610、第五中介桥630和第五密封剂650。第五半导体芯片610可充当存储由第一半导体芯片210计算的数据的存储芯片。

第五中介桥630可被设置为与第五半导体芯片610横向间隔开。第五中介桥630可包括设置在第五水平处的第五层通孔631、632、633和634。

参照图1、图11和图12,第五子封装600还可包括第四再分布线670。第四再分布线670可以是用于将第五半导体芯片610连接到第五层通孔631、632、633和634中的第四通孔634的导电图案。第四再分布线670可延伸,使得第四再分布线670的第一部分与第五半导体芯片610的芯片焊盘617中的相应芯片焊盘交叠,并且第四再分布线670的第二部分与第四通孔634中的相应通孔交叠。因此,第四再分布线670可将第五半导体芯片610电连接到第五层通孔631、632、633和634中的第四通孔634。第四再分布线670可被设置为绕开第一至第三通孔631、632和633以与第一至第三通孔631、632和633电断开。

第四层通孔631、632、633和634当中的第一通孔631、第二通孔632和第三通孔633可与第四再分布线670断开,以与第五半导体芯片610电隔离。当形成第四再分布线670时,还可形成通孔焊盘679以与第五层通孔631、632、633和634当中的第一通孔631、第二通孔632和第三通孔633中的相应通孔交叠。

再参照图1、图11和图12,第五子封装600可垂直地层叠在第四子封装500上,使得第五层通孔631、632、633和634与第四层通孔531、532、533和534中的相应通孔交叠。第五子封装600可垂直地层叠在第四子封装500上,使得第五中介桥630与第四中介桥530交叠并对准。第一至第五子封装200、300、400、500和600可垂直地层叠在互连层100上,使得第一至第五中介桥230、330、430、530和630彼此交叠并且彼此对准。

第五层通孔631、632、633和634可通过第四内连接器690电连接到第四层通孔531、532、533和534中的相应通孔。第四内连接器690可穿透覆盖第四再分布线670以将第四再分布线670彼此电隔离的介电层680,并且可电连接到与第一通孔631、第二通孔632和第三通孔633交叠的通孔焊盘679中的相应通孔焊盘以及与第四通孔634交叠的第四再分布线670。

再参照图2,第五半导体芯片610可通过包括第四再分布线670、第四内连接器690、第四层通孔中的第四通孔534、第三内连接器590、第三层通孔中的第四通孔434、第二内连接器490、第二层通孔中的第四通孔334、第一内连接器390、第一层通孔中的第四通孔234和第五水平互连图案124的电路径电连接到第一半导体芯片210。即,第一半导体芯片210和第五半导体芯片610可通过包括第四再分布线670、第四内连接器690、第四层通孔中的第四通孔534、第三内连接器590、第三层通孔中的第四通孔434、第二内连接器490、第二层通孔中的第四通孔334、第一内连接器390、第一层通孔中的第四通孔234和第五水平互连图案124的电路径彼此独立地通信,而与第二子封装300、第三子封装400和第四子封装500无关。

尽管第五层通孔中的第一通孔631、第二通孔632和第三通孔633电连接到第四层通孔中的第一通孔531、第二通孔532和第三通孔533,但是第五层通孔中的第一通孔631、第二通孔632和第三通孔633可与第五半导体芯片610电断开。由于第五层通孔中的第一通孔631、第二通孔632和第三通孔633与第五半导体芯片610电隔离或绝缘,所以第五层通孔中的第一通孔631、第二通孔632和第三通孔633可被视为第五中介桥630的虚设通孔。

图13和图14是示出设置在图1所示的第一子封装200和第二子封装300之间的支撑件360的横截面图。

参照图13,第一内连接器390可设置在第二子封装300的第二中介桥330与第一子封装200的第一中介桥230之间,以将第二中介桥330电连接到第一中介桥230。在这种情况下,第二子封装300的第二中介桥330可被设置为面向第二半导体芯片310的第一边缘311。在第二半导体芯片310的与第一中介桥230相反的一侧可不设置中介桥。即,可不存在面向第二半导体芯片310的第二边缘312的中介桥。因此,第一内连接器390可被设置为与第二子封装300的靠近第二中介桥330的第一边缘301相邻,从而与第二中介桥330交叠。因此,在与第二子封装300的与第一边缘301相反的第二边缘302相邻的区域300E下方没有设置内连接器。因此,与第二子封装300的第二边缘302相邻的区域300E未被第一内连接器390支撑。

支撑件360可设置在第一子封装200和第二子封装300之间以支撑第二子封装300的区域300E。支撑件360可设置在第二子封装300的区域300E下方以与第一内连接器390横向间隔开。支撑件360可被设置为与第二半导体芯片310交叠。支撑件360可以与第一内连接器390一起稳定地支撑第二子封装300以防止第二子封装300倾斜。如图1所示,还可在第二至第五子封装300、400、500和600之间设置这些支撑件360。

支撑件360可附接到第二子封装300的介电层380的表面和/或第一子封装200的第一半导体芯片210的顶表面210T。支撑件360可以是虚设凸块。支撑件360可由金属材料形成。另选地,支撑件360可由诸如聚合物材料或树脂材料的绝缘材料形成。

图15是示出根据另一实施方式的半导体封装20的横截面图。

参照图15,半导体封装20可被配置为包括层叠在互连层2100上的第一子封装2200以及层叠在第一子封装2200上的第二至第五子封装2300-1、2300-2、2500-1和2500-2。半导体封装20还可包括第六密封剂2150。

图16是示出图15所示的第一子封装2200的横截面图。

参照图15和图16,第一子封装2200可被配置为包括第一半导体芯片2210、辅助半导体芯片2220(以下,称为第四半导体芯片)、第一中介桥2230和第一密封剂2250。第一半导体芯片2210可以是诸如应用处理器(AP)的处理器芯片。第四半导体芯片2220可以是缓冲存储器芯片,其提供当半导体封装20或第一半导体芯片2210操作时用作高速缓存存储器的缓冲存储器。第一中介桥2230可以是将互连层2100垂直地电连接到第二子封装2300-1的垂直连接构件。第一中介桥2230可包括设置在第一水平处的第一层通孔2231和2232。

再参照图15,第一层通孔2231和2232可被设置为彼此电隔离。互连层2100可被配置为包括介电层2110以及设置在介电层2110中的导电互连图案2120。第一水平互连图案2121和第二水平互连图案2122可设置在介电层2110中。第一水平互连图案2121可以是用于将第一层通孔2231和2232中的第一通孔2231电连接到第一半导体芯片2210的导电图案。第二水平互连图案2122可以是用于将第一层通孔2231和2232中的第二通孔2232电连接到第一半导体芯片2210的导电图案。第一水平互连图案2121和第二水平互连图案2122可提供用于将第一通孔2231和第二通孔2232电连接到第一半导体芯片2210的独立路径。

外连接器2130可附接到互连层2100。互连层2100还可包括将第一半导体芯片210电连接到外连接器2130的垂直互连图案2125。互连层100还可包括将第一半导体芯片210电连接到第四半导体芯片2220的第三水平互连图案2126。

图17是示出图15所示的第二子封装2300-1的横截面图。图18是示出图17所示的第二子封装2300-1的第一再分布线2370-1的布局M6的平面图。图17是沿着图18的线X5-X5’截取的横截面图。

参照图15、图17和图18,第二子封装2300-1和第三子封装2300-2可具有相同的配置。第二子封装2300-1(或第三子封装2300-2)可被配置为包括第二半导体芯片2310-1(或2310-2)、第二中介桥2330-1(或2330-2)和第二密封剂2350-1(或2350-2)。第二半导体芯片2310-1(或2310-2)可充当存储由第一半导体芯片2210计算的数据的存储芯片。

第二半导体芯片2310-1(或2310-2)可以是具有与参照图5描述的第二半导体芯片310基本上相同的配置的半导体芯片。第二半导体芯片2310-1(或2310-2)可具有面向第二中介桥2330-1(或2330-2)的第一边缘2311以及与第一边缘2311相反的第二边缘2312,如图18所示。第二半导体芯片2310-1(或2310-2)可被配置为包括芯片焊盘2317-1(或2317-2),并且芯片焊盘2317-1(或2317-2)可排列为使得第一边缘2311与芯片焊盘2317-1(或2317-2)之间的距离小于第二边缘2312与芯片焊盘2317-1(或2317-2)之间的距离。

第二中介桥2330-1(或2330-2)可包括第二层通孔2331-1(或2331-2)和2332-1(或2332-2)。第二半导体芯片2310-1(或2310-2)的第一边缘2311与第一通孔2331-1(或2331-2)之间的距离可小于第一边缘2311与第二通孔2332-1(或2332-2)之间的距离。

第二子封装2300-1(或第三子封装2300-2)还可包括第一再分布线2370-1(或2370-2)。第一再分布线2370-1(或2370-2)可以是将第二半导体芯片2310-1(或2310-2)的芯片焊盘2317-1(或2317-2)连接到第一通孔2331-1(或2331-2)的导电图案。第二通孔2332-1(或2332-2)可与第一再分布线2370-1(或2370-2)断开以与第二半导体芯片2310-1(或2310-2)电隔离。

再参照图15和图18,第二子封装2300-1可垂直地层叠在第一子封装2200上,使得第二中介桥2330-1的第二层通孔2331-1和2332-1与第一中介桥2230的第一层通孔2231和2232中的相应通孔交叠。第三子封装2300-2可垂直地层叠在第二子封装2300-1上,使得第二中介桥2330-2的第二层通孔2331-2和2332-2电连接到第二中介桥2330-1的第二层通孔2331-1和2332-1中的相应通孔。

第一子封装2200和第二子封装2300-1可通过内连接器2390彼此电连接,并且第二子封装2300-1和第三子封装2300-2也可通过内连接器2390彼此电连接。支撑件2360可设置在第一子封装2200和第二子封装2300-1之间,使得第二子封装2300-1由支撑件2360和内连接器2390稳定地支撑。

第二子封装2300-1的第二半导体芯片2310-1可通过包括第一再分布线2370-1、内连接器2390、第一层通孔2231和2232中的第一通孔2231和第一水平互连图案2121的电路径电连接到第一半导体芯片2210。

第三子封装2300-2的第二半导体芯片2310-2可通过包括第一再分布线2370-2、内连接器2390、第二层通孔2231-1和2232-1中的第一通孔2331-1、内连接器2390、第一层通孔2231和2232中的第一通孔2231和第一水平互连图案2121的电路径电连接到第一半导体芯片2210。

第二子封装2300-1的第二半导体芯片2310-1和第三子封装2300-2的第二半导体芯片2310-2可共同使用包括第一层通孔中的第一通孔2231和互连层2100的第一水平互连图案2121的电路径电连接到第一半导体芯片2210。即,第二子封装2300-1的第二半导体芯片2310-1和第三子封装2300-2的第二半导体芯片2310-2可通过包括第一通孔2231和第一水平互连图案2121的公共电路径仅与第一半导体芯片2210通信,而与第四子封装2500-1和第五子封装2500-2无关。

图19是示出图15所示的第四子封装2500-1的横截面图。图20是示出图19所示的第四子封装2500-1的第二再分布线2570-1的布局M7的平面图。图19是沿着图20的线X6-X6’截取的横截面图。

参照图15、图19和图20,第四子封装2500-1和第五子封装2500-2可具有相同的配置。第四子封装2500-1(或第五子封装2500-2)可被配置为包括第三半导体芯片2510-1(或2510-2)、第三中介桥2530-1(或2530-2)和第三密封剂2550-1(或2550-2)。第三半导体芯片2510-1(或2510-2)可充当存储由第一半导体芯片2210计算的数据的存储芯片。第三半导体芯片2510-1(或2510-2)可具有与第二半导体芯片2310-1(或2310-2)基本上相同的配置。

第三中介桥2530-1(或2330-2)可包括第三层通孔2531-1(或2531-2)和2532-1(或2532-2)。第四子封装2500-1(或第五子封装2500-2)还可包括第二再分布线2570-1(或2570-2)。第二再分布线2570-1(或2570-2)可以是用于将第三半导体芯片2510-1(或2510-2)的芯片焊盘2517-1(或2517-2)连接到第三层通孔中的第二通孔2532-1(或2532-2)的导电图案。第三层通孔中的第一通孔2531-1(或2531-2)可与第二再分布线2570-1(或2570-2)断开,以与第三半导体芯片2510-1(或2510-2)电隔离。第二再分布线2570-1(或2570-2)可被设置为绕开第一通孔2531-1(或2531-2)以与第一通孔2531-1(或2531-2)电断开。

再参照图15和图20,第四子封装2500-1可垂直地层叠在第三子封装2300-2上,使得第三中介桥2530-1的第三层通孔2531-1和2532-1与第二中介桥2330-2的第二层通孔2331-2和2332-2中的相应通孔交叠。第五子封装2500-2可垂直地层叠在第四子封装2500-1上,使得第三中介桥2530-2的第三层通孔2531-2和2532-2电连接到第三中介桥2530-1的第三层通孔2531-1和2532-1中的相应通孔。

第三子封装2300-2和第四子封装2500-1可通过内连接器2390彼此电连接,并且第四子封装2500-1和第五子封装2500-2也可通过内连接器2390彼此电连接。支撑件2360可设置在第三子封装2300-2和第四子封装2500-1之间,使得第四子封装2500-1由支撑件2360和内连接器2390稳定地支撑。

第四子封装2500-1的第三半导体芯片2510-1可通过包括第二再分布线2570-1、内连接器2390、第二层通孔中的第二通孔2332-2、内连接器2390、第二层通孔中的第二通孔2332-1、内连接器2390、第一层通孔中的第二通孔2232和第二水平互连图案2122的电路径电连接到第一半导体芯片2210。

第五子封装2500-2的第三半导体芯片2510-2可通过包括第二再分布线2570-2、内连接器2390、第三层通孔中的第二通孔2532-1、内连接器2390、第二层通孔中的第二通孔2332-2、内连接器2390、第二层通孔中的第二通孔2332-1、内连接器2390、第一层通孔中的第二通孔2332和第二水平互连图案2122的电路径电连接到第一半导体芯片2210。

第四子封装2500-1的第三半导体芯片2510-1和第五子封装2500-2的第三半导体芯片2510-2可共同使用包括第二层通孔中的第二通孔2332-2、内连接器2390、第二层通孔中的第二通孔2332-1、内连接器2390、第一层通孔中的第二通孔2332和第二水平互连图案2122的电路径电连接到第一半导体芯片2210。即,第四子封装2500-1的第三半导体芯片2510-1和第五子封装2500-2的第三半导体芯片2510-2可通过包括第二层通孔中的第二通孔2332-2、内连接器2390、第二层通孔中的第二通孔2332-1、内连接器2390、第一层通孔中的第二通孔2332和第二水平互连图案2122的公共电路径仅与第一半导体芯片2210通信,而与第二子封装2300-1和第三子封装2300-2无关。

图21是示出根据另一实施方式的半导体封装30的平面图。

参照图21,半导体封装30可被配置为包括第一子封装3200以及层叠在第一子封装3200上的第一层叠物3300-1和第二层叠物3300-2。第一层叠物3300-1和第二层叠物3300-2可在第一子封装3200上并排设置,以彼此横向间隔开。

第一子封装3200可具有与图1所示的第一子封装200基本上相同的配置。第一子封装3200可被配置为包括第一半导体芯片3210、第一中介桥3230和第四半导体芯片3240。第一子封装3200可层叠在互连层3100上。互连层3100可具有与图1所示的互连层100基本上相同的配置。第一子封装3200可具有与图1所示的第一子封装200基本上相同的配置。第一半导体芯片3210、第一中介桥3230和第四半导体芯片3240可分别具有与图1所示的第一半导体芯片210、第一中介桥230和第六半导体芯片220基本上相同的配置。第一层叠物3300-1可被配置为具有与图1所示的第二至第五子封装300、400、500和600的层叠物基本上相同的层叠结构。另外,第二层叠物3300-2也可被配置为具有与图1所示的第二至第五子封装300、400、500和600的层叠物基本上相同的层叠结构。

互连层3100可包括与图1所示的互连层100中包括的第三水平互连图案126对应的第三水平互连图案(未示出),以用于第一半导体芯片3210和第四半导体芯片3240之间的通信。

第一半导体芯片3210可以是应用处理器(AP),并且第四半导体芯片3240可以是缓冲存储器芯片。具有至少256个路径或至少512个路径的宽输入/输出(I/O)路径可设置在第一半导体芯片3210和第四半导体芯片3240之间,以用于第一半导体芯片3210和第四半导体芯片3240之间的通信。为了建立宽I/O路径,互连层3100的第三水平互连图案可包括至少256个导电图案或至少512个导电图案。可通过宽I/O路径改进第一半导体芯片3210与第四半导体芯片3240之间的信号或数据传输速度。

当第一层叠物3300-1被配置为包括第二至第五子封装(图1的300、400、500和600)时,第一半导体芯片3210和第一层叠物3300-1可通过至少64个I/O路径彼此通信。由于第一层叠物3300-1或第二层叠物3300-2中包括的子封装300、400、500和600中的每一个与第一半导体芯片3210独立地通信,所以第一、第二、第四和第五水平互连图案(图1的121、122、123和124)中的每一个可包括16个导电图案。因此,可通过宽I/O路径改进第一半导体芯片3210与第一层叠物3300-1(或第二层叠物3300-2)之间的信号或数据传输速度。

在实施方式中,半导体封装30的第一子封装3200可具有与图15所示的第一子封装2200基本上相同的配置。第一层叠物3300-1和第二层叠物3300-2中的每一个可具有与第二至第五子封装2300-1、2300-2、2500-1和2500-2的层叠物基本上相同的配置。

再参照图1,半导体封装10可被配置为包括层叠在互连层100上的第一子封装200以及依次层叠在第一子封装200上的第二子封装300和第三子封装400。第一至第三子封装200、300和400可被配置为分别包括第一半导体芯片210、第二半导体芯片310和第三半导体芯片410。另外,第一至第三子封装200、300和400可被配置为分别包括第一中介桥230、第二中介桥330和第三中介桥430。中介桥230、330和430可包括第一通孔231、331和431以及第二通孔232、332和432。

第二子封装300还可包括将第二子封装300的半导体芯片310电连接到第一通孔231、331和431的第一再分布线370,并且第三子封装400还可包括将第三子封装400的半导体芯片410电连接到第二通孔232、332和432的第二再分布线470。

图22是示出包括采用根据实施方式的半导体封装中的至少一个的存储卡7800的电子系统的框图。存储卡7800包括诸如非易失性存储器装置的存储器7810以及存储控制器7820。存储器7810和存储控制器7820可存储数据或读出所存储的数据。存储器7810和存储控制器7820中的至少一个可包括根据实施方式的半导体封装中的至少一个。

存储器7810可包括应用了本公开的实施方式的技术的非易失性存储器装置。存储控制器7820可控制存储器7810,使得响应于来自主机7830的读/写请求,读出所存储的数据或者存储数据。

图23是示出包括根据实施方式的半导体封装中的至少一个的电子系统8710的框图。电子系统8710可包括控制器8711、输入/输出装置8712和存储器8713。控制器8711、输入/输出装置8712和存储器8713可通过提供数据移动的路径的总线8715彼此联接。

在实施方式中,控制器8711可包括一个或更多个微处理器、数字信号处理器、微控制器和/或能够执行与这些组件相同的功能的逻辑器件。控制器8711或存储器8713可包括根据本公开的实施方式的半导体封装中的至少一个。输入/输出装置8712可包括选自键区、键盘、显示装置、触摸屏等中的至少一个。存储器8713是用于存储数据的装置。存储器8713可存储要由控制器8711执行的数据和/或命令等。

存储器8713可包括诸如DRAM的易失性存储器装置和/或诸如闪存的非易失性存储器装置。例如,闪存可被安装到诸如移动终端或台式计算机的信息处理系统。闪存可构成固态盘(SSD)。在这种情况下,电子系统8710可在闪存系统中稳定地存储大量数据。

电子系统8710还可包括被配置为向通信网络发送数据以及从通信网络接收数据的接口8714。接口8714可为有线或无线型。例如,接口8714可包括天线或者有线或无线收发器。

电子系统8710可被实现为移动系统、个人计算机、工业计算机或者执行各种功能的逻辑系统。例如,移动系统可以是个人数字助理(PDA)、便携式计算机、平板计算机、移动电话、智能电话、无线电话、膝上型计算机、存储卡、数字音乐系统和信息发送/接收系统中的任一个。

如果电子系统8710是能够执行无线通信的设备,则电子系统8710可用在使用CDMA(码分多址)、GSM(全球移动通信系统)、NADC(北美数字蜂窝)、E-TDMA(增强时分多址)、WCDMA(宽带码分多址)、CDMA2000、LTE(长期演进)或Wibro(无线宽带互联网)的技术的通信系统中。

结合如上所述的一些实施方式公开了本发明构思。本领域技术人员将理解,在不脱离本公开的范围和精神的情况下,可进行各种修改、添加和替换。因此,本说明书中公开的实施方式不应从限制性角度而应从例示性角度理解。本发明构思的范围不限于以上描述,而是由所附权利要求限定,等同范围内的所有不同特征应该被解释为包括在本发明构思中。

相关申请的交叉引用

本申请要求2019年12月24日提交的韩国申请No.10-2019-0174561的优先权,其整体通过引用并入本文。

- 包括具有中介桥的层叠子封装的半导体封装

- 包括具有中介桥的层叠的模块的半导体封装