多通道数据采集电路板及具有其的数据采集同步系统

文献发布时间:2023-06-19 11:35:49

技术领域

本公开涉及高速数据采集技术领域,尤其涉及一种多通道数据采集电路板及具有其的数据采集同步系统。

背景技术

目前在军用相控阵雷达、数字波束合成数字侦查、数据监听、数据链等军用相关领域以及量子计算、数字低电平系统、射电望远镜阵列等科学实验装备领域,对高速ADC、DAC的多通道分布式同步均有强烈需求。

在支持JESD204B协议的ADC、DAC芯片出现之前,同步大规模的多通道ADC、DAC,对硬件系统的指标一致性要求、温度漂移要求等均非常高,设计的系统往往比较脆弱,需要时常维护以确保系统同步特性相关指标满足要求。而且随着ADC、DAC芯片工作速率的提升,同步难度越来越大,硬件成本也越来越高。在支持JESD204B协议相关规范的ADC、DAC以及时钟芯片出现之后,同步大规模的多通道ADC、DAC变的容易很多,尤其针对工作速率在1Gsps以上的ADC、DAC进行同步时,如果采用ADC、DAC以及配套时钟芯片厂家建议的方案时,整个系统的同步的很多必要调节测试工作均由ADC、DAC以及配套时钟芯片提供,设计人员只需要关注必要的高速时钟分配、同步脉冲分配网络的信号质量以及等长即可。系统的设计、调试与维护的成本大大的降低了。但是须使用差分信号传输时钟、同步脉冲信号,每个模块至少需要采用4根射频线进行同步,线缆使用数量较多。

发明内容

有鉴于此,本公开提出了一种多通道数据采集电路板,包括:具有时钟抖动清除功能的时钟芯片、晶体振荡器、FPGA芯片、通信模块和协议芯片;

所述时钟芯片的频率输入端与所述晶体振荡器的输出端电连接;

所述时钟芯片的第一输入端与所述时钟芯片的第一输出端电连接作为所述时钟芯片的反馈补偿;

所述时钟芯片的第二输入端适用于电连接级联输出端;

所述时钟芯片的第二输出端适用于电连接级联输入端;

所述时钟芯片的第三输出端与所述FPGA芯片的输入端电连接;

所述FPGA芯片的输入输出端与所述通信模块的第一输入输出端通信连接;

所述通信模块的第二输入输出端适用于与控制设备通信连接;

所述时钟芯片的第四输出端与所述协议芯片电连接;

所述协议芯片适用于与ADC芯片和DAC芯片电连接;

所述晶体振荡器,被配置为对所述时钟芯片提供基础频率;

所述时钟芯片,被配置为向所述FPGA芯片、所述ADC芯片和所述DAC芯片提供时钟频率;

所述FPGA芯片,被配置为通过所述控制设备对所述时钟芯片和协议芯片进行配置;

所述协议芯片,被配置为通过JESD204B协议与ADC芯片和DAC芯片进行数据传输。

在一种可能的实现方式中,所述通信模块为PHY芯片;

所述PHY芯片的第一输入输出端与所述FPGA芯片的输入输出端通信连接;

所述PHY芯片的第二输入输出端电连接有网口;

所述网口适用于与所述控制设备有线通信连接。

在一种可能的实现方式中,所述通信模块为WIFI芯片;

所述WIFI芯片的第一输入输出端与所述FPGA芯片的输入输出端通信连接;

所述WIFI芯片的第二输入输出端电连接有天线;

所述天线适用于与所述控制设备无线通信连接。

在一种可能的实现方式中,所述通信模块为串口;

所述串口的第一输入输出端与所述FPGA芯片的输入输出端通信连接;

所述串口的第二输入输出端适用于所述控制设备通信连接。

在一种可能的实现方式中,还包括第一连接器、第二连接器、第三连接器和第四连接器;

所述第一连接器设置在所述时钟芯片的第一输入端;

所述第二连接器设置在所述时钟芯片的第二输入端;

所述第三连接器设置在所述时钟芯片的第一输出端;

所述第四连接器设置在所述时钟芯片的第二输入端。

在一种可能的实现方式中,所述第一连接器与所述第三连接器通过射频电缆连接。

在一种可能的实现方式中,还包括锁相环芯片;

所述锁相环芯片的输入端与所述时钟芯片的第五输出端电连接;

所述锁相环芯片的输出端适用于与ADC芯片和DAC芯片电连接;

所述锁相环芯片用于在时钟频率大于3.2GHz时。

在一种可能的实现方式中,还包括时钟扇出器;

所述时钟扇出器的输入端与所述锁相环芯片的输出端电连接;

所述时钟扇出器的输出端适用于电连接多片所述ADC芯片和所述多片DAC芯片。

在一种可能的实现方式中,所述锁相环芯片的配置端与所述FPGA芯片的输出端电连接。

根据本公开的另一方面,提供了一种数据采集同步系统,其特征在于,包括前面任一所述的多通道数据采集电路板。

通过包括具有时钟抖动清除功能的时钟芯片、晶体振荡器、FPGA芯片、通信模块和协议芯片,时钟芯片的频率输入端与晶体振荡器的输出端电连接,时钟芯片的第一输入端与时钟芯片的第一输出端电连接作为时钟芯片的反馈补偿,时钟芯片的第二输入端适用于电连接级联输出端,时钟芯片的第二输出端适用于电连接级联输入端,时钟芯片的第三输出端与FPGA芯片的输入端电连接,FPGA芯片的输入输出端与通信模块的第一输入输出端通信连接,通信模块的第二输入输出端适用于与控制设备通信连接,时钟芯片的第四输出端与协议芯片电连接,协议芯片适用于与ADC芯片和DAC芯片电连接,晶体振荡器,被配置为对时钟芯片提供基础频率,时钟芯片,被配置为向FPGA芯片、ADC芯片和DAC芯片提供时钟频率,FPGA芯片,被配置为通过控制设备对时钟芯片和协议芯片进行配置,协议芯片,被配置为通过JESD204B协议与ADC芯片和DAC芯片进行数据传输。这样,在第二输出端和第二输入端进行同步链接,从而仅需要两根线缆就可与其他电路板进行同步,减少了线材使用,节省了成本且有利于大规模部署。

根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

附图说明

包含在说明书中并且构成说明书的一部分的附图与说明书一起示出了本公开的示例性实施例、特征和方面,并且用于解释本公开的原理。

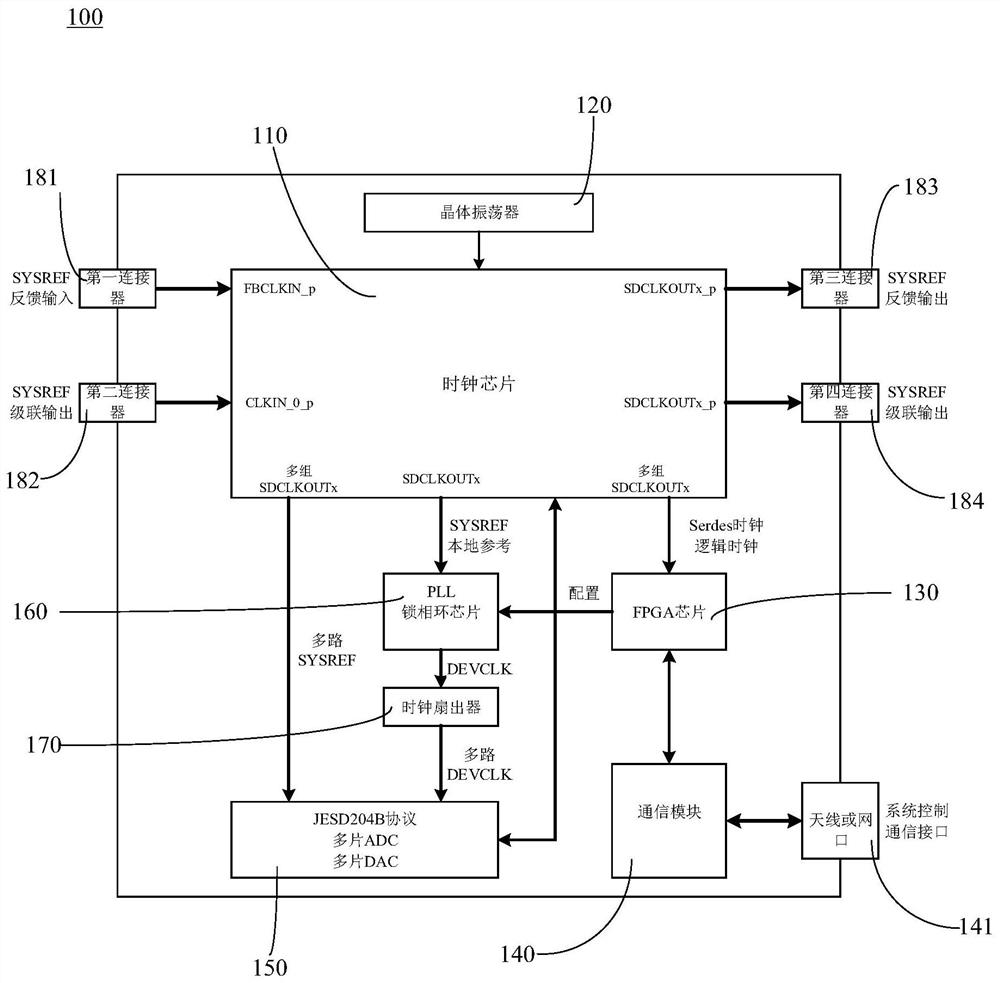

图1示出本公开实施例的多通道数据采集电路板的示意图;

图2示出本公开实施例的数据采集同步系统的示意图。

具体实施方式

以下将参考附图详细说明本公开的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。

另外,为了更好的说明本公开,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本公开同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本公开的主旨。

图1示出根据本公开一实施例的多通道数据采集电路板100的示意图。如图1所示,该多通道数据采集电路板100包括:

具有时钟抖动清除功能的时钟芯片110、晶体振荡器120、FPGA芯片130、通信模块140和协议芯片150,时钟芯片110的频率输入端与晶体振荡器120的输出端电连接,时钟芯片110的第一输入端与时钟芯片110的第一输出端电连接作为时钟芯片110的反馈补偿,时钟芯片110的第二输入端适用于电连接级联输出端,时钟芯片110的第二输出端适用于电连接级联输入端,时钟芯片110的第三输出端与FPGA芯片130的输入端电连接,FPGA芯片130的输入输出端与通信模块140的第一输入输出端通信连接,通信模块140的第二输入输出端适用于与控制设备通信连接,时钟芯片110的第四输出端与协议芯片150电连接,协议芯片150适用于与ADC芯片和DAC芯片电连接,晶体振荡器120,被配置为对时钟芯片110提供基础频率,时钟芯片110,被配置为向FPGA芯片130、ADC芯片和DAC芯片提供时钟频率,FPGA芯片130,被配置为通过控制设备对时钟芯片110和协议芯片150进行配置,协议芯片150,被配置为通过JESD204B协议与ADC芯片和DAC芯片进行数据传输。

通过包括具有时钟抖动清除功能的时钟芯片110、晶体振荡器120、FPGA芯片130、通信模块140和协议芯片150,时钟芯片110的频率输入端与晶体振荡器120的输出端电连接,时钟芯片110的第一输入端与时钟芯片110的第一输出端电连接作为时钟芯片110的反馈补偿,时钟芯片110的第二输入端适用于电连接级联输出端,时钟芯片110的第二输出端适用于电连接级联输入端,时钟芯片110的第三输出端与FPGA芯片130的输入端电连接,FPGA芯片130的输入输出端与通信模块140的第一输入输出端通信连接,通信模块140的第二输入输出端适用于与控制设备通信连接,时钟芯片110的第四输出端与协议芯片150电连接,协议芯片150适用于与ADC芯片和DAC芯片电连接,晶体振荡器120,被配置为对时钟芯片110提供基础频率,时钟芯片110,被配置为向FPGA芯片130、ADC芯片和DAC芯片提供时钟频率,FPGA芯片130,被配置为通过控制设备对时钟芯片110和协议芯片150进行配置,协议芯片150,被配置为通过JESD204B协议与ADC芯片和DAC芯片进行数据传输。这样,在第二输出端和第二输入端进行同步链接,从而仅需要两根线缆就可与其他电路板进行同步,减少了线材使用,节省了成本且有利于大规模部署。

具体的,参见图1,在一种可能的实现方式中,通信模块140为PHY芯片,PHY芯片的第一输入输出端与FPGA芯片130的输入输出端通信连接,PHY芯片的第二输入输出端电连接有网口,网口适用于与控制设备有线通信连接。举例来说,网口为RJ45网口,通过双绞线网线将本电路板与计算机(控制设备)进行连接,计算机可以下发配置到FPGA芯片130,从而对电路板中的各个芯片进行配置。有线连接稳定性高。

进一步的,参见图1,在一种可能的实现方式中,通信模块140为WIFI芯片,WIFI芯片的第一输入输出端与FPGA芯片130的输入输出端通信连接,WIFI芯片的第二输入输出端电连接有天线141,天线141适用于与控制设备无线通信连接。举例来说,WiFi芯片支持2.4GHz频率,同时天线141为单天线141,计算机为控制设备,相应的计算机也配置有无线网卡,这样就可以实现计算机可以下发配置到FPGA芯片130,从而对电路板中的各个芯片进行配置。无线连接减少线材消耗,减少成本。

进一步的,参见图1,在另一种可能的实现方式中,通信模块140为串口,串口的第一输入输出端与FPGA芯片130的输入输出端通信连接,串口的第二输入输出端适用于控制设备通信连接。也就是说,还可以使用带有串口的控制设备通过串口下发配置到FPGA芯片130,从而对电路板中的各个芯片进行配置。

需要说明的是,可以单独配置一种通信模块140,也就是网线连接,无线连接和串口中的任意一种,也可以同时配置多种通信模块140,也就是包括网线连接,无线连接和串口三种方式。另外,还可以包括其他连接方式,本公开不进行限定。

进一步的,参见图1,在一种可能的实现方式中,还包括第一连接器181、第二连接器182、第三连接器183和第四连接器184,第一连接器181设置在时钟芯片110的第一输入端,第二连接器182设置在时钟芯片110的第二输入端,第三连接器183设置在时钟芯片110的第一输出端,第四连接器184设置在时钟芯片110的第二输入端,举例来说,第一连接器181与第三连接器183通过射频电缆连接,为时钟芯片110提供了参考反馈补偿,同时通过射频线缆接入第一电路板的级联输出端到时钟芯片110的第二连接器182,通过射频线缆接入第二电路板的级联输入端到时钟芯片110的第四连接器184,这样是用两根等长的电缆就实现了与其他电路板进行同步。

进一步的,参见图1,在一种可能的实现方式中,还包括锁相环芯片160,锁相环芯片160的输入端与时钟芯片110的第五输出端电连接,锁相环芯片160的输出端适用于与ADC芯片和DAC芯片电连接,锁相环芯片160用于在时钟频率大于3.2GHz时。举例来说,时钟芯片110为LMK04828芯片,锁相环芯片160可以为LMX2594芯片,也就是说,对于3.2GHz频率以上进行处理时,因为时钟芯片110的时钟频率的倍频速率不够高,所以添加PLL芯片(锁相环芯片160),从而提高输出的时钟频率,如果是3.2GHz以内,LMK04828可以达到要求,不用添加PLL芯片。

进一步的,参见图1,在一种可能的实现方式中,还包括时钟扇出器170,时钟扇出器170的输入端与锁相环芯片160的输出端电连接,时钟扇出器170的输出端适用于电连接多片ADC芯片和多片DAC芯片。也就是说,在连接多片ADC芯片和DAC芯片时,需要使用到时钟扇出器170,这样从锁相环芯片160接入的时钟信号可以分为多路信号分别输入到各ADC芯片和DAC芯片中。

进一步的,参见图1,在一种可能的实现方式中,锁相环芯片160的配置端与FPGA芯片130的输出端电连接。举例来说,通信模块140为PHY芯片,PHY芯片的第一输入输出端与FPGA芯片130的输入输出端通信连接,PHY芯片的第二输入输出端电连接有网口,网口适用于与控制设备有线通信连接。其中,网口为RJ45网口,通过双绞线网线将本电路板与计算机(控制设备)进行连接,计算机可以下发配置到FPGA芯片130,从而对电路板中的各个芯片进行配置,其中就包括PLL芯片。

需要说明的是,尽管以上述各个实施例作为示例介绍了本公开的多通道数据采集电路板100如上,但本领域技术人员能够理解,本公开应不限于此。事实上,用户完全可根据个人喜好和/或实际应用场景灵活设定多通道数据采集电路板100,只要达到所需功能即可。

这样,通过包括具有时钟抖动清除功能的时钟芯片110、晶体振荡器120、FPGA芯片130、通信模块140和协议芯片150,时钟芯片110的频率输入端与晶体振荡器120的输出端电连接,时钟芯片110的第一输入端与时钟芯片110的第一输出端电连接作为时钟芯片110的反馈补偿,时钟芯片110的第二输入端适用于电连接级联输出端,时钟芯片110的第二输出端适用于电连接级联输入端,时钟芯片110的第三输出端与FPGA芯片130的输入端电连接,FPGA芯片130的输入输出端与通信模块140的第一输入输出端通信连接,通信模块140的第二输入输出端适用于与控制设备通信连接,时钟芯片110的第四输出端与协议芯片150电连接,协议芯片150适用于与ADC芯片和DAC芯片电连接,晶体振荡器120,被配置为对时钟芯片110提供基础频率,时钟芯片110,被配置为向FPGA芯片130、ADC芯片和DAC芯片提供时钟频率,FPGA芯片130,被配置为通过控制设备对时钟芯片110和协议芯片150进行配置,协议芯片150,被配置为通过JESD204B协议与ADC芯片和DAC芯片进行数据传输。这样,在第二输出端和第二输入端进行同步链接,从而仅需要两根线缆就可与其他电路板进行同步,减少了线材使用,节省了成本且有利于大规模部署。

根据本公开的另一方面,参见图2,提供了一种数据采集同步系统200,其特征在于,包括前面任一所述的多通道数据采集电路板100。其中,可以同步多个多通道数据采集电路板100,即,模块1、模块2和模块3均为一个多通道数据采集电路板100,若干模块中还可以包括任意数量的多通道数据采集电路板100,直至连接X个多通道数据采集电路板100,每个多通道数据采集电路板100仅需要两根线缆就可与其他电路板进行同步,减少了线材使用,节省了成本且有利于大规模部署。

以上已经描述了本公开的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。

- 多通道数据采集电路板及具有其的数据采集同步系统

- 多通道数据采集终端及分布式数据采集同步系统