半导体器件

文献发布时间:2023-06-19 11:39:06

技术领域

本发明涉及半导体器件。

背景技术

搭载有多个MOSFET(metal-oxide-semiconductor field-effect transistor:金属氧化物半导体场效应晶体管)等的功率半导体元件,用于电源装置等的功率用半导体器件的需求正在增加。在专利文献1中公开了现有技术的半导体器件的一例。该文献中公开的半导体器件,在绝缘基板的一个面设置导体图案,使各半导体元件的背面电极与导体图案接合,将多个半导体元件搭载在绝缘基板中。

半导体器件的表面积(与厚度方向正交的面的面积),为了能够搭载在更狭窄的区域中而被要求形成得小。因此,搭载在半导体器件的半导体元件的表面积也需要形成得小。MOSFET的情况下,存在表面积越小导通电阻越变大的问题。

现有技术文献

专利文献

专利文献1:日本特开2010-245212号公报

发明内容

发明要解决的问题

鉴于上述的情况,本发明的目的在于,提供能够抑制被搭载的半导体元件的表面积变小的半导体器件。

用于解决问题的技术手段

本发明提供的半导体器件,其具有第一半导体元件和第二半导体元件,各半导体元件具有元件主面和元件背面,并且具有配置在上述元件背面的元件第一电极和配置在上述元件主面的元件第二电极。另外,半导体器件包括:具有引线主面和引线背面的第一引线;覆盖上述第一引线、上述第一半导体元件和上述第二半导体元件的绝缘层;与上述第一半导体元件的上述元件第二电极导通的第一电极;和与上述第一引线导通的第二电极。上述第一半导体元件和上述第一引线以上述第一半导体元件的上述元件背面与上述引线主面相对的姿态接合在一起。上述第二半导体元件和上述第一引线以上述第二半导体元件的上述元件背面与上述引线背面相对的姿态接合在一起。

发明效果

本发明的半导体器件中,第一半导体元件搭载于第一引线的引线主面,第二半导体元件搭载于第一引线的引线背面。因此,与第一半导体元件和第二半导体元件排列搭载于第一引线的相同面的情况相比,能够增大各半导体元件的表面积。

本发明其他特征和优点,通过参照附图在以下进行的详细说明中能够更加明确。

附图说明

图1是表示本发明的第一实施方式的半导体器件的立体图。

图2是图1所示的半导体器件的电路图。

图3是表示图1所示的半导体器件的示意性的截面的图。

图4是使图1所示的半导体器件的一部分透过的俯视图。

图5是使图1所示的半导体器件的一部分透过的俯视图。

图6是使图1所示的半导体器件的一部分透过的俯视图。

图7是说明图1所示的半导体器件的制造工序的俯视图。

图8是说明图1所示的半导体器件的制造工序的俯视图。

图9是表示说明图1所示的半导体器件的制造工序的示意性的截面的图。

图10是表示说明图1所示的半导体器件的制造工序的示意性的截面的图。

图11是表示说明图1所示的半导体器件的制造工序的示意性的截面的图。

图12是表示说明图1所示的半导体器件的制造工序的示意性的截面的图。

图13是表示说明图1所示的半导体器件的制造工序的示意性的截面的图。

图14是表示说明图1所示的半导体器件的制造工序的示意性的截面的图。

图15是表示本发明的第二实施方式的半导体器件的示意性的截面的图。

图16是表示本发明的第三实施方式的半导体器件的示意性的截面的图。

图17是表示本发明的第四实施方式的半导体器件的示意性的截面的图。

图18是表示本发明的第五实施方式的半导体器件的电路图。

图19是表示图18所示的半导体器件的示意性的截面的图。

图20是使图18所示的半导体器件的一部分透过的俯视图。

图21是使图18所示的半导体器件的一部分透过的俯视图。

图22是表示本发明的第六实施方式的半导体器件的电路图。

图23是表示图22所示的半导体器件的示意性的截面的图。

图24是表示本发明的第七实施方式的半导体器件的电路图。

图25是表示本发明的第八实施方式的半导体器件的电路图。

图26是表示本发明的第九实施方式的半导体器件的示意性的截面的图。

具体实施方式

以下,参照附图具体地说明本发明的优选的实施方式。

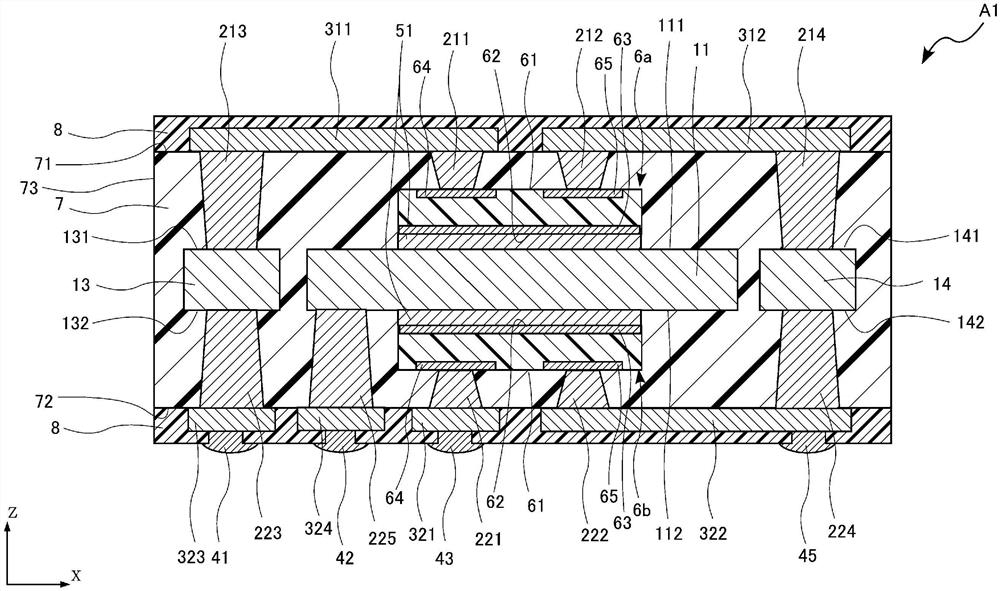

基于图1~图6,关于本发明的第一实施方式的半导体器件A1进行说明。半导体器件A1包括第一引线11、第三引线13、第四引线14、通孔211~214、221~225、配线图案311、312、321~324、第一电极41、第二电极42、第三电极43、第五电极45、导电性接合层51、半导体元件6a、6b、绝缘层7和绝缘膜8。

图1是表示半导体器件A1的立体图。图2是表示半导体器件A1的电路图。图3是表示半导体器件A1的示意性的截面的图,以容易理解导通路径的方式表示了各部材。此外,实际上,各通孔与各配线图案形成一体,在图3中为了区别,作为不同的部件标注了不同的斜线。图4~图6是表示半导体器件A1的俯视图,分别使一部分透过。在图4中,使上侧(图3中的上侧)的绝缘膜8透过。在图5中,使上侧的绝缘膜8、配线图案311、312和绝缘层7透过。在图6中,使上侧的绝缘膜8、配线图案311、312、绝缘层7、通孔211~214、第一引线11、第三引线13和第四引线14透过。

在这些图中表示的半导体器件A1是被表面安装于各种设备的电路基板。半导体器件A1的厚度方向看的形状为矩形形状。为了说明的方便,设半导体器件A1的厚度方向为z方向,与z方向正交的沿着半导体器件A1的一个边的方向为x方向,与z方向和x方向正交的方向为y方向。在以下的图中也是同样的。半导体器件A1的各尺寸没有特别的限定,在本实施方式中,例如x方向尺寸为2~6mm程度,y方向尺寸为2~6mm程度、z方向尺寸为0.5~1mm程度。

第一引线11支承半导体元件6a、6b,并且与半导体元件6a、6b导通。第三引线13与半导体元件6a导通。第四引线14与半导体元件6a、6b导通。第一引线11、第三引线13和第四引线14通过对金属板实施冲孔加工或蚀刻处理等而形成。第一引线11、第三引线13和第四引线14由金属构成,优选由Cu和Ni的任意者、或者它们的合金或42合金等构成。本实施方式中,第一引线11、第三引线13和第四引线14由Cu形成。第一引线11、第三引线13和第四引线14的厚度例如为0.08~0.3mm,在本实施方式中为0.15mm程度。此外,第一引线11、第三引线13和第四引线14的材料和厚度没有限定。

如图5所示,第一引线11在z方向看时配置在半导体器件A1的中央。第三引线13在半导体器件A1的图5中的左下的端部与第一引线11分开地配置。第四引线14在半导体器件A1的图5中的右上的端部与第一引线11分开地配置。此外,第一引线11、第三引线13和第四引线14的配置、形状、大小是一个例子,并不限定于此,能够适当地设计。

第一引线11包括主面111、背面112和端面113。主面111和背面112在z方向上彼此朝向相反侧。主面111是朝向图3的上方的面。主面111是搭载半导体元件6a的面。背面112是朝向图3的下方的面。背面112是搭载半导体元件6b的面。端面113是切断在引线框中连接第一引线11和框的连接条(Tie bar)而形成的切断面。端面113从绝缘层7露出。

第三引线13包括主面131、背面132和端面133。主面131和背面132在z方向上朝向彼此相反侧。主面131是朝向图3的上方的面。背面132是朝向图3的下方的面。端面133是切断在引线框中连接第三引线13与框的连接条而形成的切断面。端面133从绝缘层7露出。

第四引线14包括主面141、背面142和端面143。主面141和背面142在z方向上朝向彼此相反侧。主面141是朝向图3的上方的面。背面142是朝向图3的下方的面。端面143是切断在引线框中连接第四引线14与框的连接条而形成的切断面。端面143从绝缘层7露出。

如图3所示,第一引线11的主面111、第三引线13的主面131和第四引线14的主面141成同一平面。另外,第一引线11的背面112、第三引线13的背面132和第四引线14的背面142成同一平面。

半导体元件6a、6b是发挥半导体器件A1的电功能的要素。此外,在以下,对半导体元件6a、6b不加以区别的情况下记载为“半导体元件6”。如图2所示,在本实施方式中,半导体元件6为N型MOSFET。此外,半导体元件6也可以是其他的晶体管,也可以是其他的半导体元件。半导体元件6包括元件主面61、元件背面62、元件第一电极63、元件第二电极64和元件第三电极65。

元件主面61和元件背面62在z方向上彼此朝向相反侧。元件第一电极63配置在元件背面62。元件第二电极64和元件第三电极65配置在元件主面61。在本实施方式中,元件第一电极63为漏极电极,元件第二电极64为源极电极,元件第三电极65为栅极电极。

如图5所示,半导体元件6a搭载在第一引线11的主面111的中央。另外,如图3所示,半导体元件6a以元件背面62与主面111相对的姿态经由导电性接合层51接合于第一引线11。由此,半导体元件6a的元件第一电极63经由导电性接合层51电连接于第一引线11。半导体元件6b搭载在第一引线11的背面112的中央。另外,如图3所示,半导体元件6b以元件背面62与背面112相对的姿态经由导电性接合层51接合于第一引线11。由此,半导体元件6b的元件第一电极63经由导电性接合层51电连接于第一引线11。半导体元件6a的元件第一电极63和半导体元件6b的元件第一电极63均电连接于第一引线11。即,半导体器件A1构成为2个半导体元件6a、6b的漏极电极彼此连接的漏极共通电路(参照图2)。

如图3所示,导电性接合层51是插设在半导体元件6a、6b与第一引线11之间的导电体。经由导电性接合层51,半导体元件6a、6b接合于第一引线11,并且能够确保半导体元件6a、6b的元件第一电极63与第一引线11的导通。在本实施方式中,导电性接合层51通过涂布导电性接合材料并使其热固化而形成。导电性接合材料例如是由以含有Ag的环氧树脂为主剂的合成树脂构成的接合材料(Ag膏)。此外,导电性接合材料也可以是烧结膏或焊料等的其他材料。另外,导电性接合层51的形成方法没有特别的限定,导电性接合层51只要是由具有导电性的材料构成即可。

绝缘层7覆盖第一引线11、第三引线13、第四引线14和半导体元件6a、6b。绝缘层7例如由预浸料构成。预浸料为使碳纤维等的纤维状加强材料中均匀地含浸环氧树脂等的热固化性树脂,进行加热或者干燥而形成为半固化状态的强化塑料成形材料。此外,绝缘层7的材料没有特别的限定,也可以是具有电绝缘性的材料。绝缘层7具有绝缘层主面71、绝缘层背面72和绝缘层侧面73。绝缘层主面71和绝缘层背面72在z方向上彼此朝向相反侧。绝缘层主面71是朝向图3的上方的面,绝缘层背面72是朝向图3的下方的面。绝缘层侧面73是将绝缘层主面71和绝缘层背面72相连的面,朝向x方向或者y方向。在本实施方式中,第一引线11的端面113、第三引线13的端面133和第四引线14的端面143从绝缘层侧面73露出。第一引线11的端面113、第三引线13的端面133和第四引线14的端面143与绝缘层侧面73彼此成同一平面。

通孔211~214、221~225是通过在形成于绝缘层7的孔的侧面通过镀覆等形成有导电层而成的结构,构成导电通路。导电层例如为Cu等的金属。在本实施方式中,通孔211~214、221~225通过例如利用激光在绝缘层7形成孔,在该孔的侧面通过无电解电镀形成薄的Cu层作为基底层,利用以该基底层作为导电通路的电解电镀形成Cu的镀层来形成。此外,通孔211~214、221~225的形成方法没有特别的限定。通孔211~214、221~225的构造没有特别限定,可以在内部填充导电体,也可以填充绝缘膜8,也可以是空腔。

通孔211~214在绝缘层7的绝缘层主面71开口,在z方向上延伸。如图3所示,通孔211与半导体元件6a的元件第二电极64相接并且导通。通孔212与半导体元件6a的元件第三电极65相接并且导通。通孔213与第三引线13的主面131相接,并且与第三引线13导通。通孔214与第四引线14的主面141相接,并且与第四引线14导通。在本实施方式中,如图5所示,配置有2个通孔211。此外,通孔211~214的配置个数和配置位置是一个例子,并不限定于此,能够适当地设计。

通孔221~225在绝缘层7的绝缘层背面72开口,在z方向上延伸。如图3所示,通孔221与半导体元件6b的元件第二电极64相接并导通。通孔222与半导体元件6b的元件第三电极65相接并导通。通孔223与第三引线13的背面132相接,并且与第三引线13导通。通孔224与第四引线14的背面142相接,并且与第四引线14导通。通孔225与第一引线11的背面112相接,并且与第一引线11导通。在本实施方式中,如图6所示,设置有2个通孔221。此外,通孔221~225的配置个数和配置位置是一个例子,并不限定于此,能够适当设计。

配线图案311、312、321~324是形成于绝缘层7的绝缘层主面71或者绝缘层背面72的配线图案,构成导电通路。在本实施方式中,配线图案311、312、321~324例如由Cu等的金属构成。在本实施方式中,配线图案311、312、321~324通过利用无电解电镀形成Cu薄膜,并以该Cu薄膜作为导电通路利用电解电镀而形成。此外,配线图案311、312、321~324的形成方法没有限定。

配线图案311、312形成在绝缘层主面71,彼此分开地配置。如图3和图4所示,配线图案311与通孔211、213相接,并将通孔211与通孔213电连接。另外,配线图案312与通孔212、214相接,并将通孔212与通孔214电连接。此外,配线图案311、312的形状和配置是一个例子,并不限定于此,能够适当设计。

配线图案321~324形成于绝缘层背面72,彼此分开地配置。如图3和图6所示,配线图案321与通孔221相接并且导通。配线图案322与通孔222、224相接,并且将通孔222与通孔224电连接。配线图案323与通孔223相接并且导通。配线图案324与通孔225相接并且导通。此外,配线图案321~324的形状和配置是一个例子,并不限定于此,能够适当地设计。

第一电极41、第二电极42、第三电极43和第五电极45是为了将半导体器件A1表面安装于未图示的电路基板而使用的电极衬垫,配置在半导体器件A1的背面侧(绝缘层7的绝缘层背面72侧)。在本实施方式中,如图6所示,第一电极41、第二电极42、第三电极43和第五电极45在z方向看是圆形形状的导电体。第一电极41、第二电极42、第三电极43和第五电极45例如由彼此层叠的Ni层、Pd层和Au层构成,通过无电解电镀形成。此外,第一电极41、第二电极42、第三电极43和第五电极45的材料、形状、厚度、配置位置和形成方法并不限定于此。例如也可以是焊球。

第一电极41与配线图案323相接并且导通。第二电极42与配线图案324相接并且导通。第三电极43与配线图案321相接并且导通。第五电极45与配线图案322相接并且导通。

第一引线11、第三引线13、第四引线14、通孔211~214、221~225、配线图案311、312、321~324形成了半导体元件6a、6b的各电极与第一电极41、第二电极42、第三电极43和第五电极45的导通路径。

第一电极41经由配线图案323、通孔223、第三引线13、通孔213、配线图案311和通孔211而与半导体元件6a的元件第二电极64(源极电极)导通。因此,第一电极41作为半导体元件6a的源极端子发挥功能。第二电极42经由配线图案324、通孔225和第一引线11而与半导体元件6a的元件第一电极63(漏极电极)和半导体元件6b的元件第一电极63(漏极电极)导通。因此,第二电极42作为半导体元件6a和半导体元件6b的漏极端子发挥功能。半导体器件A1构成为2个半导体元件6a、6b的漏极电极彼此连接的漏极共通电路(参照图2)。

第三电极43经由配线图案321和通孔221与半导体元件6b的元件第二电极64(源极电极)导通。因此,第三电极43作为半导体元件6b的源极端子发挥功能。第五电极45经由配线图案322、通孔224、第四引线14、通孔214、配线图案312和通孔212而与半导体元件6a的元件第三电极65(栅极电极)导通。另外,第五电极45经由配线图案322和通孔222而与半导体元件6b的元件第三电极65(栅极电极)导通。因此,第五电极45作为半导体元件6a和半导体元件6b的栅极端子发挥功能。半导体器件A1构成为2个半导体元件6a、6b的栅极电极彼此连接的电路。

绝缘膜8形成于绝缘层主面71和绝缘层背面72,覆盖配线图案311、312、321~324。绝缘膜8是为了保护配线图案311、312、321~324,并且将第一电极41、第二电极42、第三电极43和第五电极45彼此电绝缘而设置的。绝缘膜8覆盖绝缘层主面71的整个面和配线图案311、312的整体。另外,绝缘膜8覆盖绝缘层背面72的整个面,并且覆盖配线图案321~324之中除了形成第一电极41、第二电极42、第三电极43和第五电极45的部分以外的整体。绝缘膜8例如由阻焊剂等的绝缘材料例如利用光刻技术而形成。此外,绝缘膜8的材料、厚度和形成方法没有限定。

接着,关于半导体器件A1的制造方法的一例参照图7~图14在以下进行说明。图7是俯视图,是相当于图5的图。图8~14是表示示意性的截面的图,是相当于图3的图。

首先,准备如图7所示的引线框900。引线框900是要形成为第一引线11、第三引线13和第四引线14的板状的材料。此外,在图7中,仅表示了要形成为1个第一引线11、第三引线13和第四引线14的区域。引线框900通过对金属板进行蚀刻处理而形成。此外,引线框900可以通过对金属板进行冲孔加工处理而形成。在图7中,为了便于理解,在引线框900中标注了斜线。引线框900具有在z方向上彼此朝向相反侧的主面901和背面902。主面901为朝向图8的上方的面,是要形成为第一引线11的主面111、第三引线13的主面131和第四引线14的主面141的面。背面902是朝向图8的下方的面,是要形成为第一引线11的背面112、第三引线13的背面132和第四引线14的背面142的面。

接着,如图8所示,将半导体元件6a、6b焊接于引线框900。首先,在引线框900的主面901之中,在成为第一引线11的主面111的区域的中央涂布Ag膏,以元件背面62与引线框900的主面901相对的姿态焊接半导体元件6a。接着,进行回流焊处理。通过回流焊处理使Ag膏热固化而形成为导电性接合层51,半导体元件6a经由导电性接合层51接合于引线框900。另外,半导体元件6a的元件第一电极63经由导电性接合层51而与引线框900电连接。接着,引线框900的背面902之中,在成为第一引线11的背面112的区域的中央涂布Ag膏,以使元件背面62与引线框900的背面902相对的姿态焊接半导体元件6b。接着,进行回流焊处理。通过回流焊处理使Ag膏热固化而形成为导电性接合层51,半导体元件6b经由导电性接合层51接合于引线框900。另外,半导体元件6b的元件第一电极63经由导电性接合层51电连接于引线框900。

接着,如图9所示,形成绝缘层903。在该工序中,在引线框900的主面901和背面902分别粘贴片状的预浸料而使其层叠,形成覆盖引线框900、半导体元件6a、6b的绝缘层903。绝缘层903成为绝缘层7。绝缘层903具有在z方向上彼此朝向相反侧的主面903a和背面903b。主面903a为朝向图9的上方的面,并且是成为绝缘层主面71的面。背面903b是朝向图9的下方的面,并且是成为绝缘层背面72的面。

接着,如图10所示在绝缘层903形成孔904。在本工序中,首先例如利用激光从绝缘层903的主面903a形成朝向z方向的孔904。各孔904在规定的位置以达到引线框900的主面901、或者半导体元件6a的元件主面61的方式形成。接着,例如利用激光从绝缘层903的背面903b形成朝向z方向的孔904。各孔904在规定的位置以达到引线框900的背面902、或者半导体元件6b的元件主面61的方式形成。

接着,形成通孔和配线图案。首先,如图11所示,通过无电解电镀在孔904的侧面和绝缘层903的主面903a以及背面903b的整个面形成薄的Cu层即基底层905。

接着,以覆盖基底层905的整个面的方式接合光敏干膜,并通过进行曝光及显影进行图案化。基底层905从光敏干膜之中通过曝光而被除去的部分露出。接着,如图12所示,形成与露出的基底层905相接的镀覆层906。镀覆层906由Cu构成,通过将基底层905作为导电通路进行电解电镀而形成。

接着,如图13所示,将没有被镀覆层906覆盖的不需要的基底层905全部除去。不需要的基底层905例如通过湿式蚀刻被除去。绝缘层903从基底层905被除去的部分露出。彼此层叠的基底层905和镀覆层906形成为一体,以下将形成有孔904的部分作为通孔907a,将形成在绝缘层903的主面903a和背面903b的部分作为配线图案907b。通孔907a形成通孔211~214、221~225,配线图案907b形成配线图案311、312、321~324。

接着,如图14所示,形成覆盖绝缘层903的主面903a以及背面903b和配线图案907b的绝缘膜908。本实施方式的绝缘膜908通过光刻技术形成。首先,以覆盖绝缘层903的主面903a以及背面903b和配线图案907b的整体的方式涂布阻焊剂。接着,通过进行曝光及显影进行图案化。由此,形成在规定的位置形成有开口部908a的绝缘膜908。绝缘膜908形成绝缘膜8。

接着,在绝缘膜908的开口部908a中通过无电解电镀形成各电极。接着,将引线框900、绝缘层903和绝缘膜908沿着与x方向和y方向平行的未图示的切断线切断,由此分割为单片。在该工序中所分割的单片形成半导体器件A1。经过以上的工序而获得上述的半导体器件A1。此外,半导体器件A1的制造方法并不限定于上述的内容。

接着,关于半导体器件A1的作用效果进行说明。

基于本实施方式,在半导体器件A1中,半导体元件6a搭载于第一引线11的主面111,半导体元件6b搭载于第一引线11的背面112。因此,与半导体元件6a和半导体元件6b排列并搭载在第一引线11的相同面的情况相比较,能够使半导体元件6a、6b成为表面积(与z方向正交的面的面积)较大的元件。由此,能够使作为MOSFET的半导体元件6a、6b的导通电阻较小。另外,如果半导体元件6a、6b的表面积相同,与将半导体元件6a、6b排列搭载在相同面的情况相比较,能够使半导体器件A1的表面积较小。

另外,基于本实施方式,半导体元件6a的元件第一电极63和半导体元件6b的元件第一电极63均与第一引线11电连接。因此,能够构成2个半导体元件6a、6b的漏极电极彼此连接的漏极共通电路。

另外,基于本实施方式,第五电极45经由配线图案322、通孔224、第四引线14、通孔214、配线图案312和通孔212与半导体元件6a的元件第三电极65(栅极电极)导通,另外,经由配线图案322和通孔222与半导体元件6b的元件第三电极65(栅极电极)导通。因此,通过将控制信号输入到第五电极45,能够同时控制半导体元件6a和半导体元件6b这两者。

基于图15,关于本发明的第二实施方式的半导体器件A2进行说明。在图15中,对于与上述的半导体器件A1相同或者类似的要素标注相同的附图标记,省略重复的说明。图15是表示半导体器件A2的示意性的截面的图,是相当于第一实施方式的半导体器件A1的图3的图。

本实施方式的半导体器件A2,在半导体元件6a的元件第三电极65与半导体元件6b的元件第三电极65不导通这一点,与第一实施方式的半导体器件A1不同。本实施方式的配线图案322与通孔224不相接。另外,半导体器件A2进一步具有配线图案325和第六电极46。

配线图案325与配线图案321~324是相同的,在绝缘层背面72中与配线图案321~324分开地形成。配线图案325与通孔224和第五电极45相接,将通孔224与第五电极45电连接。第六电极46与第五电极45是同样的,与配线图案322相接并导通。在本实施方式中,第五电极45经由配线图案325、通孔224、第四引线14、通孔214、配线图案312和通孔212与半导体元件6a的元件第三电极65(栅极电极)导通,但与半导体元件6b的元件第三电极65(栅极电极)不导通。另一方面,第六电极46经由配线图案322和通孔222与半导体元件6b的元件第三电极65(栅极电极)导通。因此,第五电极45作为半导体元件6a的栅极端子发挥功能,并且第六电极46作为半导体元件6b的栅极端子发挥功能。

在本实施方式中,半导体元件6a搭载在第一引线11的主面111,半导体元件6b搭载在第一引线11的背面112。因此,相比于半导体元件6a和半导体元件6b排列搭载在第一引线11的相同面的情况,能够使半导体元件6a、6b形成为表面积(与z方向正交的面的面积)较大的元件。另外,在本实施方式中,半导体元件6a的元件第一电极63和半导体元件6b的元件第一电极63均与第一引线11电连接。因此,能够构成2个半导体元件6a、6b的漏极电极彼此连接的漏极共通电路。

另外,基于本实施方式,第五电极45与半导体元件6a的元件第三电极65(栅极电极)导通,并且第六电极46与半导体元件6b的元件第三电极65(栅极电极)导通,第五电极45与第六电极46不导通。因此,能够在第五电极45与第六电极46输入不同的控制信号,因此半导体元件6a和半导体元件6b能够独立地控制。

此外,半导体器件A2不具有配线图案321~325,第一电极41可以与通孔223直接相接,第二电极42可以与通孔225直接相接,第三电极43可以与通孔221直接相接,第五电极45可以与通孔224直接相接,第六电极46可以与通孔222直接相接。在该情况下,因为不需要在绝缘层背面72形成配线图案321~325,因此能够削减用于配线图案形成的材料。

基于图16关于本发明的第三实施方式的半导体器件A3进行说明。图16中,关于与前述的半导体器件A1相同或者类似的要素标注相同的附图标记,省略重复的说明。图16是表示半导体器件A3的示意性的截面的图,是与第一实施方式的半导体器件A1的图3相当的图。

本实施方式的半导体器件A3,在第一引线11的背面112具有凹部114,并且半导体元件6b配置在凹部114中这一点,与第一实施方式的半导体器件A1不同。

凹部114形成于第一引线11的背面112,是向主面111侧凹陷的凹部,具有与背面112平行的底面114a。凹部114例如通过半蚀刻处理形成。半导体元件6b配置于凹部114中,以元件背面62与底面114a相对的姿态经由导电性接合层51接合于第一引线11。

在本实施方式中,半导体元件6a搭载于第一引线11的主面111,半导体元件6b搭载于第一引线11的背面112。因此,相比于半导体元件6a和半导体元件6b排列搭载在第一引线11的相同面的情况,能够将半导体元件6a、6b形成为表面积(与z方向正交的面的面积)较大的元件。

另外,基于本实施方式,半导体元件6b配置在形成于第一引线11的背面112的凹部114的底面114a。因此,在从底面114a至绝缘层背面72的距离t1,与第一实施方式中的从背面112至绝缘层背面72的距离为相同距离的情况下,半导体器件A3的厚度(z方向的尺寸)比半导体器件A1的厚度薄。即,对半导体器件的薄型化有贡献。另外,因为从背面112至绝缘层背面72的距离t2比第一实施方式的情况小,通孔223~225的高度(z方向的尺寸)比第一实施方式的情况低。因此,能够降低通孔223~225的电阻值。另外,能够削减用于形成通孔223~225的材料。并且,为了形成通孔223~225从绝缘层背面72穿设的孔的深度变浅。由此,能够抑制由于穿设而产生的缺陷。

此外,半导体器件A3中,代替在背面112具有凹部114,而可以在主面111具有凹部115。在该情况下,凹部115形成在第一引线11的主面111,是向背面112侧凹陷的凹部,具有与主面111平行的底面115a。半导体元件6a配置在凹部115中,以元件背面62与底面115a相对的姿态经由导电性接合层51接合于第一引线11。在该变形例中,在从底面115a至绝缘层主面71的距离,与在第一实施方式中的从主面111至绝缘层主面71的距离相同的情况下,半导体器件A3的厚度(z方向的尺寸)比半导体器件A1的厚度薄。即,对半导体器件的薄型化有贡献。另外,因为从主面111至绝缘层主面71的距离比第一实施方式的情况小,所以通孔213、214的高度(z方向的尺寸)比第一实施方式的情况低。因此,为了形成通孔213、214而从绝缘层主面71穿设的孔的深度变浅。由此,能够缩短用于进行穿设的工序所花费的时间。另外,能够削减用于形成通孔213、214的材料。此外,半导体器件A3中,背面112具有凹部114,半导体元件6b配置在凹部114中,并且,主面111具有凹部115,半导体元件6a也可以配置在凹部115中。

基于图17,关于本发明的第四实施方式的半导体器件A4进行说明。图17中,对于与前述的半导体器件A1相同或者类似的要素标注相同的附图标记,省略重复的说明。图17是表示半导体器件A4的示意性的截面的图,是与第一实施方式的半导体器件A1的图3相当的图。

本实施方式的半导体器件A4,在各电极不仅配置在背面侧而且也配置在主面侧(绝缘层7的绝缘层主面71侧)这一点,与第一实施方式的半导体器件A1不同。半导体器件A4进一步包括第五引线15、通孔215、216、226、配线图案313、314、第一电极41a、第二电极42a、第三电极43a和第五电极45a。

第五引线15与第四引线14是相同的,与第一引线11、第三引线13和第四引线14分开地配置。第五引线15具有主面151、背面152和端面153(未图示)。主面151和背面152在z方向上彼此朝向相反侧。主面151是朝向图17的上方的面。背面152是朝向图17的下方的面。端面153是通过在引线框中将连接第五引线15与框的连接条切断而形成的切断面。端面153从绝缘层7露出。如图17所示,第五引线15的主面151与第一引线11的主面111、第三引线13的主面131和第四引线14的主面141成同一平面。另外,第五引线15的背面152与第一引线11的背面112、第三引线13的背面132和第四引线14的背面142成同一平面。

通孔215、216与通孔211~214是相同的,在绝缘层7的绝缘层主面71开口并且在z方向上延伸。如图17所示,通孔215与第一引线11的主面111相接,且与第一引线11导通。通孔216与第五引线15的主面151相接,且与第五引线15导通。通孔226与通孔221~225是相同的,在绝缘层7的绝缘层背面72开口且在z方向上延伸。如图17所示,通孔226与第五引线15的背面152相接,且与第五引线15导通。

配线图案313、314与配线图案311、312是相同的,形成在绝缘层主面71,与配线图案311、312分开地配置。如图17所示,配线图案313与通孔215相接并且导通。配线图案314与通孔216相接并且导通。在图17中虽然没有表示,配线图案311与通孔211相接的部分和与通孔213相接的部分在绝缘层主面71相连。同样地,配线图案312与通孔212相接的部分和与通孔214相接的部分在绝缘层主面71上相连。另外,虽然图17中没有表示,配线图案321与通孔221相接的部分和与通孔226相接的部分在绝缘层背面72上相连。同样地,配线图案322与通孔222相接的部分和与通孔224相接的部分在绝缘层背面72上相连。

第一电极41a、第二电极42a、第三电极43a和第五电极45a,与第一电极41、第二电极42、第三电极43和第五电极45是相同的,配置在半导体器件A4的主面侧。第一电极41a与配线图案311相接且导通。第二电极42a与配线图案313相接且导通。第三电极43a与配线图案314相接且导通。第五电极45a与配线图案312相接且导通。因为第一电极41a与配线图案311导通,所以与第一电极41导通,并且作为半导体元件6a的源极端子发挥功能。第二电极42a经由配线图案313和通孔215与第一引线11导通。因此,第二电极42a与第二电极42导通,并且作为半导体元件6a和半导体元件6b的漏极端子发挥功能。第三电极43a经由配线图案314、通孔216、第五引线15和通孔226与配线图案321导通。因此,第三电极43a与第三电极43导通,并且作为半导体元件6b的源极端子发挥功能。第五电极45a因为与配线图案312导通,所以与第五电极45导通,并且作为半导体元件6a和半导体元件6b的栅极端子发挥功能。

在本实施方式中,半导体元件6a搭载在第一引线11的主面111,半导体元件6b搭载在第一引线11的背面112。因此,相比于半导体元件6a和半导体元件6b排列搭载在第一引线11的相同面的情况,能够将半导体元件6a、6b形成为表面积(与z方向正交的面的面积)较大的元件。另外,基于本实施方式,第一电极41a、第二电极42a、第三电极43a和第五电极45a配置在半导体器件A4的主面侧。因为各电极配置在主面侧和背面侧,在半导体器件A4的主面侧安装被动元件等,在电路基板进行安装时的自由度增加。此外,第一电极41a、第二电极42a、第三电极43a和第五电极45a也可以全都不配置,也可以仅配置所需要的电极。另外,第一电极41、第二电极42、第三电极43和第五电极45不需要全部配置。

基于图18~图21,关于本发明的第五实施方式的半导体器件A5进行说明。在图18~图21中,对于与前述的半导体器件A1相同或者类似的要素标注相同的附图标记,省略重复的说明。图18是表示半导体器件A5的电路图,是与第一实施方式的半导体器件A1的图2相当的图。图19是表示半导体器件A5的示意性的截面的图,是与第一实施方式的半导体器件A1的图3相当的图。图20~图21是表示半导体器件A5的俯视图,分别使一部分透过。图20是与第一实施方式的半导体器件A1的图5相当的图。图21是与第一实施方式的半导体器件A1的图6相当的图。此外,与第一实施方式的半导体器件A1的图4相当的图与图4是相同的,因此省略。

本实施方式的半导体器件A5,不是2个半导体元件6a、6b的漏极电极彼此连接的漏极共通电路,而是源极电极彼此连接的源极共通电路(参照图18),这一点与第一实施方式的半导体器件A1不同。半导体器件A5如图19~图22所示,还包括第二引线12、绝缘性接合层52、通孔226、配线图案325和第四电极44。

本实施方式的第一引线11如图20所示,在z方向看时,配置在半导体器件A1的y方向的中央,且比x方向的中央靠一方侧(图20中左侧)。另外,第一引线11支承半导体元件6a、6b,并且与半导体元件6a导通,且与半导体元件6b不导通。

第二引线12与第一引线11是相同的,与第一引线11、第三引线13和第四引线14分开地配置。第二引线12如图20所示,在z方向看时,配置在半导体器件A1的y方向的中央,且比x方向的中央靠另一方侧(图20中右侧)。即,本实施方式的第一引线11和第二引线12相当于将第一实施方式的第一引线11在x方向的中央分开为2个而得的引线。另外,第二引线12支承半导体元件6a、6b,并与半导体元件6b导通,与半导体元件6a不导通。此外,第一引线11、第二引线12、第三引线13和第四引线14的配置、形状、大小是一个例子,并不限定于此,能够适当地设计。第二引线12具有主面121、背面122和端面123。主面121和背面122在z方向上彼此朝向相反侧。主面121是朝向图19的上方的面。主面121是搭载半导体元件6a的面。背面122是朝向图19的下方的面。背面122是搭载半导体元件6b的面。端面123是在引线框中切断连接第二引线12与框的连接条而形成的切断面。端面123从绝缘层7露出。如图19所示,第二引线12的主面121与第一引线11的主面111、第三引线13的主面131和第四引线14的主面141成同一平面。另外,第二引线12的背面122与第一引线11的背面112、第三引线13的背面132和第四引线14的背面142成同一平面。

本实施方式的半导体元件6a、6b如图19所示,跨第一引线11和第二引线12而搭载。半导体元件6a以元件背面62与主面111和主面121相对的姿态经由导电性接合层51接合于第一引线11,且经由绝缘性接合层52接合于第二引线12。由此,半导体元件6a的元件第一电极63经由导电性接合层51与第一引线11电连接。另一方面,在半导体元件6a的元件第一电极63与第二引线12之间插设有绝缘性接合层52,因此半导体元件6a的元件第一电极63与第二引线12不导通。半导体元件6b以元件背面62与背面112和背面122相对的姿态经由导电性接合层51接合于第二引线12,经由绝缘性接合层52接合于第一引线11。由此,半导体元件6b的元件第一电极63经由导电性接合层51与第二引线12电连接。另一方面,因为在半导体元件6b的元件第一电极63与第一引线11之间插设有绝缘性接合层52,因此半导体元件6b的元件第一电极63与第一引线11不导通。

绝缘性接合层52如图19所示,在半导体元件6a与第二引线12之间以及半导体元件6b与第一引线11之间插设的绝缘体。通过导电性接合层51和绝缘性接合层52,半导体元件6a、6b接合于第一引线11和第二引线12。通过导电性接合层51,能够确保半导体元件6a的元件第一电极63与第一引线11的导通,能够确保半导体元件6b的元件第一电极63与第二引线12的导通。另一方面,通过绝缘性接合层52,能够确保半导体元件6a的元件第一电极63与第二引线12的绝缘,能够确保半导体元件6b的元件第一电极63与第一引线11的绝缘。绝缘性接合层52通过涂布绝缘性接合材料并使其热固化而形成。绝缘性接合材料例如为阻焊剂。此外,绝缘性接合材料也可以是其他的合成树脂等的材料。另外,绝缘性接合层52的形成方法没有限定,绝缘性接合层52由具有绝缘性的材料形成即可。

通孔226与通孔221~225是相同的,在绝缘层7的绝缘层背面72开口并在z方向上延伸。如图19和图20所示,通孔226与第二引线12的背面122相接,且与第二引线12导通。

配线图案325与配线图案321、322、324是相同的,形成于绝缘层背面72,与配线图案321、322、324分开地配置。如图19和图21所示,配线图案325与通孔226相接并导通。如图21所示,在本实施方式中,没有形成配线图案323,配线图案321与通孔223相接并导通。在图19分离地表示的、与配线图案321的通孔221相接的部分和与通孔223相接的部分,如图21所示在绝缘层背面72上相连。同样地,与配线图案322的通孔222相接的部分和与通孔224相接的部分在绝缘层背面72上相连。

第四电极44与第一电极41、第二电极42、第三电极43和第五电极45是相同的,配置在半导体器件A5的背面侧。如图19和图21所示,第四电极44与配线图案325相接并导通。第四电极44经由配线图案325、通孔226、第二引线12与半导体元件6b的元件第一电极63(漏极电极)导通。因此,第四电极44作为半导体元件6b的漏极端子发挥功能。

第二电极42经由配线图案324、通孔225和第一引线11与半导体元件6a的元件第一电极63(漏极电极)导通。因此,第二电极42作为半导体元件6a的漏极端子发挥功能。即,在本实施方式中,与第一实施方式不同,2个半导体元件6a、6b的漏极电极不是共通的。

第一电极41经由配线图案321、通孔223、第三引线13、通孔213、配线图案311和通孔211与半导体元件6a的元件第二电极64(源极电极)导通。另外,第一电极41经由配线图案321、通孔221与半导体元件6b的元件第二电极64(源极电极)导通。因此,第一电极41作为半导体元件6a和半导体元件6b的源极端子发挥功能。半导体器件A1形成为2个半导体元件6a、6b的源极电极彼此连接的源极共通电路(参照图18)。

在本实施方式中,半导体元件6a搭载于第一引线11的主面111,半导体元件6b搭载于第一引线11的背面112。因此,相比于半导体元件6a和半导体元件6b排列搭载在第一引线11的相同面的情况,能够将半导体元件6a、6b形成为表面积(与z方向正交的面的面积)较大的元件。

另外,基于本实施方式,第一电极41经由配线图案321、通孔223、第三引线13、通孔213、配线图案311和通孔211与半导体元件6a的元件第二电极64(源极电极)导通,另外,经由配线图案321和通孔221而与半导体元件6b的元件第二电极64(源极电极)导通。半导体元件6a的元件第一电极63(漏极电极)通过导电性接合层51与第一引线11导通,通过绝缘性接合层52与第二引线12绝缘。另外,半导体元件6b的元件第一电极63(漏极电极)通过导电性接合层51与第二引线12导通,通过绝缘性接合层52与第一引线11绝缘。由此,半导体元件6a的元件第一电极63与半导体元件6b的元件第一电极63被绝缘,2个半导体元件6a、6b的漏极电极不共通。因此,能够构成2个半导体元件6a、6b的源极电极彼此连接的源极共通电路。如图18所示,在半导体器件A5中,成为共通的源极端子(第一电极41)被接地连接,即使输入到各栅极端子(第五电极45)的控制信号的电压低,各MOSFET(半导体元件6a、6b)也能够驱动。因此,不需要用于将控制信号的电压升压的升压电路。

基于图22和图23关于本发明的第六实施方式的半导体器件A6进行说明。在图22和图23中,对与前述的半导体器件A1相同或者类似的要素标注相同的附图标记,省略重复的说明。图22是表示半导体器件A6的电路图,是与第一实施方式的半导体器件A1的图2相当的图。图23是表示半导体器件A6的示意性的截面的图,是与第一实施方式的半导体器件A1的图3相当的图。

本实施方式的半导体器件A6,不是2个半导体元件6a、6b的漏极电极彼此连接的漏极共通电路,而是使半导体元件6a的源极电极与半导体元件6b的漏极电极连接的电路(参照图22),这一点与第一实施方式的半导体器件A1不同。半导体器件A6例如用于逆变器的桥电路等(参照图22)。半导体器件A6如图23所示,进一步具有绝缘性接合层52、配线图案325和第六电极46。

本实施方式的第三引线13支承半导体元件6b,并且与半导体元件6b导通。本实施方式的半导体元件6b如图23所示,跨第一引线11和第三引线13而搭载。半导体元件6b以元件背面62与背面112和背面132相对的姿态经由导电性接合层51与第三引线13接合,并经由绝缘性接合层52与第一引线11接合。由此,半导体元件6b的元件第一电极63经由导电性接合层51与第三引线13电连接。另一方面,在半导体元件6b的元件第一电极63与第一引线11之间插设有绝缘性接合层52,因此半导体元件6b的元件第一电极63与第一引线11不导通。绝缘性接合层52与第五实施方式的绝缘性接合层52是相同的,如图23所示,是在半导体元件6b与第一引线11之间插设的绝缘体。半导体元件6b通过导电性接合层51与第三引线13接合,通过导电性接合层51能够确保半导体元件6b的元件第一电极63与第三引线13的导通。另外,半导体元件6b通过绝缘性接合层52与第一引线11接合,通过绝缘性接合层52能够确保半导体元件6b的元件第一电极63与第一引线11的绝缘。

配线图案325与配线图案321~324是相同的,在绝缘层背面72中与配线图案321~324分开地形成。配线图案325与通孔224和第五电极45相接,将通孔224与第五电极45电连接。第六电极46与第一电极41、第二电极42、第三电极43和第五电极45是相同的,与配线图案322相接并导通。在本实施方式中,第五电极45经由配线图案325、通孔224、第四引线14、通孔214、配线图案312和通孔212与半导体元件6a的元件第三电极65(栅极电极)导通,与半导体元件6b的元件第三电极65(栅极电极)不导通。另一方面,第六电极46经由配线图案322和通孔222与半导体元件6b的元件第三电极65(栅极电极)导通。因此,第五电极45作为半导体元件6a的栅极端子发挥功能,第六电极46作为半导体元件6b的栅极端子发挥功能。

第一电极41经由配线图案323、通孔223、第三引线13、通孔213、配线图案311和通孔211而与半导体元件6a的元件第二电极64(源极电极)导通。另外,第一电极41经由配线图案323、通孔223和第三引线13而与半导体元件6b的元件第一电极63(漏极电极)导通。因此,第一电极41作为半导体元件6a的源极端子发挥功能,并且作为半导体元件6b的漏极端子发挥功能。半导体器件A6形成为使半导体元件6a的源极电极与半导体元件6b的漏极电极连接的电路(参照图22)。

在本实施方式中,半导体元件6a搭载于第一引线11的主面111,半导体元件6b搭载于第一引线11的背面112。因此,相比于半导体元件6a和半导体元件6b排列并搭载在第一引线11的相同面的情况,能够使半导体元件6a、6b形成为表面积(与z方向正交的面的面积)较大的元件。

另外,基于本实施方式,第一电极41经由配线图案323、通孔223、第三引线13、通孔213、配线图案311和通孔211而与半导体元件6a的元件第二电极64(源极电极)导通,另外,经由配线图案323、通孔223和第三引线13而与半导体元件6b的元件第一电极63(漏极电极)导通。因此,能够构成使半导体元件6a的源极电极与半导体元件6b的漏极电极连接的电路。

另外,基于本实施方式,第五电极45与半导体元件6a的元件第三电极65(栅极电极)导通,第六电极46与半导体元件6b的元件第三电极65(栅极电极)导通,第五电极45与第六电极46不导通。因此,能够对第五电极45和第六电极46输入不同的控制信号,因此半导体元件6a和半导体元件6b能够独立地控制。

另外,基于本实施方式,能够降低半导体元件6a的元件第二电极64(源极电极)与半导体元件6b的元件第一电极63(漏极电极)之间的寄生电感。

基于图24关于本发明的第七实施方式的半导体器件A7进行说明。在图24中,对与前述的半导体器件A1相同或者相似的要素标注相同的附图标记,省略重复的说明。图24是表示半导体器件A7的电路图,是与第一实施方式的半导体器件A1的图2相当的图。

本实施方式的半导体器件A7,在2个半导体元件6a、6b为P型MOSFET这一点与第一实施方式的半导体器件A1不同。此外,半导体器件A7的构造与第一实施方式的半导体器件A1相同。因此,在本实施方式中,也能够起到与第一实施方式相同的效果。

基于图25,关于本发明的第八实施方式的半导体器件A8进行说明。图25中,对与前述的半导体器件A2相同或者相似的要素标注相同的附图标记,省略重复的说明。图25是表示具有半导体器件A8的电动机驱动电路的电路图。

本实施方式的半导体器件A8,在半导体元件6a为P型MOSFET,半导体元件6b为N型MOSFET这一点,与第一实施方式的半导体器件A1不同。此外,半导体器件A8的构造与第二实施方式的半导体器件A2相同。图25中表示的电动机驱动电路具有2个半导体器件A8。在作为一方的半导体器件A8的共通漏极端子的第二电极42(参照图15)、与作为另一方的半导体器件A8的第二电极42之间连接有电动机。对各半导体器件A8的作为连接有半导体元件6a的源极电极的源极端子的第一电极41(参照图153)输入电压Vin,各半导体器件A8的作为连接有半导体元件6b的源极电极的源极端子的第三电极43(参照图153)被接地。对于一方的半导体器件A8的作为连接有半导体元件6a的栅极电极的栅极端子的第五电极45(参照图15)、一方的半导体器件A8的作为连接有半导体元件6b的栅极电极的栅极端子的第六电极46(参照图15)、另一方的半导体器件A8的作为连接有半导体元件6a的栅极电极的栅极端子的第五电极45、和另一方的半导体器件A8的作为连接有半导体元件6b的栅极电极的栅极端子的第六电极46,分别输入驱动信号。

半导体器件A8的构造与第二实施方式的半导体器件A2相同,因此,在本实施方式中能够起到与第二实施方式相同的效果。

如第七实施方式和第八实施方式所示,半导体元件6a、6b分别可以为N型MOSFET,也可以为P型MOSFET。

基于图26,关于本发明的第九实施方式的半导体器件A9进行说明。在图26中,对与前述的半导体器件A1相同或者相似的要素标注相同的附图标记,省略充分的说明。图26是表示半导体器件A9的示意性的截面的图,是与第一实施方式的半导体器件A1的图3相当的图。

本实施方式的半导体器件A9,在2个半导体元件6a、6b为二极管这一点与第一实施方式的半导体器件A1不同。半导体器件A9如图26所示,不具有第四引线14、通孔212、214、222、224、配线图案312、322和第五电极45。

半导体元件6a、6b为二极管,作为阴极电极的元件第一电极63配置在元件背面62,作为阳极电极的元件第二电极64配置在元件主面61。没有配置元件第三电极65。因此,半导体器件A9不具有在第一实施方式的半导体器件A1中作为元件第三电极65的导电通路发挥功能的通孔212、214、222、224、配线图案312、322和第五电极45。

第一电极41因为与半导体元件6a的元件第二电极64(阳极电极)导通,所以作为半导体元件6a的阳极端子发挥功能。第三电极43因为与半导体元件6b的元件第二电极64(阳极电极)导通,所以作为半导体元件6b的阳极端子发挥功能。第二电极42因为与半导体元件6a的元件第一电极63(阴极电极)和半导体元件6b的元件第一电极63(阴极电极)导通,所以作为半导体元件6a和半导体元件6b的阴极端子发挥功能。半导体器件A9构成为2个半导体元件6a、6b的阴极电极彼此连接的阴极共通电路。此外,半导体器件A9也可以为使半导体元件6a、6b的元件主面61与第一引线11相对地接合的阳极共通电路。

在本实施方式中,半导体元件6a搭载于第一引线11的主面111,半导体元件6b搭载于第一引线11的背面112。因此,相比于半导体元件6a和半导体元件6b排列搭载于第一引线11的相同面的情况,能够将半导体元件6a、6b形成为表面积(与z方向正交的面的面积)较大的元件。

本发明的半导体器件并不限于上述的实施方式。本发明的半导体器件的各部的具体结构能够自由地进行各种设计变更。

- 半导体器件用部材、以及半导体器件用部材形成液和半导体器件用部材的制造方法、以及使用该方法制造的半导体器件用部材形成液、荧光体组合物、半导体发光器件、照明装置和图像显示装置

- 半导体器件的制造方法、半导体器件的制造装置、半导体器件、半导体器件的制造程序、半导体用处理剂以及转印用部件