具有抗共模干扰的光耦驱动电路

文献发布时间:2023-06-19 11:39:06

【技术领域】

本发明涉及光耦技术领域,尤其涉及一种具有抗共模干扰的光耦驱动电路。

【背景技术】

请参考图1所示,其为现有技术中的一种光耦的基本模型,由于其输入侧与输出侧之间通过封装分布着耦合电容,因此,当共模信号发生时,就会有电流通过耦合电容,使输入侧二极管误导通或者误关断,容易导致输出侧功率半导体误导通或者误关断。例如,当光耦处于ON状态,有共模信号发生时,有电流I

因此,有必要提供一种新的技术方案来克服上述问题。

【发明内容】

本发明要解决的技术问题在于提供一种具有抗共模干扰的光耦驱动电路,其可以降低甚至消除光耦的误导通和误关断现象,保护输出侧功率半导体的可靠导通和关断。

为了解决上述问题,根据本发明的第一个方面,本发明提供一种具有抗共模干扰的光耦驱动电路,,其包括:光耦U1,其包括输入侧发光二极管D1和输出侧光敏功率半导体Q2,所述输入侧发光二极管D1的阳极和阴极分别与第一信号输入端1和第二信号输入端2相连;开关Q4,其第一连接端和第二连接端分别与所述输入侧发光二极管D1的阳极和阴极相连,其控制端与第三信号输入端3相连;其中,所述第一信号输入端1接收第一输入信号,所述第二信号输入端2接收第二输入信号,所述第三信号输入端3接收第三输入信号。

进一步的,当所述第一输入信号1和第二输入信号2驱动所述输入侧发光二极管D1导通时,所述第三输入信号3控制开关Q4关断,且所述第一输入信号1和第二输入信号2提供给所述输入侧发光二极管D1的驱动电流IF与共模信号产生的共模干扰电流ILEDP的差值大于所述输入侧发光二极管D1的最小导通电流;当所述第一输入信号1和第二输入信号2驱动所述输入侧发光二极管D1截止时,所述第三输入信号3控制开关Q4导通,以泄放共模信号产生的共模干扰电流ILEDP。

进一步的,所述具有抗共模干扰的光耦驱动电路,还包括电阻R1、电阻R2和电阻R3,所述电阻R1的一端与所述第一信号输入端1相连,其另一端与所述开关Q4的控制端相连;所述电阻R2的一端与所述第一信号输入端1相连,其另一端与所述开关Q4的第一连接端相连;所述电阻R3的一端与所述第二信号输入端2相连,其另一端与所述开关Q4的第二连接端相连。

进一步的,所述开关Q4为三极管,当所述第一输入信号1和第二输入信号2驱动所述输入侧发光二极管D1导通时,所述第三输入信号3控制所述三极管Q4处于导通饱和状态,且所述三极管Q4的导通饱和电压小于所述输入侧发光二极管D1的最低导通电压。

进一步的,所述三极管为NPN型三极管,所述三极管的第一连接端、第二连接端和控制端分别为所述NPN型三极管的集电极、基极和射极。

进一步的,所述具有抗共模干扰的光耦驱动电路还包括电容C1,所述电容C1连接于所述第一信号输入端1和第二信号输入端2之间。

进一步的,所述第一输入信号1和第二输入信号2为一对PWM差分信号PWM1+、PWM1-;所述控制信号3为另一个PWM信号PWM2。

相对于现有技术,本发明中的具有抗共模干扰的光耦驱动电路,当输入信号驱动输入侧发光二极管导通时,增大输入侧二极管的输入驱动电流;当输入信号驱动输入侧发光二极管截止(或关断)时,控制与输入侧发光二极管并联的开关导通,从而可以降低甚至消除光耦的误导通和误关断现象,保护输出侧功率半导体的可靠导通和关断。

本发明的其他目的,特征以及优点,下面将结合附图在具体实施方式中详细描述。

【附图说明】

结合参考附图及接下来的详细描述,本发明将更容易理解,其中同样的附图标记对应同样的结构部件,其中:

图1为现有技术中的一种光耦的基本模型;

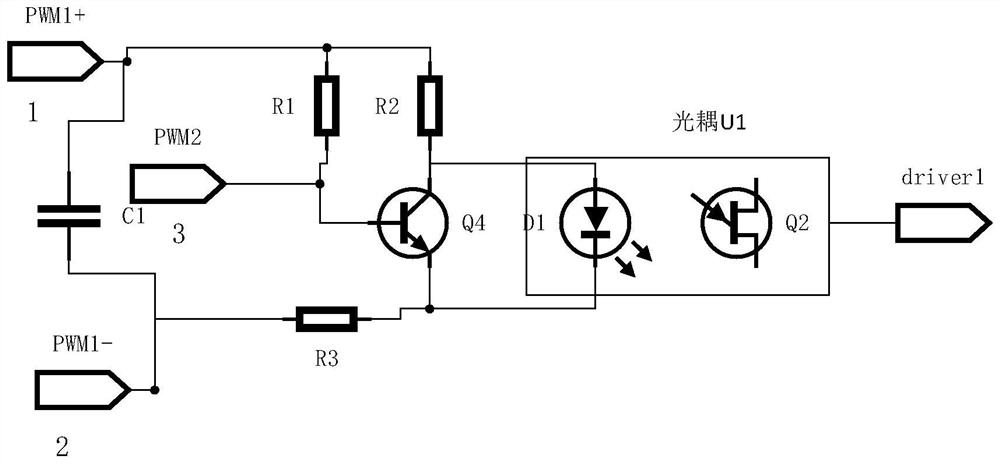

图2为本发明在一个实施例中的具有抗共模干扰的光耦驱动电路的电路示意图。

【具体实施方式】

为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

此处所称的“一个实施例”或“实施例”是指与所述实施例相关的特定特征、结构或特性至少可包含于本发明至少一个实现方式中。在本说明书中不同地方出现的“在一个实施例中”并非必须都指同一个实施例,也不必须是与其他实施例互相排斥的单独或选择实施例。本发明中的“多个”、“若干”表示两个或两个以上。本发明中的“和/或”表示“和”或者“或”。

请参考图2所示,其为本发明在一个实施例中的具有抗共模干扰的光耦驱动电路的电路示意图。图2所示的具有抗共模干扰的光耦驱动电路包括电容C1、电阻R1、电阻R2、电阻R3,开关Q4和光耦U1。

光耦U1包括输入侧发光二极管D1和输出侧光敏功率半导体Q2,输入侧发光二极管D1的阳极和阴极分别与第一信号输入端1和第二信号输入端2相连。输入侧发光二极管D1导通时发出光线,输出侧光敏功率半导体Q2接收光线后导通;输入侧发光二极管D1关断(或截止)时,输出侧光敏功率半导体Q2关断。光耦U1可以为现有技术中的光耦,在此不再赘述。

开关Q4的第一连接端和第二连接端分别与输入侧发光二极管D1的阳极和阴极相连,其控制端与第三信号输入端3相连。其中,第一信号输入端1接收第一输入信号,第二信号输入端2接收第二输入信号,第三信号输入端3接收第三输入信号。

在图2所示的具体实施例中,开关Q4为三极管Q4,电阻R1的一端与第一信号输入端1相连,其另一端与开关Q4的控制端相连;电阻R2的一端与第一信号输入端1相连,其另一端与开关Q4的第一连接端相连;电阻R3的一端与第二信号输入端2相连,其另一端与开关Q4的第二连接端相连;电容C1连接于第一信号输入端1和第二信号输入端2之间。在图2所示的具体实施例中,三极管Q4为NPN型三极管,三极管Q4的第一连接端、第二连接端和控制端分别为NPN型三极管的集电极、基极和射极。

以下具体介绍图2所示的光耦驱动电路的抗共模干扰的原理。

当光耦U1处于ON状态时(即当第一输入信号1和第二输入信号2驱动输入侧发光二极管D1导通时),增大输入驱动电流,且第三输入信号3控制开关Q4关断。其中,增大输入驱动电流具体为,第一输入信号1和第二输入信号2提供给输入侧发光二极管D1的驱动电流(或工作电流)I

当光耦U1处于OFF状态时(即当第一输入信号1和第二输入信号2驱动输入侧发光二极管D1关断或截止时),第三输入信号3控制开关Q4导通,以泄放共模信号产生的共模干扰电流I

在图2所示的具体实施例中,第一输入信号1和第二输入信号2为一对PWM(Pulsewidth modulation,脉冲宽度调制)差分信号PWM1+、PWM1-;第三输入信号3为另一个PWM信号PWM2。

综上所述,本发明中的具有抗共模干扰的光耦驱动电路包括:光耦U1,其包括输入侧发光二极管D1和输出侧光敏功率半导体Q2,输入侧发光二极管D1的阳极和阴极分别与第一输入信号1和第二输入信号2相连;开关Q4,其第一连接端和第二连接端分别与输入侧发光二极管D1的阳极和阴极相连,其控制端与第三输入信号3相连。当第一输入信号1和第二输入信号2驱动输入侧发光二极管D1导通时,第三输入信号3控制开关Q4关断,且第一输入信号1和第二输入信号2提供给输入侧发光二极管D1的驱动电流I

在本发明中,“连接”、相连、“连”、“接”等表示电性相连或通信连接的词语,如无特别说明,则表示直接或间接的电性或通信连接。本文中的“耦接”是指间接或直接电性的连接,间接的连接可以是经过一个或多个电器件(比如电阻、电容、电感等)电性相连。

上述说明已经充分揭露了本发明的具体实施方式。需要指出的是,熟悉该领域的技术人员对本发明的具体实施方式所做的任何改动均不脱离本发明的权利要求书的范围。相应地,本发明的权利要求的范围也并不仅仅局限于前述具体实施方式。

- 具有抗共模干扰的光耦驱动电路

- 具有编码磁性阵列的光耦合和具有光耦合的连接器总成及电子装置