模数转换系统及音频设备

文献发布时间:2023-06-19 11:44:10

技术领域

本发明涉及音频技术领域,尤其是涉及一种模数转换系统及音频设备。

背景技术

在音频设备中,ADC(Analog-to-Digital Converter,模数转换器)系统的作用非常重要。在传统的ADC系统中,ADC模拟部分以输出采样率(Fs,sampling frequency)的一个固定倍数的时钟工作,这个比率称为过采样率(OVFS,oversampling frequency)。通常OVFS=128,也有256或其他的倍率,而这个倍率在一个ADC系统中通常是固定的,比如,固定是128,ADC模拟部分工作在128倍时钟(128Fs)。

输出采样率通常有Fs=44.1KHz/48KHz两个采样率系列,对应的128Fs时钟频率是5.6448MHz/6.144MHz。为了产生这个频率的时钟,需要一个PLL(phase-locked-loop,锁相环)电路,以高频晶振(HOSC,High frequency oscillator)产生的24MHz时钟为参考,并经过数字分频,产生所需要的5.6448MHz或6.144MHz时钟。

固定过采样率的ADC系统限制了其应用范围。

发明内容

本发明主要解决的技术问题是提供一种模数转换系统及音频设备,可提供不同的过采样率信号,在需要高性能的应用中能提高系统的过采样率、取得更高的性能,在低功耗应用中能使用低过采样率降低系统的工作频率,节省功耗。

为解决上述技术问题,本发明采用的一个技术方案是:提供一种模数转换系统,所述模数转换系统包括依次连接的模拟电路和数字电路以及分别连接所述模拟电路和数字电路的时钟控制电路,其中:

所述时钟控制电路用于根据不同的预设过采样率提供符合各设计比率的时钟信号;其中,所述时钟信号包括第一数字时钟信号、第二数字时钟信号以及模拟时钟信号;

所述模拟电路用于根据不同的所述模拟时钟信号输出对应的过采样信号;

所述数字电路用于根据所述第一数字时钟信号对所述过采样信号进行第一次抽取得到第一抽取信号,并进一步根据所述第二数字时钟信号对所述第一抽取信号进行第二次抽取,以输出符合采样率需求的第二抽取信号。

可选的,所述数字电路包括CIC滤波器,其中:

所述CIC滤波器用于接收所述第一数字时钟信号、根据不同的所述过采样信号获取对应的CIC滤波器抽取率、基于所述CIC滤波器抽取率和所述第一数字时钟信号产生CIC使能信号、并根据CIC使能信号对接收的所述过采样信号进行所述第一次抽取得到所述第一抽取信号。

可选的,所述CIC滤波器包括计算单元和控制单元,所述控制单元与所述计算单元电连接,其中:

所述控制单元包括计数器和译码器,其中:

所述计数器用于根据所述过采样信号对第一次抽取的时间点进行定时;

所述译码器用于根据计数器的定时以及所述过采样信号获取对应的所述CIC滤波器抽取率,并基于所述CIC滤波器抽取率和所述第一数字时钟信号产生CIC使能信号;

所述计算单元包括依次电连接的多个积分器、抽取器、多个微分器以及幅度调整器,其中:

所述多个积分器用于接收所述过采样信号,并对所述过采样信号进行多次积分处理;

所述抽取器用于根据所述CIC使能信号对积分后的信号进行第一次抽取得到第一抽取信号;

所述多个微分器用于对所述第一次抽取信号进行微分处理;

所述幅度调整器用于对微分后的信号进行幅度调整后输出幅度调整信号。

可选的,所述数字电路还包括FIR滤波器,所述FIR滤波器与所述CIC滤波器电连接,其中:

所述FIR滤波器用于接收所述第二数字时钟信号、根据所述过采样信号获取对应的FIR滤波器抽取率、基于所述FIR滤波器抽取率和所述第二时钟信号产生FIR使能信号、并根据所述FIR使能信号对接收的所述幅度调整信号进行第二次抽取得到所述第二抽取信号。

可选的,所述FIR滤波器包括第一FIR滤波器和第二FIR滤波器,所述第一FIR滤波器和所述第二FIR滤波器电连接,其中:

所述第一FIR滤波器用于根据所述过采样信号配置不同的过采样信号系列,其中,同一所述过采样信号系列具有相同的抽取率;

所述第一FIR滤波器还用于根据所述过采样信号系列获取对应的第一FIR滤波器抽取率、基于所述第一FIR滤波器抽取率和所述第二时钟信号产生第一FIR使能信号、并根据所述第一FIR使能信号对接收的所述幅度调整信号进行所述第二次抽取得到所述第二抽取信号;

所述第二FIR滤波器用于根据预设的第二FIR滤波器抽取率和所述第二数字时钟信号产生第二FIR使能信号,并根据所述第二FIR使能信号进一步对所述第二抽取信号进行第三次抽取,以输出符合采样率需求的第三抽取信号。

可选的,所述第一FIR滤波器包括计算单元和控制单元,其中:

所述控制单元用于根据所述过采样信号选择对应的所述第一FIR滤波器抽取率,并基于所述第一FIR滤波器抽取率和所述第二数字时钟信号产生所述第一FIR使能信号;

所述计算单元用于根据所述第一FIR使能信号对所述幅度调整信号进行抽取。

可选的,所述计算单元用于进一步根据所述过采样信号与补偿强度的映射关系,对第一FIR滤波器的频响曲线进行补偿,使得所述第一FIR的频响曲线补偿CIC滤波器的频响曲线,以获得平坦的通带曲线。

可选的,所述时钟控制电路包括依次电连接的高频晶振、第一分频器、第二分频器以及分频比译码器,其中:

所述高频晶振用于产生高频源信号;

所述第一分频器用于根据所述预设过采样率与所述设计比率对所述高频源信号进行第一分频,得到所述第二数字时钟信号;

所述第二分频器用于根据所述预设过采样率和所述设计比率对所述高频信号源进行第二分频,得到所述第一数字时钟信号和模拟时钟信号;

所述分频比译码器用于控制所述第二分频的分频比例。

可选的,所述时钟控制电路还包括PLL电路,所述PLL电路用于在特定应用中基于所述过采样信号产生频率稳定的时钟信号。

为解决上述技术问题,本发明采用的另一个技术方案是:提供一种音频设备,所述音频设备包括前文所述的模数转换系统。

本发明的有益效果是:区别于现有技术的情况,本发明提供一种模数转换器和音频设备,模数转换系统包括依次连接的模拟电路和数字电路以及分别连接所述模拟电路和数字电路的时钟控制电路,其中:所述时钟控制电路用于根据不同的预设过采样率提供符合各设计比率的时钟信号;其中,所述时钟信号包括第一数字时钟信号、第二数字时钟信号以及模拟时钟信号;所述模拟电路用于根据不同的所述模拟时钟信号输出对应的过采样信号;所述数字电路用于根据所述第一数字时钟信号对所述过采样信号进行第一次抽取得到第一抽取信号,并进一步根据所述第二数字时钟信号对所述第一抽取信号进行第二次抽取,以输出符合采样率需求的第二抽取信号。

因此,本发明的时钟电路可以提供不同的模拟时钟信号和数字时钟信号,使得可以支持不同的过采样频率模拟信号的要求,在需要高性能的应用中能提高系统的过采样率、取得更高的性能,在低功耗应用中能使用低过采样率降低系统的工作频率,节省功耗。

附图说明

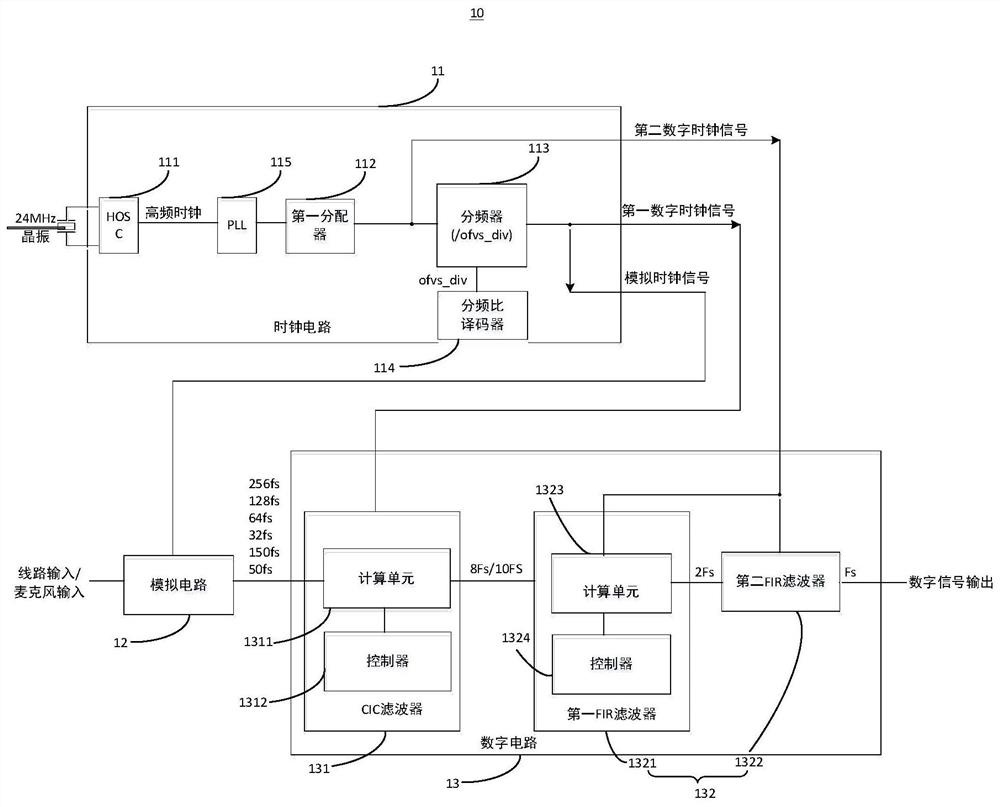

图1是本发明实施例提供的一种模数转换系统的结构示意图;

图2是本发明实施例的CIC滤波器的计算单元的结构示意图;

图3是本发明实施例的CIC滤波器的控制单元的结构示意图。

具体实施方式

现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的范例;相反,提供这些实施方式使得本发明将更加全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。所描述的特征、结构或特性可以以任何合适的方式结合在一个或更多实施方式中。

此外,附图仅为本发明的示意性图解,并非一定是按比例绘制。图中相同的附图标记表示相同或类似的部分,因而将省略对它们的重复描述。附图中所示的一些方框图是功能实体,不一定必须与物理或逻辑上独立的实体相对应。可以采用软件形式来实现这些功能实体,或在一个或多个硬件模块或集成电路中实现这些功能实体,或在不同网络和/或处理器装置和/或微控制器装置中实现这些功能实体。

请参阅图1,图1本发明实施例提供的一种模数转换系统的结构示意图。如图1所示,本发明的模数转换系统10包括依次连接的模拟电路12和数字电路13以及分别连接所述模拟电路12和数字电路13的时钟控制电路11。

所述时钟控制电路11用于根据不同的预设过采样率提供符合各设计比率的时钟信号;其中,所述时钟信号包括第一数字时钟信号、第二数字时钟信号以及模拟时钟信号。

在一可选的实施例中,第一数字时钟信号与所述模拟时钟信号的频率相同,第二数字时钟信号与所述模拟时钟信号具有倍频关系的。

所述模拟电路12用于根据不同的所述模拟时钟信号输出对应的过采样信号。

所述数字电路13用于根据所述第一数字时钟信号对所述过采样信号进行第一次抽取得到第一抽取信号,并进一步根据所述第二数字时钟信号对第一抽取信号进行第二次抽取,以输出符合采样率需求的第二抽取信号。

因此,本发明的时钟电路11可以提供不同的模拟时钟信号和数字时钟信号,使得可以支持不同的过采样频率模拟信号的要求,在需要高性能的应用中能提高系统的过采样率、取得更高的性能,在低功耗应用中能使用低过采样率降低系统的工作频率,节省功耗。

本实施例中,模拟电路12可在不同的模拟时钟信号下产生不同的过采样信号。

线路录音,高清录音要求使用高性能的模数转换系统,而语音识别、语音唤醒由于需要在系统待机的时候持续工作,对模数转换系统的功耗要求特别高。

模数转换系统必须适应应用场景的变换,就要求它必须既能工作在高性能模式,又要能工作在低功耗模式。

sigma-delta变换的理论表明,提高过采样率能有效提高模数转换系统的性能,取得更高的动态范围(DR,dynamic range)和信噪比(SNR,signal-noise-ratio),而高过采样率又意味着高的时钟频率、高的功耗。

因此,本发明实施例可根据不同的性能需求,使用不同的过采样率,在性能和功耗之间取得平衡。在高性能的应用中能提高系统的过采样率、取得更高的性能,在低功耗应用中能使用低过采样率降低系统的工作频率,节省功耗。

请参阅表1,表1示出了本实施例的模数转换系统支持的过采样率,以及每一个过采样率对应的特点和应用:

表1

如表1可知,本发明实施例的模数转换系统可以实现序号为1~6的功能。对于只有语音录音、语音识别的应用系统来说,可以只实现5、6中的一项或两项功能,只使用HOSC(High frequency oscillator,高频晶振)就能满足要求,降低了产品的成本和功耗。

对于高性能应用来说,可以使用OVFS=256的参数,系统性能实测比使用标准的OVFS=128时要高50%。

对于高性能语音应用来说,可以使用OVFS=150,Fs=16KHz或Fs=32KHz,系统的成本比较低而性能比较高,系统性能实测比使用标准的OVFS=128时要高20%。

对于语音唤醒应用来说,可以使用OVFS=50或OVFS=32(如果系统有PLL的话),这时ADC系统时钟比较低,功耗比较低;对于某些数字麦克风(DMIC)而言,50Fs/32FS的时钟会使DMIC处于低功耗(Low Power)模式,进一步降低了系统功耗。

由于本发明实施例的模拟电路12可支持多种模拟时钟信号,产生不同的过采样信号。为了支持该不同的过采样率,本实施例对与模拟电路12匹配的数字电路13进行改进,具体如下文详述。

所述数字电路13包括CIC(Cascade Integrator Comb,级联积分梳状)滤波器131。CIC滤波器131用于接收所述第一数字时钟信号、根据不同的所述过采样率获取对应的CIC滤波器抽取率、基于所述CIC滤波器抽取率和所述第一数字时钟信号产生CIC使能信号,并根据CIC使能信号对接收的所述过采样信号进行所述第一次抽取得到所述第一抽取信号。

请参阅表2,表2是本发明实施例的过采样率与CIC滤波器、第一FIR滤波器以及第二FIR滤波器的抽取率的映射关系:

表2:

所述CIC滤波器131包括计算单元1311和控制单元1312。控制单元1312与计算单元1311电连接。

请一并参阅图2,图2是本发明实施例的CIC滤波器的计算单元1311的结构示意图。如图2所示,所述控制单元1311包括计数器1313和译码器1314,其中,所述计数器1313用于根据所述过采样信号对第一次抽取的时间点进行定时。所述译码器1314用于根据计数器的定时以及所述过采样信号获取对应的所述CIC滤波器抽取率,并基于所述CIC滤波器抽取率和所述第一数字时钟信号产生CIC使能信号。使得CIC滤波器的计算单元1311每隔D个时钟周期就输出一个数值。

请进一步参阅图3,图3是本发明实施例的CIC滤波器的控制单元1312的结构示意图。如图3所示,所述计算单元1312包括依次电连接的多个积分器1315、抽取器1316、多个微分器1317以及幅度调整器1318。所述多个积分器1315用于接收所述过采样信号,并对所述过采样信号进行多次积分处理。所述抽取器1316用于根据所述CIC使能信号对积分后的信号进行第一次抽取得到第一抽取信号。所述多个微分器1317用于对第一抽取信号进行微分处理,幅度调整器1318用于对微分后的信号进行幅度调整后输出幅度调整信号。

如图3所示,在实施例中,使用了4级的积分器和4级的微分器。然而本发明并不限定使用上述数量的积分器和微分器,在这里仅作为例子。本发明与传统CIC滤波器的区别在于,传统滤波器的CIC使能信号是固定的,输出不需要幅度调整,而本发明的CIC使能信号是根据过采样信号设置(通常是通过系统寄存器设置)由控制器产生的,是可以变化的,同时在滤波器的输出前进行幅度调整。

积分器、微分器的位宽按OVFS=256计算,在其他OVFS情况下需要调整信号的幅度,使得输入满幅信号时,输出也是满幅的;这个工作由幅度调整器1318完成。

所述数字电路13还包括FIR(Finite Impulse Response,非递归型滤波器)滤波器132。所述FIR滤波器132与所述CIC滤波器131电连接。所述FIR滤波器132用于接收所述第二数字时钟信号,根据所述过采样率获取对应的FIR滤波器抽取率,基于所述FIR滤波器抽取率和所述第二时钟信号产生FIR使能信号,并根据所述FIR使能信号对接收的所述幅度调整信号进行抽取进行第二次抽取得到所述第二抽取信号。

具体的,所述FIR滤波器132包括第一FIR滤波器1321和第二FIR滤波器1322。所述第一FIR滤波器1321和所述第二FIR滤波器1322电连接,所述第一FIR滤波器1321用于根据所述过采样信号配置不同的过采样信号系列,其中,同一所述过采样信号系列具有相同的抽取率;所述第一FIR滤波器1321还用于根据所述过采样信号系列获取对应的第一FIR滤波器抽取率、基于所述第一FIR滤波器抽取率和所述第二时钟信号产生第一FIR使能信号、并根据所述第一FIR使能信号对接收的所述幅度调整信号进行所述第二次抽取得到所述第二抽取信号。

所示第二FIR滤波器1322用于根据预设的第二FIR滤波器1322抽取率(如表2所示)和所述第二数字时钟信号产生第二FIR使能信号,并根据所述第二FIR使能信号进一步对所述第二抽信号进行第三次抽取,以输出符合采样率需求的第三抽取信号。

所述第一FIR滤波器1321包括计算单元1323和控制单元1324。

所述控制单元1323用于根据所述过采样信号选择对应的所述第一FIR滤波器抽取率,并基于所述第一FIR滤波器抽取率和所述第二数字时钟信号产生所述第一FIR使能信号。

所述计算单元1324用于根据所述第一FIR使能信号对幅度调整信号进行抽取。

所述计算单元1324用于进一步根据所述过采样信号与补偿强度的映射关系对第一FIR滤波器的频响曲线进行补偿,使得所述第一FIR的频响曲线补偿CIC滤波器的频响曲线,以获得平坦的通带曲线。

综上,第一FIR滤波器1321按过采样信号的系列来设计。具体的:

OVFS=256、128、64、32为一个系列,以OVFS=128为参数设计,工作在OVFS=256,128,64,32时使用这套滤波器系数,同时下采样抽取率为D1=4。

OVFS=150、50为一个系列,以OVFS=150为参数设计,工作在OVFS=256、128、64、32时使用这套滤波器系数,同时采样抽取率为D1=5。

同一OVFS系列的情况下的第一FIR滤波器1321不必重新设计也可以有效补偿CIC频谱曲线,获得相当平坦的通带曲线和足够的阻带衰减。

第一FIR滤波器1321是一个短长度滤波器,OVFS=150,50系列的典型长度L1=37,而OVFS=256、128、64、32时的典型长度是L1=29,使用两套系数对应两个OVFS系列。两套系数的长度也可以以OVFS=150为标准设计。使得第一FIR滤波器1321在实际设置中可以只使用一套时序控制电路、一套计算单元、两套滤波器系数,满足全部过采样率的需求。

第二FIR滤波器1322是一个长长度滤波器,典型的长度L2=124。

第二FIR滤波器1322滤波器总是工作在2fs输入采样率,输出1fs采样率,因此在实际设计中只需要一套时序控制电路、一套计算单元、一套滤波器系数。

从中可见,本发明的模数转换系统只需要在长度短的第一FIR滤波器1321使用两套系数就可以得到满意的效果,而长度长的第二FIR滤波器1322使用传统的1/2抽取滤波器就可以了。

以上的模拟时钟信号、第一数字时钟信号以及第二数字时钟信号均由时钟控制电路11提供。所述时钟控制电路11包括依次电连接的高频晶振111、第一分频器112、第二分频器113以及分频比译码器114。

所述高频晶振111用于产生高频源信号。如图所示,本实施例的高频源信号为24MHz晶振信号。

所述第一分频器112用于根据预设过采样率与所述设计比率对所述高频源信号进行第一分频,得到所述第二数字时钟信号。

所述第二分频器113用于根据所述预设过采样率和所述设计比率对所述高频信号源进行第二分频,得到所述第一数字时钟信号和模拟时钟信号。

所述分频比译码器114用于控制所述第二分频的分频比例。

可选的,所述时钟控制电路11还包括PLL电路115,所述PLL电路115用于在特定应用中基于过采样信号产生频率稳定的时钟信号。也即是用一个稳定的参考时钟产生另一个不同频率的稳定的时钟。

请参阅表3,表3是使用不同过采样率时,各时钟信号频率比的关系:

表3:

综上所述,本发明通过CIC滤波器的控制器和配套的时钟控制电路,通过合理调整CIC滤波器的抽取率,只在短长度的第一FIR滤波器使用两套滤波器系数的情况下,实现了对多过采样率的支持,使得在需要高性能的应用中能提高过采样率、提高系统性能,在低功耗应用中能不使用PLL而直接适用高频晶振、降低过采样率同时降低时钟频率,从而降低了成本和功耗。

本发明实施例还提供一种音频设备,该音频设备可包括前文所述的模数转换系统。

此外,上述附图仅是根据本发明示例性实施例的方法所包括的处理的示意性说明,而不是限制目的。易于理解,上述附图所示的处理并不表明或限制这些处理的时间顺序。另外,也易于理解,这些处理可以是例如在多个模块中同步或异步执行的。

本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本发明的其他实施例。本发明旨在涵盖本发明的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本发明的一般性原理并包括本发明未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本发明的真正范围和精神由权利要求指出。

应当理解的是,本发明并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本发明的范围仅由所附的权利要求来限。

- 模数转换系统及音频设备

- 动态比较器、模数转换器、模数转换系统以及校准方法