电阻式随机存取存储器及其制造方法

文献发布时间:2023-06-19 11:44:10

技术领域

本发明有关于一种存储器装置,且特别是有关于一种用于提高读出电流乱度的电阻式随机存取存储器及其制造方法。

背景技术

在现有技术的电阻式随机存取存储器(RRAM)中,在一个阵列区中包括多个存储器单元,且各存储器单元包括图案化的底电极层、电阻转换层与顶电极层。当对存储器单元施加形成电压或写入电压时,氧离子会受到电压驱动而离开电阻转换层。留在电阻转换层中的等效正价氧空缺形成导电路径(或导电细丝),进而使电阻转换层由高电阻态转换为低电阻态。当施加抹除电压时,氧离子回到电阻转换层并与等效正价氧空缺结合。因此,上述导电路径消失,而使电阻转换层由低电阻态转换为高电阻态。一般而言,高电阻态对应到逻辑状态“0”,而低电阻态对应到逻辑状态“1”。

在某些应用领域(例如,人工智能、加密等)中,自这些存储器单元所读出的电流值(以下简称读出电流)最好是难以预测的。亦即,读出电流的乱度(randomness)越高越好。然而,现有的电阻式随机存取存储器要求这些存储器单元具有高度的结构均一性,使得自这些存储器单元所读出的电流值具有高度均一的表现,如此则不易满足人工智能、加密等应用领域的需求。

为了增加读出电流的乱度,现有技术的方法是使用额外的控制电路对不同位置的存储器单元施加不同的电压。然而,这样的方法需要复杂的电路设计,大幅提高制造工艺复杂度、生产时间与生产成本。再者,此额外的控制电路也会占据较大的可用空间,而不利于存储器装置的微小化。

对存储器产业的业者而言,为了满足人工智能、加密等应用领域的需求,并且降低制造工艺复杂度、生产时间与生产成本,仍有需要对电阻式随机存取存储器及其制造工艺进行改良。

发明内容

本发明实施例提供一种电阻式随机存取存储器及其制造方法,能够明显增加电阻式随机存取存储器的读出电流的乱度,并且降低制造工艺的复杂度、生产成本及生产时间。

本发明的一实施例揭示一种电阻式随机存取存储器,包括:层间介电层,位于基板上;第一底部接触结构及第二底部接触结构,位于层间介电层中,其中第一底部接触结构的顶表面、第二底部接触结构的顶表面及层间介电层的顶表面共平面;第一存储器单元,位于第一底部接触结构上,其中第一存储器单元包括第一底电极层,且第一底电极层包括第一导电区域,其中第一导电区域垂直投影于第一底部接触结构的图样为第一投影图样;以及第二存储器单元,位于第二底部接触结构上,其中第二存储器单元包括第二底电极层,且第二底电极层包括第二导电区域,其中第二导电区域垂直投影于第二底部接触结构的图样为第二投影图样,且其中第二投影图样不同于第一投影图样。

本发明的一实施例揭示一种电阻式随机存取存储器的制造方法,包括:形成层间介电层于基板中;形成第一底部接触结构及第二底部接触结构于层间介电层中,其中第一底部接触结构的顶表面、第二底部接触结构的顶表面及层间介电层的顶表面共平面;形成第一存储器单元于第一底部接触结构上,其中第一存储器单元包括第一底电极层,且第一底电极层包括第一导电区域,其中第一导电区域垂直投影于第一底部接触结构的图样为第一投影图样;以及形成第二存储器单元于第二底部接触结构上,其中第二存储器单元包括第二底电极层,且第二底电极层包括第二导电区域,其中第二导电区域垂直投影于第二底部接触结构的图样为第二投影图样,且其中第二投影图样不同第一投影图样。

在本发明实施例所提供的电阻式随机存取存储器的制造方法中,通过经过图案化的底电极层以及底电极层的导电区域与底部接触结构之间的对准偏差,可使位在一个存储器单元中的底电极层的导电区域垂直投影于底部接触结构的投影图样不同于位在另一个存储器单元中的底电极层的导电区域垂直投影于底部接触结构的投影图样。导电路径主要会形成在电阻转换层中对应于上述投影图样的位置。即使有导电路径形成在电阻转换层的其他位置中,导电路径的数量也明显较少。再者,存储器单元的接触电阻会随着底电极层的导电区域与底部接触结构的接触面积不同而有差异。因此,可大幅增加电阻式随机存取存储器的读出电流的乱度,而不需要使用额外的控制电路。因此,能够降低制造工艺的复杂度、生产成本及生产时间,并且有利于存储器装置的微小化。

附图说明

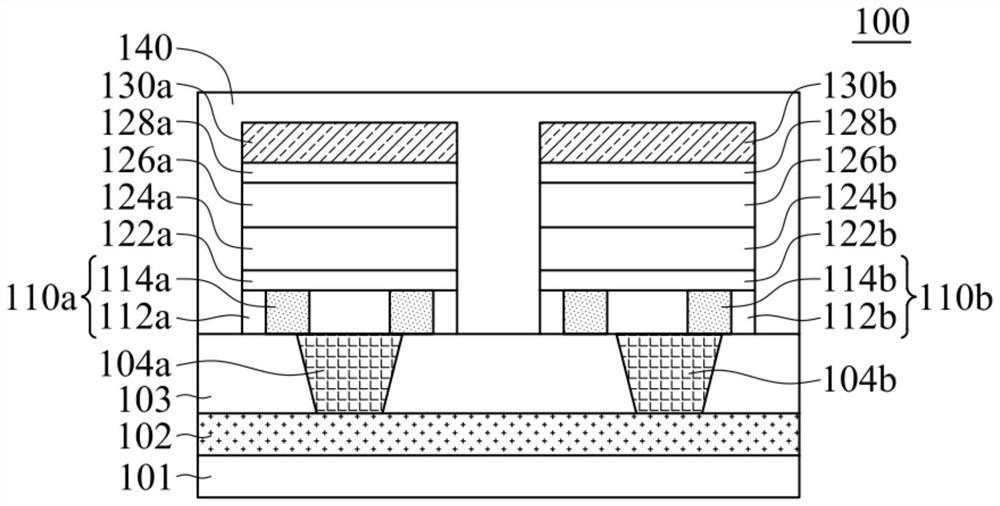

图1A至图1D为本发明一些实施例的制造电阻式随机存取存储器的各步骤中所对应的剖面示意图;

图2为本发明一些实施例的电阻式随机存取存储器的上视示意图;

图3为本发明另一些实施例的电阻式随机存取存储器的上视示意图;

图4A至图4D为本发明另一些实施例的底电极层的上视示意图;

图5为本发明另一些实施例的电阻式随机存取存储器的上视示意图;

图6为本发明一些实施例的光刻制造工艺的流程图。

符号说明

100、200、300~电阻式随机存取存储器

101~基板 102~导线

103~层间介电层 104a~第一底部接触结构

104b~第二底部接触结构 104c~第三底部接触结构

104d~第四底部接触结构 105~开口

110~底电极层 110a~第一底电极层

110b~第二底电极层 110c~第三底电极层

110d~第四底电极层 112~绝缘材料层

112a~第一绝缘区域 112b~第二绝缘区域

112c~第三绝缘区域 112d~第四绝缘区域

114~底电极材料 114a~第一导电区域

114b~第二导电区域 114c~第三导电区域

114d~第四导电区域 124~电阻转换材料

122、128~扩散阻挡材料 126~氧离子储藏材料

128~顶电极材料 140~保护层

124a、124b~电阻转换层 126a、126b~氧离子储藏层

130a、130b~顶电极层 W1、W2~边长

122a、122b~第一氧离子扩散阻挡层

128a、128b~第二氧离子扩散阻挡层

602、604、606、608~步骤

具体实施方式

为使本发明的目的、特征、优点能更明显易懂,下文特举出较佳实施例,并配合所附图式,作详细说明如下。

图1A至图1D为本发明一些实施例的制造电阻式随机存取存储器100的各步骤中所对应的剖面示意图。请参照图1A,形成层间介电层103于基板101上。基板101的材料可包括块材半导体基板(例如,硅基板)、化合物半导体基板(例如,IIIA-VA族半导体基板)、绝缘层上覆硅(silicon on insulator,SOI)基板等。基板101可为经掺杂或未经掺杂的半导体基板。在一些实施例中,基板101为硅基板。层间介电层103可为合适的绝缘材料,例如,氮化物、氧化物或氮氧化物。在一些实施例中,层间介电层103为氧化硅。

接着,形成多个导线102及多个底部接触结构于层间介电层103中。在图中,例示了两个底部接触结构104a、104b,然而本发明不以此为限。详细而言,可通过罩幕层(未绘示)将层间介电层103图案化,以形成多个沟槽于层间介电层103中。接着,将第一导电材料填入沟槽中,并且通过平坦化制造工艺(例如,化学机械抛光制造工艺)移除位于层间介电层103上的多余的第一导电材料,以形成导线102于层间介电层103中。形成导线102之后,再次沉积层间介电层103并将其图案化,以形成多个接触孔于层间介电层103中。相似地,可将第二导电材料填入接触孔中,并且通过平坦化制造工艺移除位于层间介电层103上的多余的第二导电材料,以形成底部接触结构104a、104b于层间介电层103中。可通过合适的干式刻蚀制造工艺(例如,等离子体刻蚀制造工艺)形成沟槽及接触孔。

在上视图(例如,图2)中,多个导线102彼此平行且沿着第一方向(即,水平方向)延伸。如图1A所示,导线102形成于底部接触结构104a、104b的正下方,且导线102电性连接至底部接触结构104a、104b。应可理解的是,图1A及图2所示的导线102的位置及其延伸方向仅用于说明,并非用以限定本发明。

在一些实施例中,第一导电材料包括钨、铝、铜、银、其他合适的金属或上述的组合。在另一些实施例中,第二导电材料与第一导电材料不同,且第二导电材料为双层结构,且包括衬层及导电填充材料。衬层可改善导电填充材料与基板101或层间介电层103的粘着性,且可避免金属原子扩散进入基板101或层间介电层103中。衬层的材料可包括钛、氮化钛、氮化钨、钽或氮化钽或上述的组合。导电填充材料包括钨、铜、钽、铝或上述的组合。

接着,形成绝缘材料层112于基板101及层间介电层103上。之后,进行光刻制造工艺,以图案化绝缘材料层112,从而形成多个开口105于绝缘材料层112中。如图1A所示,开口105部分地暴露出底部接触结构104a、104b的顶表面。请同时参照图1A及图2,相对于这些开口105,底部接触结构104a的顶表面所被暴露出的面积为第一暴露面积,底部接触结构104b的顶表面所被暴露出的面积为第二暴露面积,且第二暴露面积不同于第一暴露面积。如此将可有利于增加读出电流的乱度,此部分将于下文中详述。绝缘材料层112可为合适的绝缘材料,例如,氮化物、氧化物或氮氧化物。在一些实施例中,绝缘材料层112为氧化硅。可通过合适的干式刻蚀制造工艺(例如,等离子体刻蚀制造工艺)形成开口105。

请参照图1B,填入底电极材料114于开口105中,使底电极材料114与底部接触结构104a、104b电性连接。接着,进行平坦化制造工艺(例如,化学机械抛光制造工艺),使底电极材料114的顶表面与绝缘材料层113的顶表面共平面。底电极材料114可为钛、钽、氮化钛、氮化钽、其他合适的导电材料或上述的组合。在一些实施例中,底电极材料114为氮化钛。在另一些实施例中,底电极材料114为钛。可利用物理气相沉积制造工艺、化学气相沉积或其他合适的沉积制造工艺,以形成底电极材料114于开口105中。

请参照图1C,沉积扩散阻挡材料122于绝缘材料层112与底电极材料114上。扩散阻挡材料122可用于阻挡并限制氧离子的移动。因此,可避免氧离子从后续形成的电阻转换材料124扩散进入底电极材料114,而导致底电极材料114氧化。扩散阻挡材料122可包括氧化铝(Al

接着,形成电阻转换材料124于扩散阻挡材料122上。电阻转换材料124可包括过渡金属氧化物,例如,氧化铝(Al

接着,可视需要形成氧离子储藏材料126于电阻转换材料124上。氧离子储藏材料126可用于储存来自于电阻转换材料124中的氧离子。氧离子储藏材料126可包括钛(Ti)、钽(Ta)、铪(Hf)、锆(Zr)。在一些实施例中,氧离子储藏材料126为钛。

接着,可视需要形成扩散阻挡材料128于氧离子储藏材料126上。扩散阻挡材料128可避免氧离子从电阻转换材料124或氧离子储藏材料126扩散进入后续形成的顶电极材料130中,从而导致顶电极材料130氧化。扩散阻挡材料128可与扩散阻挡材料122相同或相似。在一些实施例中,扩散阻挡材料128的材料为氧化铝(Al

在本实施例中,氧离子储藏材料126及扩散阻挡材料128依序形成于电阻转换材料124上。应注意的是,可视需要增加或省略氧离子储藏材料126及/或扩散阻挡材料128。

接着,形成顶电极材料130于扩散阻挡材料128上。顶电极材料130可包括钛、钽、氮化钛、氮化钽、其他合适的导电材料或上述的组合。顶电极材料130可为由单一材料所形成的单层结构或由多种不同材料所形成的多层结构。在一些实施例中,顶电极材料130为由氮化钛所形成的单层结构。可利用物理气相沉积制造工艺、化学气相沉积、原子层沉积制造工艺或其他合适的沉积制造工艺,以各自独立地形成扩散阻挡材料122、电阻转换材料124、氧离子储藏材料126、扩散阻挡材料128及顶电极材料130。

请参照图1D,图案化顶电极材料130、扩散阻挡材料128、氧离子储藏材料126、电阻转换材料124、扩散阻挡材料122及底电极材料110,以形成第一存储器单元于底部接触结构104a上,并形成第二存储器单元于底部接触结构104b上。其中,第一存储器单元包括底电极层110a、第一氧离子扩散阻挡层122a、电阻转换层124a、氧离子储藏层126a、第二氧离子扩散阻挡层128a及顶电极层130a。顶电极层130a决定底电极层110a的范围。底电极层110a包括第一绝缘区域112a与第一导电区域114a。第二存储器单元包括底电极层110b、第一氧离子扩散阻挡层122b、电阻转换层124b、氧离子储藏层126b、第二氧离子扩散阻挡层128b及顶电极层130b。顶电极层130b决定底电极层110b的范围。底电极层110b包括第二绝缘区域112b与第二导电区域114b。接着,形成保护层140覆盖第一存储器单元与第二存储器单元。保护层140可为由单一材料所形成的单层结构或由多种不同材料所形成的多层结构。在一些实施例中,保护层140为由氢氧阻挡层及形成于氢氧阻挡层上的间隔层所形成的双层结构。在这样的实施例中,氢氧阻挡层可避免氢气或氧气进入基板101或存储器单元的各层中,因而可避免电阻式随机存取存储器的劣化或失效。氢氧阻挡层的材料可为金属氧化物(例如,氧化铝)、金属氮化物、金属氮氮化物、氮化物、氮氧化物或上述的组合。间隔层可减少或避免存储器单元在后续制造工艺中受到损伤。间隔层的材料可为氮化物或氮氧化物,例如为二氧化硅。在另一些实施例中,氢氧阻挡层的功能及材料可与间隔层的功能及材料相同或相似。保护层140可包括氧化铝、氮化铝、氮化硅、氮氧化硅或上述的组合。在本实施例中,保护层140为由氧化铝(Al

之后,可进行其他现有技术的制造工艺(例如,可形成顶电极接触结构于顶电极层130之上),以完成电阻式随机存取存储器100,在此不再详述。

图2为图1A至图1D的电阻式随机存取存储器100的上视示意图,且图1A至图1D是沿着图2中的剖线A-A’所绘制。由于底部接触结构104a、104b、104c、104d分别位于底电极层110a、110b、110c、110d的下方,因此,在上视图(亦即,图2、图3、图5)中以虚线绘示底部接触结构104a、104b、104c、104d。

在本实施例所提供的电阻式随机存取存储器100的制造方法中,可在不增加制造工艺的复杂度、生产成本及生产时间的前提下,大幅增加读出电流的乱度。

在形成存储器单元的制造工艺中,容易在许多步骤中发生上下层之间的对准偏差。举例而言,上述对准偏差可包括发生于光刻制造工艺或刻蚀制造工艺的对准偏差。在一般的光刻制造工艺中,是将同一片晶片分为多个区域分次进行曝光。因此,即使使用相同的光掩膜,不同次的曝光之间,仍有可能会产生对准偏差。另一方面,在刻蚀制造工艺中,即使用以定义这些存储器单元的光掩膜的开口图案均设计为相同,也有可能会产生刻蚀位置的偏差。

于现有技术的RRAM中,为了确保从阵列中的所有存储器单元所读出的电流在相同条件下具有高度均一的表现,通常会使各存储器单元中的底电极层的面积大于底部接触结构的面积,且使底电极层完全覆盖整个底部接触结构。如此一来,即使发生底电极层与底部接触结构之间的对准偏差,仍可确保每一个存储器单元与底部接触结构的接触面积皆为彼此相等。

在本发明实施例所提供的电阻式随机存取存储器的制造方法中,底电极层110a是由排列成预定图样的第一绝缘区域112a与第一导电区域114a所形成。底电极层110b是由排列成预定图样的第二绝缘区域112b与第二导电区域114b所形成。在如此的实施例中,更容易发生上述对准偏差,使这些存储器单元在相同条件的操作时的读出电流值彼此不同,而有利于应用于某些应用领域(例如,人工智能、加密等)中。

更详言之,请同时参照图1D及图2,第一导电区域114a垂直投影于底部接触结构104a的图样为第一投影图样,且此第一投影图样是由图2中位于虚线方框内的所有第一导电区域114a所组成。相似地,第二导电区域114b垂直投影于底部接触结构104b的图样为第二投影图样,且此第二投影图样是由图2中位于虚线方框内的所有第二导电区域114b所组成。

仍请参照图2,电阻式随机存取存储器100进一步包括第三存储器单元(位于左下角)及第四存储器单元(位于左下角)。第三存储器单元包括由第三导电区域114c与第三绝缘区域112c所形成的第三底电极层110c,且第四存储器单元包括由第四导电区域114d与第四绝缘区域112d所形成的第四底电极层110d。第三导电区域114c垂直投影于第三底部接触结构104c的图样为第三投影图样,且此第三投影图样是由图2中位于虚线方框内的所有第三导电区域114c所形成。第四导电区域114d垂直投影于第四底部接触结构104d的图样为第四投影图样,且此第四投影图样是由图2中位于虚线方框内的所有第四导电区域114d所形成。

在本实施例中,这些底电极层110a、110b、110c与110d具有相同的图样。然而,由于发生上述对准偏差,因此,第一投影图样、第二投影图样、第三投影图样与第四投影图样彼此不同。再者,第一导电区域114a与底部接触结构104a的接触面积(亦即,第一投影图样的总面积,此总面积相等于上述第一暴露面积)、第二导电区域114b与第二底部接触结构104b的接触面积(亦即,第二投影图样的总面积,此总面积相等于上述第二暴露面积)、第三导电区域114c与第三底部接触结构104c的接触面积(亦即,第三投影图样的总面积)与第四导电区域114d与第四底部接触结构104d的接触面积(亦即,第四投影图样的总面积)彼此不同。因此,当施加相同的操作电压时,自第一存储器单元、第二存储器单元、第三存储器单元与第四存储器单元所读取出的电流值彼此不同。如此一来,可在不明显增加制造工艺的复杂度、生产成本及生产时间的前提下,大幅增加电阻式随机存取存储器的读出电流的乱度。

在本发明实施例所提供的电阻式随机存取存储器的制造方法中,亦可视需要而使上述对准偏差发生于某些制造工艺步骤中。图6为本发明一些实施例的光刻制造工艺的流程图。在一实施例中,可依照如图6所示的流程进行如图1A所示的光刻制造工艺。请参照步骤602,使用一光掩膜在一基板的第一区域进行第一次曝光。此第一次曝光是在此光掩膜与一预定的对准记号对准后直接进行。请参照步骤604,使用此光掩膜在此基板的第二区域进行第二次曝光。此第二次曝光是在此光掩膜与预定的另一对准记号对准之后,使此光掩膜的位置产生一偏差之后再进行。可通过在平行于此基板的表面上沿着水平方向及/或垂直方向移动此光掩膜而产生上述偏差。请参照步骤606,在此基板的其他区域中,可视需要重复进行一次以上的上述第一次曝光及/或第二次曝光。请参照步骤608,当基板上的所有区域皆曝光之后,即完成此光刻制造工艺。在如此的实施例中,即使上述对准偏差并未发生,仍能够使位于不同位置的底部接触结构具有不同的暴露图样(或暴露面积)。因此,位于不同位置的存储器单元在操作时的电流值彼此不同。如此一来,可在不明显增加制造工艺的复杂度、生产成本及生产时间的前提下,大幅增加电阻式随机存取存储器的读出电流的乱度。

请参照图1D,在一些实施例中,提供一种电阻式随机存取存储器100。电阻式随机存取存储器100包括位于基板101上的导线102、层间介电层103、多个底部接触结构104a、104b与第一存储器单元及第二存储器单元。底部接触结构104a、104b位于层间介电层103中。底部接触结构104a、104b的顶表面及层间介电层103的顶表面共平面。第一存储器单元及第二存储器单元分别位于第一底部接触结构104a及第二底部接触结构104b上。第一存储器单元包括底电极层110a,且底电极层110a包括第一绝缘区域112a及第一导电区域114a。第一绝缘区域112a的顶表面与第一导电区域114a的顶表面共平面。第二存储器单元包括底电极层110b,且底电极层110b包括第二绝缘区域112b及第二导电区域114b。第二绝缘区域112b的顶表面与第二导电区域114b的顶表面共平面。底部接触结构104a直接接触第一绝缘区域112a及第一导电区域114a。底部接触结构104b直接接触第二绝缘区域112b及第二导电区域114b。第一存储器单元亦包括依序位于底电极层110a上的第一氧离子扩散阻挡层122a、电阻转换层124a、氧离子储藏层126a、第二氧离子扩散阻挡层128a及顶电极层130a。第二存储器单元亦包括依序位于底电极层110b上的第一氧离子扩散阻挡层122b、电阻转换层124b、氧离子储藏层126b、第二氧离子扩散阻挡层128b及顶电极层130b。

请同时参照图1D及图2,在本实施例中,第一导电区域114a垂直投影于第一底部接触结构104a的图样为第一投影图样。第二导电区域114b垂直投影于第二底部接触结构104b的图样为第二投影图样。第二投影图样不同于第一投影图样,且第二投影图样的总面积不同于第一投影图样的总面积。如上所述,即使不使用额外的控制电路,当施加相同的操作电压时,自第一存储器单元所读出的电流值与自第二存储器单元所读出的电流值彼此不同。藉此,可在不明显增加制造工艺的复杂度、生产成本及生产时间的前提下,大幅增加电阻式随机存取存储器100的读出电流的乱度。

请同时参照图1D及图2,在本实施例中,导线102电性连接至底部接触结构104a、104b,其中第一存储器单元中的第一绝缘区域112a与第一导电区域114a具有第一排列方式,第二存储器单元中的第二绝缘区域112b与第二导电区域114b具有第二排列方式,且第一排列方式不同于第二排列方式。

若第一氧离子扩散阻挡层122的厚度不均匀,则氧离子容易在厚度较薄的区域扩散进入底电极层110a、110b中。因此,第一氧离子扩散阻挡层122下方的平坦度(亦即,底电极层110a、110b的顶表面的平坦度)是很重要的。在本实施例中,底电极材料114为氮化钛。若是先形成底电极材料114于层间介电层103的整个表面上,则会很容易形成多个柱状结晶于底电极材料114中,导致表面不平坦。如此一来,随后的光刻制造工艺可能无法将底电极材料114图案化成预期的形状。因此,在对底电极材料114进行光刻制造工艺之前,必须对底电极材料114进行额外的平坦化制造工艺,使底电极层110a、110b具有平坦的顶表面。如此将增加制造工艺的复杂度、生产成本及时间。

相较之下,在本实施例中,是先形成绝缘材料层112,并将其图案化以形成开口105。之后,才填入底电极材料114并且进行平坦化制造工艺,以使绝缘材料层112的顶表面与底电极材料114的顶表面共平面。再者,请参照图1A,底部接触结构104a、104b及层间介电层103的顶表面共平面,如此可有利于形成厚度均一的绝缘材料层112。在本实施例中,即使绝缘材料层112形成于层间介电层103的整个表面上,绝缘材料层112的顶表面仍会是平坦的。因此,不需要进行上述额外的平坦化制造工艺而可直接对绝缘材料层112进行光刻制造工艺。再者,在本实施例中,底电极材料114是形成于深宽比为0.5至4的开口105之中,因而能够避免柱状结晶的产生。

在另一些实施例中,底电极材料114为金属(例如,钛或钽)。由于金属材料不会形成上述柱状结晶,在这样的实施例中,可以先形成底电极材料114,再形成绝缘材料层112于底电极材料114的开口中。在对底电极材料114进行光刻制造工艺之前,不需要进行上述额外的平坦化制造工艺。

此外,对于人工智能或加密等的应用而言,为了兼顾制造工艺的容易度与读出电流的乱度,可将底电极的绝缘区域及导电区域的尺寸分别控制在适当的范围。请参照图2,在一些实施例中,第一绝缘区域112a的边长W1可以是200-800nm,且第一导电区域114a的边长W2可以是60-300nm。

图3为本发明另一些实施例的电阻式随机存取存储器200的上视示意图。图3所示的电阻式随机存取存储器200与图1D所示的电阻式随机存取存储器100相似,差异在于图3的底电极层具有不同的图样。为了简化说明,关于相同于图1D所示的元件及其形成制造工艺步骤,在此不再详述。

可通过类似于图1A至图1D的制造工艺步骤形成图3所示的电阻式随机存取存储器200。在本实施例中,当进行图1A的光刻制造工艺时,可通过改变光掩膜的图案,以形成具有预定图样(如图3所示的第一导电区域114a的图样)的开口。除此之外,其余制造工艺步骤皆与图1A至图1D的制造工艺步骤相同。在本实施例中,底电极材料114为可以是金属,也可以是金属氮化物。

在另一些实施例中,当底电极材料114为金属时,可先形成底电极材料114,再将绝缘材料层112填入形成于底电极材料114的开口中。除此之外,其余制造工艺步骤皆与图1A至图1D的制造工艺步骤相同。

请参照图2,在底电极层110a中,第一导电区域114a包括多个彼此分离的导电部分(亦即,在图2中被第一绝缘区域112a所包围的5个方形区域),且第一绝缘区域112a环绕这些导电部分。如上所述,各导电部分的顶表面面积为6,000nm

请参照图3,图3绘示的底电极层110a与图2绘示的底电极层110a是彼此互补的图样。更详言之,在图3中,第一绝缘区域112a包括多个彼此分离的绝缘部分(亦即,在图3中被第一导电区域114a所包围的5个方形区域),且第一导电区域114a环绕这些绝缘部分。相较于图2,在本实施例中,第一导电区域114a与底部接触结构104a的接触面积较大。因此,可进一步降低底电极层110a与底部接触结构104a之间的接触电阻,且可有利于电阻式随机存取存储器100的操作。

图4A至图4D为本发明另一些实施例的第一底电极层110a的上视示意图。

请同时参照图2及图4A,图4A所示的底电极层110a与图2所示的底电极层110a相似,差异在于图4A的底电极层110a的导电部分的数量与排列方式不同。

请参照图4B,在底电极层110a中,第一绝缘区域112a包括多个长条状的绝缘部分,第一导电区域114a包括多个长条状的导电部分,且这些绝缘部分与这些导电部分交错排列。

请参照图4C,在底电极层110a中,第一绝缘区域112a包括多个矩形的绝缘部分,第一导电区域114a包括多个矩形的导电部分,且这些绝缘部分与这些导电部分棋盘式的交错排列。

参照图4D,在底电极层110a中,第一绝缘区域112a包括一个环状的绝缘部分,第一导电区域114a包括一个环状的导电部分及一个矩形的导电部分,且这些绝缘部分与这些导电部分交错排列。更详言之,环状的绝缘部分环绕矩形的导电部分,且环状的导电部分环绕环状的绝缘部分。

图5为本发明另一些实施例的电阻式随机存取存储器300的上视示意图。图5所示的电阻式随机存取存储器300与图1D所示的电阻式随机存取存储器100相似,差异在于图5的经过图案化的底电极层具有不同的图样。为了简化说明,关于相同于图1D所示的元件及其形成制造工艺步骤,在此不再详述。

可通过类似于图1A至图1D的制造工艺步骤形成图5所示的电阻式随机存取存储器300。在本实施例中,当进行图1A的光刻制造工艺时,可通过改变光掩膜的图案,以形成具有预定图样(如图5所示的图样)的开口105。除此之外,其余制造工艺步骤皆与图1A至图1D的制造工艺步骤相同。在本实施例中,底电极材料114为可以是金属,也可以是金属氮化物。

在另一些实施例中,当底电极材料114为金属时,可先形成底电极材料114,再将绝缘材料层112填入形成于底电极材料114的开口中。除此之外,其余制造工艺步骤皆与图1A至图1D的制造工艺步骤相同。

在本实施例中,在电阻式随机存取存储器300中,经过图案化的底电极具有彼此不同的图样。更详言之,请参照图5,电阻式随机存取存储器300的经过图案化的底电极包括4种图样。

底电极层110a包括第一绝缘区域112a及第一导电区域114a,且底电极层110a的图样相同于图2所示的底电极层110a的图样。底电极层110b包括第二绝缘区域112b及第二导电区域114b,且底电极层110b的图样相同于图4A所示的底电极层110a的图样。底电极层110c包括第三绝缘区域112c及第三导电区域114c,且底电极层110c的图样相同于图4B所示的底电极层110a的图样。底电极层110d包括第四绝缘区域112d及第四导电区域114d,且底电极层110d的图样相同于图4D所示的底电极层110a的图样。换言之,在电阻式随机存取存储器300中,第一存储器单元中的第一绝缘区域112a与第一导电区域114a具有第一排列方式;第二存储器单元中的第二绝缘区域112b与第二导电区域114b具有第二排列方式;第三存储器单元中的第三绝缘区域112c与第三导电区域114c具有第三排列方式;以及第四存储器单元中的第四绝缘区域112d与第四导电区域114d具有第四排列方式。第一排列方式、第二排列方式、第三排列方式及第四排列方式彼此不同。

在本实施例中,底电极层110a、110b、110c与110d具有彼此不同的图样。因此,不论是否发生上述对准偏差,第一投影图样、第二投影图样、第三投影图样与第四投影图样必定会彼此不同。再者,第一导电区域114a与第一底部接触结构104a的接触面积(亦即,第一投影图样的总面积)、第二导电区域114b与第二底部接触结构104b的接触面积(亦即,第二投影图样的总面积)、第三导电区域114c与第三底部接触结构104c的接触面积(亦即,第三投影图样的总面积)与第四导电区域114d与第四底部接触结构104d的接触面积(亦即,第四投影图样的总面积)也可能会彼此不同。因此,当施加操作电压时,第一存储器单元的电流值、第二存储器单元的电流值、第三存储器单元的电流值与第四存储器单元的电流值彼此不同。如此一来,可在不明显增加制造工艺的复杂度、生产成本及时间的前提下,大幅增加电阻式随机存取存储器的读出电流的乱度。

应可理解的是,图2、图3、图4A至图4D及图5所示的第一绝缘区域112a及第一导电区域114a的数量及其排列方式仅用于说明,并非用以限定本发明。

综上所述,在本发明实施例所提供的电阻式随机存取存储器的制造方法中,通过经过图案化的底电极层以及底电极层的导电区域与底部接触结构之间的对准偏差,可使位在一个存储器单元中的底电极层的导电区域垂直投影于底部接触结构的投影图样不同于位在另一个存储器单元中的底电极层的导电区域垂直投影于底部接触结构的投影图样。因此,可大幅增加电阻式随机存取存储器的读出电流的乱度。再者,通过改变光刻制造工艺时所使用的光掩膜的图案,即可形成具有预定图样的底电极层的导电区域。因此,本发明实施例所提供的制造方法,可轻易整合至现有的电阻式随机存取存储器的制造工艺中,而不需额外更换或修改生产设备。可在降低制造工艺复杂度及生产成本的前提下,大幅增加电阻式随机存取存储器的读出电流的乱度。此外,在本发明实施例所提供的电阻式随机存取存储器中,不需要使用额外的控制电路。因此,能够降低制造工艺的复杂度、生产成本及生产时间,并且有利于存储器装置的微小化。

虽然本发明已以多个较佳实施例揭露如上,然其并非用以限定本发明,任何所属技术领域中技术人员在不脱离本发明的精神和范围内,当可作任意的更动与润饰,因此本发明的保护范围当视权利要求所界定者为准。

- 电阻式随机存取存储器以及存储及检索电阻式随机存取存储器的信息的方法

- 电阻式随机存取存储器、其制造方法及其操作方法