半导体结构及其制造方法

文献发布时间:2023-06-19 11:44:10

技术领域

本发明是有关于半导体结构及其制造方法,且特别是有关于一种适用于高压操作的半导体结构及其制造方法。

背景技术

近年来,半导体结构在电脑、消费电子等领域中发展快速。目前,半导体结构技术在金属氧化物半导体场效应晶体管的产品市场中已被广泛接受,具有很高的市场占有率。半导体结构被用于各种电子应用中,例如高功率装置、个人电脑、手机、数字相机及其他电子装置。这些半导体结构一般通过在半导体基底上沉积绝缘层或介电层、导电层材料和半导体层材料,随后通过使用光刻(photolithography)工艺将各种材料层图案化以制造而成。因此,在半导体基底上形成电路装置和组件。

在这些装置中,高电子迁移率晶体管(high-electron mobility transistors,HEMTs)具有例如高输出功率和高击穿电压的优势,因此它们被广泛地使用于高功率的应用中。虽然现存的半导体结构及其形成方法可以应付它们原先预定的用途,但目前它们在结构和制法各个技术方面上仍有需要克服的问题。

以系统单封装(system in a package,SiP)为例,是将多个功能不同的晶片直接封装成具有完整功能的一个集成电路(IC),并利用打线电连接不同晶片再进行封装,以形成SiP半导体结构。虽然相较于将不同功能的集成电路整合成一个系统单晶片(system ona chip,SoC),系统单封装的工艺容易许多,但使用打线连接两元件会产生寄生电感和寄生电容,会产生较严重的噪声。例如电流变化率(change rate of input current,L*di/dt)很快的时候,会造成峰值电流(spike of current),进而限制了半导体结构的操作频率。再者,若峰值电流的上下摆幅太大,可能超过元件的临界电压而使元件受损。

发明内容

本发明的一些实施例提供一种半导体结构。半导体结构包括一基板,且基板具有第一区域和第二区域。上述半导体结构亦包含位于基板上方的一外延层。上述半导体结构亦包含设置于基板的第一区域上的一第一元件,以及设置于基板的第二区域上的一第二元件。一些实施例中,第一元件包含位于外延层上的第一栅极,以及分别位于第一栅极的相对两侧的第一源极电极和第一漏极电极,其中,一介电层形成于外延层上并覆盖第一栅极。一些实施例中,第二元件包含位于介电层上的第二栅极,以及分别位于第二栅极的相对两侧的第二源极电极和第二漏极电极,其中第二源极电极电连接第一漏极电极。上述半导体结构更包含设置于基板上的一隔离结构,且第一区域与第二区域中的外延层通过隔离结构而彼此隔绝开来。

根据一些实施例,半导体结构中的第一栅极包含p型掺杂的氮化镓,第二栅极包含金属或多晶硅。

根据一些实施例,半导体结构中的第二元件的第二栅极电连接第一元件的第一源极电极。

根据一些实施例,半导体结构中的隔离结构贯穿外延层并接触基板的顶面。

根据一些实施例,半导体结构更包括一晶种层位于基板上,其中外延层位于晶种层上。

根据一些实施例,半导体结构中的隔离结构贯穿外延层与晶种层,且隔离结构接触该基板的顶面。

根据一些实施例,半导体结构中的第一源极电极包含相互电连接的两个第一导电部,第一元件更包含一第一贯孔与前述两个第一导电部其中一者电连接,且第一贯孔穿过外延层并接触晶种层。

根据一些实施例,半导体结构中的第二源极电极包含相互电连接的两个第二导电部,第二元件更包含一第二贯孔与前述两个第二导电部其中一者电连接,且第二贯孔穿过外延层并接触晶种层。

根据一些实施例,半导体结构中的第一元件是增强型(enhanced mode)高压晶体管,第二元件是空乏型(depletion mode)高压晶体管。

根据一些实施例,半导体结构更包括一层间介电层位于外延层上且覆盖第一元件以及第二元件,其中层间介电层包含前述覆盖第一栅极的介电层以及覆盖第二栅极的另一介电层。

根据一些实施例,半导体结构更包括一第三元件设置于基板的第二区域上,第三元件包含位于介电层上的第三栅极,分别位于第三栅极的相对两侧的一第三源极电极和一第三漏极电极,其中第三元件的第三源极电极电连接至第二元件的第二漏极电极。

根据一些实施例,半导体结构中的第三元件的第三栅极电连接至第二元件的第二源极电极。

根据一些实施例,半导体结构更包括另一隔离结构设置于基板上,此隔离结构使对应于第二元件和第三元件的外延层彼此隔绝。

根据一些实施例,半导体结构中的第一元件是增强型高压晶体管,第二元件和第三元件是空乏型高压晶体管。

根据一些实施例,半导体结构中的基板包含一基底和设置于基底上的一绝缘层,且外延层位于绝缘层的上方。

本发明的一些实施例提供一种半导体结构的制造方法,包含提供一基板,且基板具有第一区域和第二区域。上述制造方法亦包含形成一外延层于基板的上方,以及形成一隔离结构于基板上,其中此隔离结构使第一区域以及第二区域中的外延层彼此隔绝。上述制造方法还包含形成一第一元件于基板的第一区域,以及形成一第二元件于基板的第二区域。一些实施例中,第一元件包含位于外延层上的第一栅极,以及分别位于第一栅极的相对两侧的第一源极电极和第一漏极电极,其中,一介电层形成于外延层上并覆盖第一栅极。一些实施例中,第二元件包含位于介电层上的第二栅极,以及分别位于第二栅极的相对两侧的第二源极电极和第二漏极电极,其中第二源极电极电连接第一漏极电极。

一些实施例中,上述半导体结构的制造方法更包括电连接第二元件的第二栅极至第一元件的第一源极电极。

一些实施例中,上述半导体结构的制造方法中,所形成的隔离结构贯穿外延层并接触基板的顶面。

一些实施例中,上述半导体结构的制造方法中,更包括形成一晶种层于该基板上,其中外延层形成于晶种层上。

一些实施例中,上述半导体结构的制造方法中,隔离结构贯穿外延层与晶种层,且隔离结构接触基板的顶面。

一些实施例中,上述半导体结构的制造方法中,第一源极电极包含相互电连接的两个第一导电部,形成第一元件的步骤更包含形成一第一导孔与前述两个第一导电部其中一者电连接,且第一导孔贯穿外延层并接触晶种层。

一些实施例中,上述半导体结构的制造方法中,第二源极电极包含相互电连接的两个第二导电部,形成第二元件的步骤更包含形成一第二导孔与前述两个第二导电部其中一者电连接,且第二导孔贯穿外延层并接触晶种层。

根据一些实施例,上述半导体结构的制造方法中,所制得的第一元件是增强型高压晶体管,第二元件是空乏型高压晶体管。

根据一些实施例,上述半导体结构的制造方法中,所制得的半导体结构更包括位于外延层上且覆盖第一元件以及第二元件的一层间介电层,其中层间介电层包含覆盖第一栅极的介电层以及覆盖第二栅极的另一介电层。

根据一些实施例,上述半导体结构的制造方法中,更包括形成一第三元件于基板的第二区域上,第三元件包含位于介电层上的一第三栅极,分别位于第三栅极的相对两侧的一第三源极电极和一第三漏极电极。其中,第三源极电极与第二漏极电极电连接。

根据一些实施例,上述半导体结构的制造方法中,所制得的第三元件的第三栅极电连接至第二元件的第二源极电极。

根据一些实施例,上述半导体结构的制造方法中,更包括形成另一隔离结构于基板上,此隔离结构使对应于第二元件和第三元件的外延层彼此隔绝。

根据一些实施例,上述半导体结构的制造方法中,所制得的第一元件是增强型高压晶体管,第二元件和第三元件是空乏型高压晶体管。

本发明可以避免传统使用打线连接不同元件所产生的寄生电感和寄生电容所造成的噪声,进而减少高电流变化率所造成的峰值电流,元件不容易受损。

为让本发明实施例的特征、和优点能更明显易懂,下文特举出较佳实施例,并配合所附图式,作详细说明如下。

附图说明

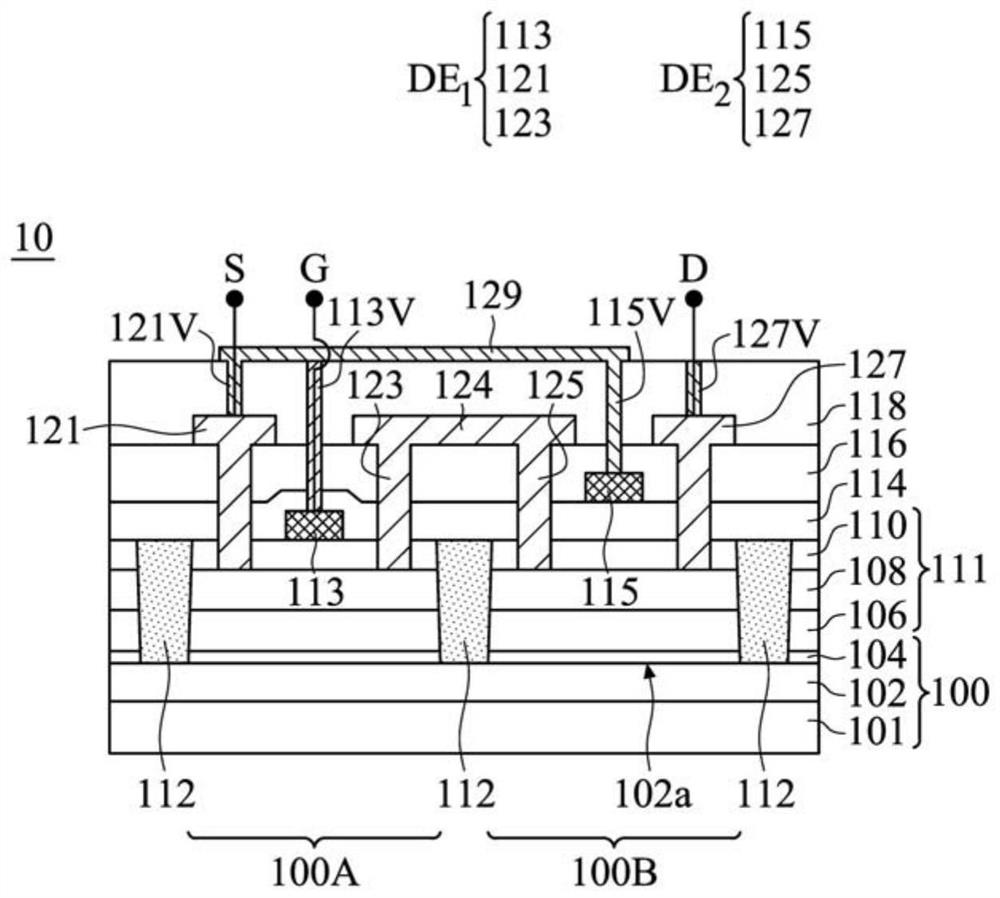

图1A-图1G是根据本发明的一些实施例,显示形成图1G的半导体结构100的各个中间阶段的剖面示意图。

图2为根据本发明一些实施例的半导体结构的剖面示意图,其中串接2个空乏型晶体管于基板的第二区域中。

图3为根据本发明一些实施例的半导体结构的剖面示意图,其中串接n个空乏型晶体管于基板的第二区域中,n为大于等于3的正整数。

图4为根据本发明的一些实施例的半导体结构的等效电路图。

图5为根据本发明一些其他的实施例的半导体结构的剖面示意图,其中各元件具有贯孔以电连接源极电极和晶种层。

图6为根据本发明一些其他的实施例的半导体结构的剖面示意图,其中各元件具有贯孔以电连接源极电极和晶种层。

附图标号

10、20、30、40、50、60~半导体结构;

100A~第一区域;

100B~第二区域;

DE

DE

DE

100~基板;

101~基底;

102~绝缘层;

102a~顶面;

104~晶种层;

106~缓冲层;

108~通道层;

110~障壁层;

111~外延层;

112h~沟槽;

112~隔离结构;

113~第一栅极;

114~第一介电层;

115~第二栅极;

115-2~第三栅极;

115-n~第(n+1)栅极;

116~第二介电层;

118~第三介电层;

121h、123h、125h、127h~开口;

121~第一源极电极;

1211~第一导电部;

1212~第二导电部;

123~第一漏极电极;

124、129~连接部;

125~第二源极电极;

1251~第三导电部;

1252~第四导电部;

125-2~第三源极电极;

125-n~第(n+1)源极电极;

127~第二漏极电极;

127-2~第三漏极电极;

127-n~第(n+1)漏极电极;

125-21、125-22、125-n1、125-n2~导电部;

113V、115V、121V、127V~导孔;

S、G、D~端点;

151~第一贯孔;

152~第二贯孔;

152-n~第(n+1)贯孔。

具体实施方式

以下揭露提供了许多的实施例或范例,用于实施所提供的半导体结构的不同元件。各元件和其配置的具体范例描述如下,以简化本发明实施例的说明。当然,这些仅仅是范例,并非用以限定本发明实施例。举例而言,叙述中若提及第一元件形成在第二元件之上,可能包含第一和第二元件直接接触的实施例,也可能包含额外的元件形成在第一和第二元件之间,使得它们不直接接触的实施例。此外,本发明实施例可能在不同的范例中重复参考数字及/或字母。如此重复是为了简明和清楚,而非用以表示所讨论的不同实施例之间的关系。

再者,在以下叙述中可使用空间上相关措辞,例如“在……之下”、“在……下方”、“下方的”、“在……上方”、“上方的”和其他类似的用语,以简化一元件或部件与其他元件或其他部件之间如图所示的关系的陈述。此空间相关措辞除了包含图式所描绘的方向,还包含装置在使用或操作中的不同方位。装置可以朝其他方向定位(旋转90度或在其他方向),且在此使用的空间相关描述可依此相应地解读。

以下描述实施例的一些变化。在不同图式和说明的实施例中,相似的元件符号被用来标明相似的元件。可以理解的是,在方法的前、中、后可以提供额外的步骤,且一些叙述的步骤可为了该方法的其他实施例被取代或删除。

本发明内容的实施例提供了半导体结构及其制造方法。一些实施例中,是在相同的基板上制作多个串接的元件,并利用隔离结构以及基板使对应不同元件的外延层相互隔绝。根据一些实施例所提出的元件串接方式,无须形成很厚的外延层也能使半导体结构实现高压元件或超高压元件的应用。而厚度下降的外延层不但减少了外延工艺的时间,也大幅减轻了基板所承受的外延层的重量,降低了外延层对基板产生的应力。再者,一些实施例所提出的半导体结构的各元件可以是承受较低电压的元件,通过上述实施例的串接方式而实现高压应用。一些实施例中,半导体结构包含串接的一个增强型晶体管和一个或多个空乏型晶体管。另外,一些实施例所提出的半导体结构的工艺是一种系统单晶片(system ona chip,SoC)的工艺,所制得的半导体结构可以避免传统使用打线连接不同元件所产生的寄生电感和寄生电容所造成的噪声,进而减少高电流变化率(change rate of inputcurrent,di/dt)所造成的峰值电流(spike of current),以进一步提高半导体结构的电性表现。因此,本发明一些实施例所提出的半导体结构及其制造方法具有改善的电子特性和良好的可靠度。

在以下的一些实施例中,是以高电子迁移率晶体管(high-electron mobilitytransistor,HEMT)作为半导体结构中元件结构的示例说明,但本发明并非以此为限,一些其他的实施例亦可使用其他类型的半导体元件。

图1A-图1G是根据本发明的一些实施例,显示形成图1G的半导体结构10的各个中间阶段的剖面示意图。

参照图1A,根据一些实施例,提供基板100。基板100包含基底101和设置于基底101上的绝缘层102。绝缘层102可提供基板100的绝缘表面。在一些实施例中,基板100包含基底101和密封(encapsulate)基底101的一复合材料层。复合材料层例如包覆住基底101的所有表面(包含上下表面和所有侧面),以提供如图1A所示的基底101上的绝缘层102。在一些实施例中,基底101包含陶瓷材料。陶瓷材料包含金属无机材料。在一些实施例,基底101可以是包含碳化硅(SiC)、氮化铝(AlN)、蓝宝石(Sapphire)或其他适合的材料。上述蓝宝石基材为氧化铝。一些实施例中,包覆住基底101的四周的复合材料层可包含单一层或多层的绝缘材料层以及/或其他合适的材料层,其中绝缘材料层例如是氧化物、氮化物、氮氧化物、或其他合适的绝缘材料。另外,在一些其他的实施例中,基底101例如可由硅(Si)、碳化硅、氮化镓(GaN)、二氧化硅(SiO2)、蓝宝石或前述的组合所形成。例如,基板100为绝缘层上覆硅(silicon on Insulator,SOI)的基板,亦即基板100包含硅基底和形成于硅基底上的绝缘层。为简化图式,在图式中的基板100仅示出基底101上方的绝缘层102的部分。于一些实施例中,基板100,其可以为单层基板或多层基板。基板100不限于绝缘层上覆硅(silicon onInsulator,SOI)的基板,也可以为硅晶圆或陶瓷基板。再者,基板100包括第一区域100A和第二区域100B。根据一些实施例,第一区域100A为后续将形成第一元件D

接着,参照图1A,在基板100上方形成晶种层(seed layer)104,并且在晶种层104上方形成外延层111。

在一些实施例中,晶种层104可由硅(Si)或其他合适的材料所形成。一些实施例中,晶种层104的形成方法可包含选择性外延成长(selective epitaxy growth,SEG)工艺、化学气相沉积(chemical vapor deposition,CVD)工艺、分子束外延工艺(molecular-beamepitaxy,MBE)、沉积经掺杂的非晶半导体(例如,Si)之后固相外延再结晶(solid-phaseepitaxial recrystallization,SPER)步骤、通过直接转贴晶种的方式、或其他合适的工艺。化学气相沉积工艺例如是气相外延(vapor-phase epitaxy,VPE)工艺、低压化学气相沉积(low pressure chemical vapor deposition,LPCVD)工艺、超高真空化学气相沉积(ultra-high vacuum chemical vapor deposition,UHV-CVD)工艺、或其他合适的工艺。

如图1A所示,在一些实施例中,以高电子迁移率晶体管作为第一区域100A和第二区域100B中所形成的元件的结构为例,外延层111包含缓冲层106、通道层108以及障壁层110。

在一些实施例中,在晶种层104上外延成长以形成缓冲层106。缓冲层106可帮助减缓后续形成于缓冲层106上方的一通道层108的应变(strain),且防止缺陷形成于上方的通道层108中。在一些实施例中,缓冲层106的材料是III-V族半导体,例如AlN、GaN、AlxGa1-xN(1 接着,在缓冲层106上外延形成通道层108。在一些实施例中,通道层108包括未掺杂的III-V族半导体材料。举例而言,通道层108可以是由未掺杂的氮化镓(GaN)所形成,但本发明并非以此为限。在一些其他的实施例中,通道层108包括氮化铝镓(AlGaN)、氮化铝(AlN)、砷化镓(GaAs)、磷化铟镓(GaInP)、砷化铝镓(AlGaAs)、磷化铟(InP)、砷化铟铝(InAlAs)、砷化铟镓(InGaAs)、其他适当的III-V族材料或上述的组合。在一些实施例中,可使用分子束外延法(MBE)、氢化物气相外延法(HVPE)、有机金属化学气相沉积法(MOCVD)、其他适当的方法或上述方法的组合,而形成通道层108。 之后,在通道层108上外延形成障壁层110。在一些实施例中,障壁层110包括未掺杂的III-V族半导体材料。举例而言,障壁层110是由未掺杂的氮化镓铝(AlxGa1-xN,其中0 在一些实施例中,通道层108与障壁层110包括相异的材料,以于通道层108与障壁层110之间形成一异质界面。通过异质材料的能隙差(band gap),可使二维电子气(two-dimensional electron gas,2DEG)(未显示)形成于此异质界面上。根据一些实施例所形成的半导体结构,例如高电子迁移率晶体管(HEMT),可利用二维电子气作为导电载子。 虽然如上述实施例,外延层111为含氮化镓的复合层,但本发明并不以此为限。除了缓冲层106、通道层108以及障壁层110,外延层111亦可包含其他层膜;例如一些其他实施例中,在缓冲层106和通道层108之间还可形成一碳掺杂层(carbon-doped layer),以提升半导体结构的击穿电压。 接着,参照图1B,在一些实施例中,形成贯穿外延层111并接触基板100的顶面的沟槽112h。如图1B所示,沟槽112h穿过障壁层110、通道层108、缓冲层106以及晶种层104,并接触基底101上的绝缘层102。于此示例中,以绝缘层102的顶面102a为基板100的顶面。再者,于一些实施例中,自基板100的上方视之,沟槽112h为相连的封闭槽(closed trench)的一部分,封闭槽可区隔出基板100的第一区域100A和第二区域100B。 沟槽112h的形成方法可包含在障壁层110上形成遮罩层(未绘示)。然后,通过实施图案化工艺将遮罩层图案化以形成图案化的遮罩(未绘示)。图案化工艺包含光刻工艺和刻蚀工艺。光刻工艺包含光刻胶涂布(例如旋转涂布)、软烤、遮罩对准、曝光、曝光后烘烤、光刻胶显影、洗涤和烘干(例如硬烤)。刻蚀工艺包含干式刻蚀或湿式刻蚀。结果,图案化的遮罩暴露出障壁层110的一部分。然后,使用图案化的遮罩为遮罩,实施干式刻蚀工艺、湿式刻蚀工艺、或使用干式和湿式两种工艺的搭配,以形成沟槽112h。 然后,参照图1C,于一些实施例中,在沟槽112h内填入一种或多种绝缘材料以形成隔离结构112,以及在第一区域100A中的外延层111上(例如障壁层110上)形成第一栅极113。 一些实施例中,在沟槽112h内填入的绝缘材料例如包含氮化物、氧化物、或前述的组合,以形成隔离结构112。隔离结构112的材料可由原子层沉积(atomic layerdeposition,ALD)、化学气相沉积、旋涂式玻璃(spin-on glass,SOG)、流动式化学气相沉积(flowable chemical vapor deposition,FCVD)、高密度等离子体化学气相沉积或类似工艺,而形成隔离结构112。一些其他的实施例中,隔离结构112可包括衬层(liner)于沟槽112h的侧壁。所使用的衬层材料视工艺、元件的需求,包括了金属及/或介电质材料。 再者,于一些实施例中,自基板100的上方视之,隔离结构112为相连的封闭结构(closed structure)的一部分,所构成的封闭结构可区隔出基板100的第一区域100A和第二区域100B。例如图1C所示,最左边的隔离结构112与中间的隔离结构112分别是围绕第一区域100A的封闭结构的左侧壁和右侧壁的一部分,而位于中间的隔离结构112与最右边的隔离结构112分别是围绕第二区域100B的封闭结构的左侧壁和右侧壁的一部分。一些实施例中,封闭结构的上视形状为方形、长方形、或其他适合的形状。本发明对于封闭结构的上视形状及其围绕而成的区域面积(即第一区域100A和第二区域100B的大小)并不特别限制,可视实际应用的半导体结构的配置需求而任意的变化和调整。 然后,再参照图1C,于一些实施例中,在第一区域100A中的障壁层110上形成第一栅极113,并且在障壁层110上形成第一介电层114。第一介电层114顺应性地(conformally)覆盖隔离结构112和第一栅极113。如图1C所示,第一栅极113直接接触障壁层110。 在一些实施例中,第一栅极113可由P型掺杂的氮化镓(p-GaN)制成。一些其他的实施例中,第一栅极113可包含P型掺杂的氮化铝镓(AlGaN)、氮化镓(GaN)、氮化铝(AlN)、砷化镓(GaAs)、磷化铟镓(GaInP)、砷化铝镓(AlGaAs)、磷化铟(InP)、砷化铟铝(InAlAs)、砷化铟镓(InGaAs)、其他合适的III-V族材料或前述的组合。此外,第一栅极113的形成方法可包含前述的沉积或外延工艺,以及离子植入(ion implantation)或原位(in-situ)掺杂工艺。 在一些实施例中,第一介电层114可由氧化硅、氮化硅、氮氧化硅、氧化铝或其他合适的介电材料制成,其中第一介电层114厚度为约1埃 之后,参照图1D,于一些实施例中,在第二区域100B中的第一介电层114上形成第二栅极115,并且在第一介电层114上形成第二介电层116。其中,第二栅极115直接接触第一介电层114。第二介电层116则顺应性地(conformally)覆盖隔离结构112和第二栅极115。 在一些实施例中,第二栅极115可包括金属材料、金属硅化物、多晶硅、其他适当的导电材料或上述的组合。金属材料例如镍(Ni)、金(Au)、铂(Pt)、钯(Pd)、铱(Ir)、钛(Ti)、铬(Cr)、钨(W)、铝(Al)、铜(Cu)前述的组合或其他合适的材料。一些实施例中,第二栅极115可由原子层沉积、化学气相沉积、物理气相沉积(如溅射)或类似工艺形成。另外,在一些实施例中,第二介电层116的工艺和材料可相似或相同于第一介电层114的工艺和材料,在此便不重复叙述。 在一些实施例中,第一栅极113为一p-GaN栅极,且第一栅极113与后续在第一栅极113两侧形成的第一源极电极121以及第一漏极电极123(图1F)可构成一增强型(enhancedmode,E-mode)元件。而第二栅极115为一金属栅极,且第二栅极115与后续在第二栅极115两侧形成的第二源极电极125以及第二漏极电极127(图1F)可构成一空乏型(depletionmode,D-mode)元件。 接着,如图1E所示,在一些实施例中,对前述包含第二介电层116、第一介电层114以及障壁层110等材料层进行图案化步骤,以在第一区域100A中形成开口121h和123h以及在第二区域100B中形成开口125h和127h。 于此示例,第一区域100A中的开口121h和123h分别位于第一栅极113的相对两侧,以于后续形成第一元件DE 一些实施例中,可通过一遮罩层(未显示)以及刻蚀工艺,同时形成开口121h、123h、125h和127h。刻蚀工艺例如干式刻蚀工艺,例如反应性离子刻蚀(reactive ionetch,RIE)、电子回旋共振式(electron cyclotron resonance,ERC)刻蚀、感应耦合式等离子体(inductively-coupled plasma,ICP)刻蚀或类似干式刻蚀工艺。 在一些实施例中,可使用包含刻蚀腔室的刻蚀设备提供刻蚀工艺所使用的刻蚀剂的供气系统、可施加偏压功率至刻蚀腔室的偏压功率产生源(bias power generator)、晶圆载台、可均匀地分散刻蚀剂的喷洒头以及可在刻蚀工艺中即时监控所希望移除的材料层的刻蚀信号的刻蚀终点检测器。进行刻蚀工艺时,刻蚀剂在刻蚀腔室中受到偏压电场的加速,且朝着晶圆载台的方向,对于第二介电层116、第一介电层114以及障壁层110进行非等向性(anisotropic)刻蚀。 形成开口121h、123h、125h和127h之后,可实施灰化工艺,以移除遮罩层。 接着,如图1F所示,在一些实施例中,在开口121h、123h、125h和127h中沉积适当导电材料,并搭配图案化步骤,以分别形成第一元件和第二元件的源极电极以及漏极电极。 在一些实施例中,沉积的导电材料例如是金(Au)、镍(Ni)、铂(Pt)、钯(Pd)、铱(Ir)、钛(Ti)、铬(Cr)、钨(W)、铝(Al)、铜(Cu)、氮化钽(TaN)、氮化钛(TiN)、硅化钨(WSi 如图1F所示,在一些实施例中,第一区域100A中的第一源极电极121以及第一漏极电极123位于通道层108上且与通道层108电性接触;第二区域100B中的第二源极电极125以及第二漏极电极127位于通道层108上且与通道层108电性接触。 一些实施例中,可由原子层沉积(ALD)、化学气相沉积(CVD)、物理气相沉积(physical vapor deposition,PVD)、电子束蒸镀(electron beam evaporation)、溅射或类似工艺进行导电材料的沉积。在一些实施例中,沉积形成源极电极/漏极电极的材料层后,更包含进行高温热工艺例如快速热退火(rapid thermal annealing)工艺,以形成源极漏极欧姆接触。 如图1F所示,形成于第一区域100A的第一元件DE 值得注意的是,根据本发明的一些实施例,第一元件DE 之后,参照图1G,于一些实施例中,在第二介电层116上形成第三介电层118。如图1G所示,第三介电层118顺应性地覆盖第一元件DE 接着,如图1G所示,于一些实施例中,在第一元件DE 根据本发明的一些实施例,第二区域100B中第二元件DE 根据一些实施例,上述提出的半导体结构通过串接(cascade)的方式将多个元件相互连接,以实现高压应用的可能性。在一些实施例中,在第一区域100A中形成的元件例如是增强型晶体管(例如第一元件DE 根据上述本发明的一些实施例,通过如上述图1G的半导体结构10所示的串接方式,外延层111只需具有承受约650V的能力,且可以在相同的基板上制作出可承受约650V的第一元件DE 因此,根据上述本发明的一些实施例所提出的半导体结构10的串接方式,无须形成很厚的外延层111也能使半导体结构10实现高压元件或超高压元件的应用。例如,一个第一元件DE 再者,本发明一些实施例提出一种容易实现且制造成本低的系统单晶片(SoC)的半导体结构的工艺。如上述图1A-图1G所示的半导体结构的制造方法,在相同的基板100上制作第一元件DE 根据本发明一些实施例,可以在第二区域100B中串接多个空乏型(D-mode)晶体管,使串接后形成的半导体结构可以实现高压或超高压的操作。 图2为根据本发明一些实施例的半导体结构的剖面示意图。图2的半导体结构20与上述图1G的半导体结构10的差异在于,半导体结构20的第二区域100B中串接了两个空乏型晶体管,可降低各颗晶体管需承受的电压、或是提高半导体结构20可应用的电压。图2中相同于前述图1A-图1G的部件使用相同或类似的标号并省略其说明。 如图2所示,一些实施例中,半导体结构20包含一个增强型(E-mode)晶体管例如第一元件DE 一些实施例中,第三元件DE 再者,三个元件之间的串接相似于上述示例的串接方式。例如,在一些实施例中,第一元件DE 再者,位于基板100的第二区域100B上的元件(例如空乏型晶体管),其栅极电连接下一颗晶体管的源极电极。例如,在一些实施例中,第二元件DE 根据图2的半导体结构20,通过如上述图2所示的串接方式,若需要实现1200V的高压应用时,则外延层111只需具有承受约450V的能力,且可以在相同的基板上制作出可承受约450V的第一元件DE 再者,于一些实施例的半导体结构中,串接n个空乏型(D-mode)晶体管于第二区域100B中,n为大于等于3的正整数。图3为根据本发明一些实施例的半导体结构的剖面示意图。图3中相同于前述实施例的图1A-图1G和图2的部件使用相同或类似的标号,并省略其说明。 如图3所示,一些实施例中,半导体结构30包含一个增强型晶体管例如第一元件DE 再者,一些实施例中,设置于第二区域100B的多个元件具有相似的部件与配置。例如,第(n+1)元件DE 再者,三个元件之间的串接相似于上述示例的串接方式。例如,在一些实施例中,第一元件DE 再者,位于基板100的第二区域100B上的元件(例如空乏型晶体管),其栅极电连接下一颗晶体管的源极电极。例如,在一些实施例中,第二元件DE 操作如图3所示的半导体结构30时,分别于端点S施加一源极电压至第一源极电极121,于端点G施加一栅极电压至第一栅极113,以及于端点D施加一漏极电压至第(n+1)漏极电极127-n。如图3所示的半导体结构30,第一元件DE 根据图3的半导体结构30,通过如上述图3所示的串接方式,若需要实现1200V的高压应用时,则外延层111只需具有承受略大于(1200/(n+1))V的能力。例如,当n=4时,基板上共1个增强型和4个空乏型晶体管,则外延层111只需具有承受例如约280V~300V(1200/5=240V)的能力,即可稳定操作半导体结构30。并且可以在相同的基板上制作出可承受约280V~300V的第一元件DE 图4为根据本发明的一些实施例的半导体结构40的等效电路图,其中半导体结构40是串接1个增强型晶体管(第一区域100A)和5个空乏型晶体管(第二区域100B)。半导体结构40的各部件的结构请参照上述实施例如图1G、图2、图3所示的第一元件DE 另外,在基板100上串接越多的元件虽然可以降低外延层111的厚度,各元件所需承受的电压也越低。但是也增加了基板100的面积。因此,实际应用时可以考虑外延层对应增加的元件数目而减少的厚度、增加的基板的面积大小以及应用产品尺寸等多项因素而进行损益取舍(trade-off),而决定基板上欲串接的元件数目。 另外,本发明并不仅限于上述实施例所提出的半导体结构。在一些其他的实施例中,半导体结构可能包含其他的部件,以进一步提高半导体结构的电性表现。 例如,外延层111下方的晶种层104可能因等离子体刻蚀工艺而产生且累积在晶种层104中的寄生电荷。累积在晶种层104中的寄生电荷会造成动态导通电阻(dynamic R-on)上升,导致电流(I-on)下降,进而使电路失效,影响半导体结构的电性。以下提出一些其他实施例的半导体结构,以解决累积在晶种层104中的寄生电荷的问题。 图5为根据本发明一些其他的实施例的半导体结构的剖面示意图。图5中相同于前述图1G的部件使用相同或类似的标号,其相关结构、材料、工艺与元件之间的串接方式请参照上述实施例的说明,在此不再重复赘述。 图5的半导体结构50与上述图1G的半导体结构10的差异在于,半导体结构50的各元件的源极电极包含相互电连接的两个导电部,且其中一个导电部通过额外形成的贯孔而与晶种层104电连接,以释放例如因等离子体刻蚀工艺而产生且累积在晶种层104中的寄生电荷。 如图5所示,一些实施例中,第一元件DE 同样的,一些实施例中,第二元件DE 在高压操作(例如操作电压在600V以上)如图5的半导体结构50时,由于外延层111的贯孔151、152中填充的导电材料提供了累积在晶种层104中的寄生电荷的释放路径,因此可进一步解决寄生电荷在高压下随意移动而影响半导体结构的电性表现的问题。 于一些其他的实施例的半导体结构中,可于第二区域100B中串接2个或2个以上的空乏型晶体管。图6为根据本发明一些其他的实施例的半导体结构的剖面示意图。图6中相同于前述实施例的图3和图5的部件使用相同或类似的标号,并省略其说明。 如图6所示,可于半导体结构60的第二区域100B中串接n个空乏型晶体管,n例如是大于等于3的正整数。再者,一些实施例中,半导体结构60的各个元件的源极电极包含相互电连接的两个导电部(例如第一导电部1211和第二导电部1212、第三导电部1251和第四导电部1252、导电部125-21和125-22、……、导电部125-n1和125-n2)。且各个源极电极的其中一个导电部可利用穿过外延层111的贯孔(例如151、152、152-2、……、152-n)而与晶种层104电连接。 因此,在高压操作(例如操作电压在600V以上)如图6的半导体结构60时,不但具有可以减少外延层的厚度、降低各元件所需承受的电压、以及可在相同一基板上进行元件制作等前述优点,实现高压或超高压的应用,各元件的贯孔中填充的导电材料更提供了累积在晶种层104中的寄生电荷的释放路径,因此高压操作如图6所示的半导体结构60时,可以避免寄生电荷在高压下随意移动,进一步提升半导体结构的电性表现。 综合而言,本发明一些实施例提出的半导体结构,具有多个串接的晶体管元件。根据一些实施例所提出的元件串接方式,无须形成很厚的外延层也能使半导体结构实现高压元件或超高压元件的应用。而厚度下降的外延层不但减少了外延工艺的时间,也大幅减轻了基板所承受的外延层的重量,降低了外延层对基板产生的应力。再者,一些实施例所提出的半导体结构的各元件可以是承受较低电压的元件,通过上述实施例的串接方式而实现高压应用。另外,一些实施例所提出的半导体结构的工艺是一种容易实现且制造成本低的系统单晶片(SoC)的工艺。在相同的基板上制作多个元件,例如一个增强型晶体管和一个或多个空乏型晶体管相互串接,且利用隔离结构以及基底上的绝缘层使对应不同元件的外延层相互隔绝。通过如上述实施例的元件的串接方式,可以避免传统使用打线连接不同元件(例如晶体管元件)所产生的寄生电感和寄生电容所造成的噪声,进而减少高电流变化率(di/dt)所造成的峰值电流(spike of current)。峰值电流的上下摆幅越小,元件越不容易受损。另外,根据一些其他的实施例所提出的半导体结构,可更包含其他的部件,例如在贯孔中连接各元件的源极电极的导电部,以提供累积在晶种层中的寄生电荷的释放路径,以进一步提高半导体结构的电性表现。因此,本发明一些实施例所提出的半导体结构及其制造方法具有改善的电子特性和良好的可靠度。 虽然本发明的实施例及其优点已揭露如上,但应该了解的是,任何所属技术领域中相关技术人员,在不脱离本发明的精神和范围内,当可作更动、替代与润饰。此外,本发明的保护范围并未局限于说明书内所述特定实施例中的工艺、机器、制造、物质组成、装置、方法及步骤,任何所属技术领域中相关技术人员可从本发明一些实施例的揭示内容中理解现行或未来所发展出的工艺、机器、制造、物质组成、装置、方法及步骤,只要可以在此处所述实施例中实施大抵相同功能或获得大抵相同结果皆可根据本发明一些实施例使用。因此,本发明的保护范围包括上述工艺、机器、制造、物质组成、装置、方法及步骤。另外,每一权利要求构成个别的实施例,且本发明的保护范围也包括各个权利要求及实施例的组合。

- 氮化物半导体结构、氮化物半导体发光元件、氮化物半导体晶体管元件、氮化物半导体结构的制造方法以及氮化物半导体元件的制造方法

- 用于制造腔结构、制造用于半导体结构的腔结构的方法和使用该方法制造的半导体传声器