通道数可扩展的中频信号采集电路、关键模块与采集方法

文献发布时间:2023-06-19 11:45:49

技术领域

本发明通道数可扩展的中频信号采集电路、关键模块与采集方法属于信号采集处理领域。

背景技术

机械振动在自然界中无处不在,通过对机械振动的观察我们可以获得许多有用的信息。可以对机械振动进行采样发现其物理规律,以此来监测被测目标的振动情况,发现规律并运用所找到的物理规律。例如对地震波的监测实现地震预测,对航天设备振动信号的采集实现性能监测以及桥梁振动信号的采集实现桥梁安全监测等等。因此通过传感器采集中频振动信号,实现对信号的采集与检测是必不可少的。

振动采集的实际应用灵活多变,实际应用的不同环境所需要的信号采集点也不同。不同系统重新搭建,周期长成本高;如果采用完整的总线式数据采集系统如VXI、PXI又太复杂,成本昂贵。因此为解决针对性广泛通道数不同的需求,克服上述问题,利用电子技术发展的最新成果提出了类似的采集系统,适应中频信号的通道数可扩展的同步采集系统。

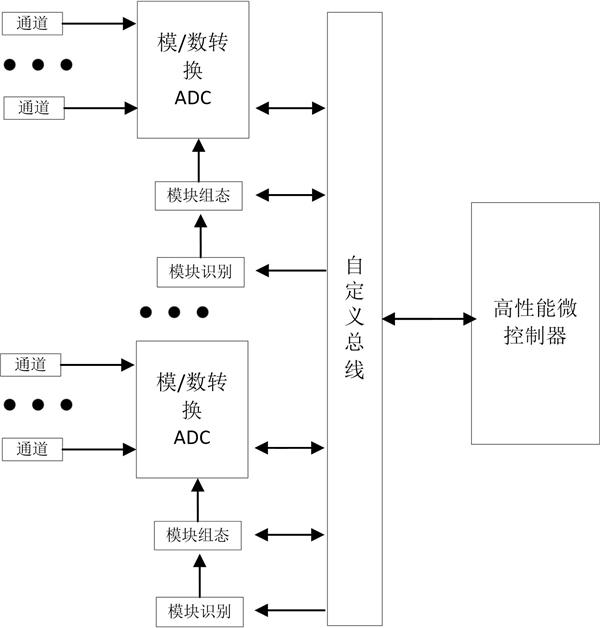

通过1块MCU模块板组合多块ADC模块板的方法,以此来实现针对多种传感器的通道数可扩展的中频信号采集系统。ADC模块板最多为8块,通道数最高可达64路且每路通道可独立工作。

发明内容

本发明的目的是通过模块组态与模块识别实现1块MCU模块板和最多8块ADC模块板的信息交互,通道数在64路内的通道数可扩展的中频信号采集系统电路,提供一种总线与MCU直接连接,MCU模块板给各个ADC模块板提供资源,采用SPI通信为主双QSPI通信从的逻辑控制方法。本发明可多路通道同步采集且每路通道也可保持其工作独立性。

本发明的目的是这样实现的:

通道数可扩展的中频信号采集电路,包括模块识别单元、公用资源单元、模块组态单元和采集数据与传输单元;

所述模块识别单元由1片4位数据比较器74HC85、1个4位拨码开关和2或3个移位寄存器74HC595组成;拨码开关为每一块ADC模块板设置物理地址,当ADC模块板接入MCU模块板时通过软件寻址实现对接入ADC模块板的识别功能;拨码开关SX1的1脚定义为COD0经电阻RX11接+3.3V,COD0接UX3的输入引脚10脚;拨码开关SX1的2脚定义为COD1经电阻RX12接+3.3V,COD1接UX3的输入引脚12脚;拨码开关SX1的3脚定义为COD2经电阻RX13接+3.3V,COD2接UX3的输入引脚13脚,SX1的4脚、5脚和6脚都接地实现对ADC模块板的编码功能;微处理器的IO口PE5通过连接器CN2经RX22连接UX3的输入脚9脚定义为RGA0;PE4通过连接器CN2经RX23连接UX3的输入脚11脚定义为RGA1;PE3通过连接器CN2经RX31连接UX3的输入脚14脚定义为RGA2;PE6通过连接器CN2经RX29连接UX8的输入脚13脚,UX8导通通过7脚输出定义为RGEN连接UX3的1脚;UX3的15脚、2脚与4脚接地,UX3的3脚接+3.3V;UX3输出引脚6脚定义为RGLD经RX24和发光二极管阳极相连,发光二接管阴极接地;UX3的6脚RGLD作为移位寄存器的锁存时钟与UX5和UX6的12脚相连接;

所述公用资源单元包含2片晶振8.192M和25M、1片基准电压源ADR4525、1片DCDC转换器、1片线性稳压器7805;通过双插孔DC输入电压产生24V电压与12V电压,24V电压接入DCDC芯片的1脚与2脚,DCDC芯片7脚与8脚输出+3.3V电压;DCDC的3脚、4脚、5脚和6脚接地,24V经过电容C50与C51并联接地,+3.3V经E2与R40并联接地;12V通过0.4A保险丝接入V1的1脚,V1的1脚经E6接地,V1的3脚输出+5V,2脚与地相连,+5V经并联电容C52与C53接地;+5V电压与基准电压源U4的2脚连接,U4的6脚输出基准电压VREF经连接器传输给ADC模块板为ADC芯片提供外部基准;接入U4的2脚的+5V经并联电容C3与C42接地,VREF经并联电容E1与C4接地;晶振X1为各块ADC模块板的ADC芯片提供时钟,晶振X1的2脚接地4脚接数字电源+3.3V,X1的3脚接上拉电阻R4输出时钟信号定义为FSYS为各ADC模块板的ADC芯片提供时钟;晶振X2为单片机STM32H7x3IIT提供时钟,X2的1脚输出定义为OSCIN与微处理器U1B的29脚PH0-OSC_IN相连,X2的3脚输出定义为OSCOUT与微处理器U1B的30脚PH1-OSC_OUT相连,OSCIN与OSCOUT之间串联电阻R7,X2的1脚经过电容C2与X2的2脚连接之后接地,X2的3脚经过电容C5与X2的4脚连接之后接地;MCU模块板中微处理器为ADC模块板提供的传输数据线ADDO、ADRDY、ADCS、ADCK、ADRST、ADDI、RGEN、RGA0、RGA1、RGA2,X1提供的时钟信号线FSYS均通过连接器CN2传输给各ADC模块板;MCU模块板中微处理器提供的BK1_IO0、BK1_IO1、BK1_IO2、BK1_IO3、BK2_IO0、BK2_IO1、BK2_IO2、BK2_IO3接上拉电阻通过连接器CN1与ADC模块板连接;MCU模块板上的基准电压VREF、+3.3V、+5V、DC24V通过连接器与ADC模块板连接;通过上述连接MCU模块板给各个ADC板提供资源包括时钟、基准、触发、总线以实现数据采集传输的同步;

所述模块组态单元由1片3组二选一开关74HC4053、1片八选一开关74HC4051、2或3片74HC595构成;对模块组态与ADC芯片的控制指令由微处理器U1C的134脚PI3输出通过电阻RX20与UX8的14脚连接,UX8的6脚输出定义为ADDI与ADC芯片的20脚DIN相连,同时与UX5的输入引脚14脚连接;UX5的并行输出引脚15脚输出SET0、1脚输出SET1、2脚输出SET2、3脚输出SET3、4脚输出SET4、5脚输出SET5、6脚输出SET6、7脚输出SET7;UX5串行输出引脚9脚级联另一个串行移位寄存器UX6的14脚,UX6并行输出信号控制调理电路的开关;MCU模块板提供的时钟信号经电阻RX18与UX8的16脚连接,导通后UX8的4脚输出定义为ADCK与ADC芯片的22脚SCLK连接,同时ADCK连接UX5与UX6的11脚时钟输入引脚;UX5与UX6的12脚锁存时钟输入引脚连接UX3的6脚RGLD,UX5与UX6的13脚/OE引脚接地使其一直处于低电平有效状态,10脚/MR主复位引脚接+3.3V电压使其一直处于高电平;当单块ADC模块板为8通道时则需要采用3个串行移位寄存器连接方式和上述内容相同,第三个移位寄存器也为模拟调理电路部分提供电源开关;

UX5并行输出的SET0连接UX1的11脚A端;SET1连接UX1的10脚B端;SET2连接UX1的9脚C端;SET3连接UX1的6脚INH端;UX1的13脚、14脚、15脚、12脚、1脚、5脚、2脚、4脚分别定义为ADDO0、ADDO1、ADDO2、ADDO3、ADDO4、ADDO5、ADDO6、ADDO7接上拉电阻通过连接器与MCU模块板的微处理器连接,UX1的3脚与ADC芯片的21脚连接定义为XDDO;XDDO也接入UX7的13脚X1端,UX7的14脚定义为ADDO通过连接器与微处理器U1C的133脚PI2连接,UX5的3脚SET3与UX7的控制引脚11脚相连控UX7的X端导通;ADC芯片19脚定义为DBOK接入UX7的1脚Y1端,UX7的15脚定义为DRDY通过连接器与微处理器U1A的40脚PA0连接,UX5的4脚SET4与UX7的控制引脚10脚相连控UX7的Y端导通;MCU模块提供的片选信号通过电阻RX17与UX8的17脚连接,导通后UX8的3脚输出定义为ADCS与UX7的3脚Z1端连接,UX7的5脚Z0端接+3.3V,UX7的4脚定义为ADEN与ADC芯片的23脚连接,UX5的5脚SET5与UX7的控制引脚9脚相连控制UX7的Z端导通;UX7的6脚、7脚、8脚接地,16脚接+3.3V电压源;

所述采集数据与传输单元由微处理器STM32H7x3IIT、模数转换芯片ADS131A04或ADS131M08构成;ADC芯片UX4其数字部分供电电压为3.3V,模拟部分工作电压为5V;当UX4选用4通道时,采集输入信号OUTA±、OUTB±、OUTC±、OUTD±分别与ADC芯片的AIN连接,UX4的30脚M0通过RX7连接+3.3V电压实现置高,31脚M1与32脚M2都与地直接连接实现置低,当UX4选用8通道时,对于信号输入部分OUTA±、OUTB±、OUTC±、OUTD±、OUTE±、OUTF±、OUTG±、OUTH±分别与ADC芯片的AIN连接,无模式选择引脚;除上述差异外UX4的4通道与8通道连接电路相同,UX4的12脚通过滤波电容CX7接地,13脚直接与地相连;UX4的14脚缓冲外部基准连接经电阻RX6连接VREF,基准电压VREF对地并联CX3与EX2,28脚CAP通过电容CX6接地;UX4的19脚DRDY_N端定义的DBOK连接UX7的1脚;微处理器U1B的PC13通过连接器经电阻RX19与UX8的15脚连接,5脚输出定义为ADRST与UX4的17脚连接;UX4的23脚CS_N端定义的ADEN连接UX7的4脚,微处理器U1C的PI0脚连接连接器CN2的4脚,U1B的110脚PG6引脚定义为BK1_NCS通过电阻R43也连接CN2的4脚,连接器CN2的4脚经过电阻RX17连接UX8的17脚,UX8的3脚输出连接UX7的3脚定义为ADCS,控制UX7的9脚就能够控制ADCS与ADEN导通;微处理器U1C的134脚PI3输出通过电阻RX20与UX8的14脚连接,UX8的6脚输出定义为ADDI与ADC芯片的20脚DIN相连;微处理器U1C的131脚PI1定义的ADCK连接到连接器CN2的5脚,微处理器U1B的28脚PF10引脚定义为QSPI_CLK,QSPI_CLK通过电阻R44也连接至连接器CN2的5脚ADCK,CN2的5脚经电阻RX18与UX8的16脚连接,UX84脚输出ADCK与UX4的22脚SCLK连接定义为ADCK;UX4的21脚DOUT端定义的XDDO连接UX7的13脚与UX1的3脚,PF9定义的BK1_IO3接上拉电阻后通过连接器CN1与UX1的ADDO3连接、PF8定义的BK1_IO2接上拉电阻后通过连接器CN1与UX1的ADDO2连接、PF7定义的BK1_IO1接上拉电阻后通过连接器CN1与UX1的ADDO1连接、PF6定义的BK1_IO0接上拉电阻后通过连接器CN1与UX1的ADDO0连接、PG9定义的BK2_IO3接上拉电阻后通过连接器CN1与UX1的ADDO7连接、PG14定义的BK2_IO2接上拉电阻后通过连接器CN1与UX1的ADDO6连接、PH3定义的BK2_IO1接上拉电阻后通过连接器CN1与UX1的ADDO5连接、PH2定义的BK2_IO0接上拉电阻后通过连接器CN1与UX1的ADDO4连接,实现双QSPI的数据线接入的选择。

通道数可扩展的中频信号采集电路关键单元,为模块识别单元,由1片4位数据比较器74HC85、1个4位4位拨码开关和2或3个移位寄存器74HC595组成;拨码开关为每一块ADC模块板设置物理地址,当ADC模块板接入MCU模块板时通过软件寻址实现对接入ADC模块板的识别功能;拨码开关SX1的1脚定义为COD0经电阻RX11接+3.3V,COD0接UX3的输入引脚10脚;拨码开关SX1的2脚定义为COD1经电阻RX12接+3.3V,COD1接UX3的输入引脚12脚;拨码开关SX1的3脚定义为COD2经电阻RX13接+3.3V,COD2接UX3的输入引脚13脚,SX1的4脚、5脚和6脚都接地实现对ADC模块板的编码功能;微处理器的IO口PE5通过连接器CN2经RX22连接UX3的输入脚9脚定义为RGA0;PE4通过连接器CN2经RX23连接UX3的输入脚11脚定义为RGA1;PE3通过连接器CN2经RX31连接UX3的输入脚14脚定义为RGA2;PE6通过连接器CN2经RX29连接UX8的输入脚13脚定,UX8导通通过7脚输出定义为RGEN连接UX3的1脚;UX3的15脚、2脚与4脚接地,UX3的3脚接+3.3V;UX3输出引脚6脚定义为RGLD经RX24和发光二极管阳极相连,发光二接管阴极接地;UX3的6脚RGLD作为移位寄存器的锁存时钟与UX5和UX6的12脚相连接。

通道数可扩展的中频信号采集电路关键单元,为公用资源单元,包含2片晶振8.192M和25M、1片基准电压源ADR4525、1片DCDC转换器、1片线性稳压器7805;通过双插孔DC输入电压产生24V电压与12V电压,24V电压接入DCDC芯片的1脚与2脚,DCDC芯片7脚与8脚输出+3.3V电压;DCDC的3脚、4脚、5脚和6脚接地,24V经过电容C50与C51并联接地,+3.3V经E2与R40并联接地;12V通过0.4A保险丝接入V1的1脚,V1的1脚经E6接地,V1的3脚输出+5V,2脚与地相连,+5V经并联电容C52与C53接地;+5V电压与基准电压源U4的2脚连接,U4的6脚输出基准电压VREF经连接器传输给ADC模块板为ADC芯片提供外部基准;接入U4的2脚的+5V经并联电容C3与C42接地,VREF经并联电容E1与C4接地;晶振X1为各块ADC模块板的ADC芯片提供时钟,晶振X1的2脚接地4脚接数字电源+3.3V,X1的3脚接上拉电阻R4输出时钟信号定义为FSYS为各ADC模块板的ADC芯片提供时钟;晶振X2为单片机STM32H7x3IIT提供时钟,X2的1脚输出定义为OSCIN与微处理器U1B的29脚PH0-OSC_IN相连,X2的3脚输出定义为OSCOUT与微处理器U1B的30脚PH1-OSC_OUT相连,OSCIN与OSCOUT之间串联电阻,X2的1脚经过电容C2与X2的2脚连接之后接地,X2的3脚经过电容C5与X2的4脚连接之后接地;MCU模块板中微处理器为ADC模块板提供的传输数据线ADDO、ADRDY、ADCS、ADCK、ADRST、ADDI、RGEN、RGA0、RGA1、RGA2,X1提供的时钟信号线FSYS均通过连接器CN2传输给各ADC模块板;MCU模块板中微处理器提供的BK1_IO0、BK1_IO1、BK1_IO2、BK1_IO3、BK2_IO0、BK2_IO1、BK2_IO2、BK2_IO3接上拉电阻通过连接器CN1与ADC模块板连接;MCU模块板上的基准电压VREF、+3.3V、+5V、DC24V通过连接器与ADC模块板连接;通过上述连接MCU模块板给各个ADC板提供资源包括时钟、基准、触发、总线以实现数据采集传输的同步。

通道数可扩展的中频信号采集电路关键单元,为模块组态单元,由1片3组二选一开关74HC4053、1片八选一开关74HC4051、2或3片74HC595构成;对模块组态与ADC芯片的控制指令由微处理器U1C的134脚PI3输出通过电阻RX20与UX8的14脚连接,UX8的6脚输出定义为ADDI与ADC芯片的20脚DIN相连,同时与UX5的输入引脚14脚连接;UX5的并行输出引脚15脚输出SET0、1脚输出SET1、2脚输出SET2、3脚输出SET3、4脚输出SET4、5脚输出SET5、6脚输出SET6、7脚输出SET7;UX5串行输出引脚9脚级联另一个串行移位寄存器UX6的14脚,UX6并行输出信号控制调理电路的开关;MCU模块板提供的时钟信号经电阻RX18与UX8的16脚连接,UX8的4脚输出定义为ADCK与ADC芯片的22脚SCLK连接,同时ADCK连接UX5与UX6的11脚时钟输入引脚;UX5与UX6的12脚锁存时钟输入引脚连接UX3的6脚RGLD,UX5与UX6的13脚/OE引脚接地使其一直处于低电平有效状态,10脚/MR主复位引脚接+3.3V电压使其一直处于高电平;当单块ADC模块板为8通道时则需要采用3个串行移位寄存器连接方式和上述内容相同,第三个移位寄存器也为模拟调理电路部分提供电源开关;

UX5并行输出的SET0连接UX1的11脚A端;SET1连接UX1的10脚B端;SET2连接UX1的9脚C端;SET3连接UX1的6脚INH端;UX1的13脚、14脚、15脚、12脚、1脚、5脚、2脚、4脚分别定义为ADDO0、ADDO1、ADDO2、ADDO3、ADDO4、ADDO5、ADDO6、ADDO7接上拉电阻通过连接器与MCU模块板的微处理器连接,UX1的3脚与ADC芯片的21脚连接定义为XDDO;XDDO也接入UX7的13脚X1端,UX7的14脚定义为ADDO通过连接器与微处理器U1C的133脚PI2连接,UX5的3脚SET3与UX7的控制引脚11脚相连控UX7的X端导通;ADC芯片19脚定义为DBOK接入UX7的1脚Y1端,UX7的15脚定义为DRDY通过连接器与微处理器U1A的40脚PA0连接,UX5的4脚SET4与UX7的控制引脚10脚相连控UX7的Y端导通;MCU模块提供的片选信号通过电阻RX17与UX8的17脚连接,UX8的3脚输出定义为ADCS与UX7的3脚Z1端连接,UX7的5脚Z0端接+3.3V,UX7的4脚定义为ADEN与ADC芯片的23脚连接,UX5的5脚SET5与UX7的控制引脚9脚相连控制UX7的Z端导通;UX7的6脚、7脚、8脚接地16脚接+3.3V电压源。

通道数可扩展的中频信号采集电路关键单元,为采集数据与传输单元,由微处理器STM32H7x3IIT、模数转换芯片ADS131A04或ADS131M08构成;ADC芯片UX4其数字部分供电电压为3.3V,模拟部分工作电压为5V;当UX4选用4通道时,采集输入信号OUTA±、OUTB±、OUTC±、OUTD±分别与ADC芯片的AIN连接,UX4的30脚M0通过RX7连接+3.3V电压实现置高,31脚M1与32脚M2都与地直接连接实现置低,当UX4选用8通道时,对于信号输入部分OUTA±、OUTB±、OUTC±、OUTD±、OUTE±、OUTF±、OUTG±、OUTH±分别与ADC芯片的AIN连接,无模式选择引脚;除上述差异外UX4的4通道与8通道连接电路相同,UX4的12脚通过滤波电容CX7接地,13脚直接与地相连;UX4的14脚缓冲外部基准连接经电阻RX6连接VREF,基准电压VREF对地并联CX3与EX2,28脚CAP通过电容CX6接地;UX4的19脚DRDY_N端定义的DBOK连接UX7的1脚;微处理器U1B的PC13通过连接器经电阻RX19与UX8的15脚连接,5脚输出定义为ADRST与UX4的17脚连接;UX4的23脚CS_N端定义的ADEN连接UX7的4脚,微处理器U1C的PI0脚连接连接器CN2的4脚,U1B的110脚PG6引脚定义为BK1_NCS通过电阻R43也连接CN2的4脚,连接器CN2的4脚经过电阻RX17连接UX8的17脚,UX8的3脚输出连接UX7的3脚定义为ADCS,控制UX7的9脚就能够控制ADCS与ADEN导通;微处理器U1C的134脚PI3输出通过电阻RX20与UX8的14脚连接,UX8的6脚输出定义为ADDI与ADC芯片的20脚DIN相连;微处理器U1C的131脚PI1定义的ADCK连接到连接器CN2的5脚,微处理器U1B的28脚PF10引脚定义为QSPI_CLK,QSPI_CLK通过电阻R44也连接至连接器CN2的5脚ADCK,CN2的5脚经电阻RX18与UX8的16脚连接,UX84脚输出ADCK与UX4的22脚SCLK连接定义为ADCK;UX4的21脚DOUT端定义的XDDO连接UX7的13脚与UX1的3脚,PF9定义的BK1_IO3接上拉电阻后通过连接器CN1与UX1的ADDO3连接、PF8定义的BK1_IO2接上拉电阻后通过连接器CN1与UX1的ADDO2连接、PF7定义的BK1_IO1接上拉电阻后通过连接器CN1与UX1的ADDO1连接、PF6定义的BK1_IO0接上拉电阻后通过连接器CN1与UX1的ADDO0连接、PG9定义的BK2_IO3接上拉电阻后通过连接器CN1与UX1的ADDO7连接、PG14定义的BK2_IO2接上拉电阻后通过连接器CN1与UX1的ADDO6连接、PH3定义的BK2_IO1接上拉电阻后通过连接器CN1与UX1的ADDO5连接、PH2定义的BK2_IO0接上拉电阻后通过连接器CN1与UX1的ADDO4连接,实现双QSPI的数据线接入的选择。

通道数可扩展的中频信号采集方法,为单一ADC模块SPI采集数据情况下的中频信号采集方法,包括以下步骤:

步骤a、对ADC内部控制寄存器写操作;

步骤a1、配置各ADC模块的移位寄存器已经且确认SET5已写操作的有效性;

步骤a2、当显示写操作有效初始化让ADC芯片的ADCS置1,关闭QSPI功能并且让RGEN为1使74HC85的P3 步骤a3、DRDY中断有效后置ADCS为低电平,启动SPI写操作;按ADC芯片使用说明通过STM32H7x3IIT对ADC芯片内部的各寄存器写操作;实现任意个工作状态相同的ADC模块的批量写操作; 步骤b、对移位寄存器写操作; 步骤b1、MCU程序首先进行控制逻辑操作,且确保ADCS为1,使所有ADC的ADDO为高组态; 步骤b2、QSPI功能关闭,RGEN为1; 步骤b3、RGA2、RGA1、RGA0设置为需要操作的ADC模块序号,启动1次16bit的SPI写操作,REGN来1个正脉冲,实现SPI的写入串行移位寄存器的数据并行加载(如8通道,则需3个移位寄存器,24bit数据长度);高8(16)位用于设置4(8)通道的电流源开关和AC/DC测量模式开关,低8位用于设置模块数据传输组态; 所述步骤a和步骤b的顺序能够调换或同步进行; 步骤c、中频信号采集; 步骤c1、配置ADC模块的移位寄存器设置为SET3置1,SET4置1,SET5置1;SET3置1使UX7的13脚X1与14脚X导通,XDDO与ADDO连接可利用SPI通信;SET4置1使UX7的1脚Y1与15脚Y导通,DBOK与DRDY导通,可通过微处理器控制引脚输出置0置1实现DRDY使能与禁用;SET5置1使UX7的3脚Z1与4脚Z导通,ADCS与ADEN导通此时对ADCS连接的IO口置高低电平就可实现控制ADC芯片使能; 步骤c2、QSPI功能关闭,RGEN为1; 步骤c3、DRDY中断有效后置ADCS为低电平,启动SPI读操作,按ADC芯片使用说明通过STM32H7x3IIT读取各通道转换数据。 通道数可扩展的中频信号采集方法,为多ADC模块QSPI采集数据情况下的中频信号采集方法,包括以下步骤: 步骤a、对ADC内部控制寄存器写操作; 步骤a1、配置各ADC模块的移位寄存器已经且确认SET5已写操作的有效性; 步骤a2、当显示写操作有效初始化让ADC芯片的ADCS置1,关闭QSPI功能并且让RGEN为1使74HC85的P3 步骤a3、DRDY中断有效后置ADCS为低电平,启动SPI写操作;按ADC芯片使用说明通过STM32H7x3IIT对ADC芯片内部的各寄存器写操作;实现任意个工作状态相同的ADC模块的批量写操作; 步骤b、对移位寄存器写操作; 步骤b1、MCU程序首先进行控制逻辑操作,且确保ADCS为1,使所有ADC的ADDO为高组态; 步骤b2、QSPI功能关闭,RGEN为1; 步骤b3、RGA2、RGA1、RGA0设置为需要操作的ADC模块序号,启动1次16bit的SPI写操作,REGN来1个正脉冲,实现SPI的写入串行移位寄存器的数据并行加载(如8通道,则需3个移位寄存器,24bit数据长度);高8(16)位用于设置4(8)通道的电流源开关和AC/DC测量模式开关,低8位用于设置模块数据传输组态; 所述步骤a和步骤b的顺序能够调换或同步进行; 步骤c、中频信号采集; 步骤c1、设置模块的移位寄存器,将每块ADC模块板的SET2、SET1、SET0与拨码开关状态保持相同; 步骤c2、SET3置0,SET4置0,SET5置1; 步骤c3、QSPI功能关闭且RGEN为1;模块识别功能开启将RGA0、RGA1、RGA2设置为与目标ADC模块板的拨码开关状态保持相同; 步骤c4、对目标操作ADC模块板的SET4为1,其他为0不更新; 步骤c5、DRDY中断有效后置ADCS为低电平,QSPI从输入功能启动,启动SPI读操作; 步骤c6、按ADC芯片使用说明通过STM32H7x3IIT读取并缓存QSPI输入数据,SPI的输入数据无用;通过控制目标ADC模块板的模块识别单元使移位寄存器锁存时钟产生上升沿起到更新并行输出更新作用,为操作的ADC模块按原来设置的并行输出信号工作。 有益效果: 第一、本发明通道数可扩展的中频信号采集系统的通道数在64路以内,采用1块MCU模块板最多携带8块ADC模块板的形式,实现通道数扩展功能;单块ADC模块板的通道数为4通道或8通道,选择接入MCU模块板的ADC模块板的通道数就能够灵活控制信号采集通道数;通过微处理器控制ADC模块板上调理电路的开关,实现对每一路通道通断与否的控制,保证64路通道内任意通道数的数据采集与独立工作。 第二、本发明的模块识别单元,通过每块ADC模块板的拨码开关对ADC模块板进行编码;当需要对目标ADC模块进行操作时,微处理器输出的RGA0、RGA1、RGA2与目标ADC的编码一致,控制RGEN输出上升沿移位寄存器并行数据输出更新完成目标ADC模块板操作,为更新的ADC模块板按原并行输出数据工作。 第三、MCU模块板为本发明通道数可扩展的中频信号采集系统的共用资源,为整个系统提供基准、时钟、总线、触发,通过公用时钟、总线、触发、基准实现对多路通道数据的采集与同步传输。 第四、微处理器对各ADC模块上的ADC内部控制寄存器进行写操作;当接入单块ADC模块板时采用SPI读取采集数据,当多块ADC模块板接入时采用QSPI读取采集数据;利用模块组态将采集的中频信号选通输出,利用SPI通信时74HC4053的数据输出端导通,QSPI通信时74HC4051的数据输出端导通,并保证将每块ADC模块板的SET2、SET1、SET0与拨码开关状态保持相同,实现单SPI的多通道单ADC模块传输和双QSPI的多通道多ADC模块传输。 附图说明 图1是多通道数可扩展的中频信号采集系统电路总框图。 图2是模块识别单元电路图。 图3是公用资源单元电路图。 图4是模块组态单元电路图。 图5是采集数据与传输单元电路图。 具体实施方式 下面结合附图对本发明具体实施方式作进一步详细介绍。 具体实施方式一 以下是本发明通道数可扩展的中频信号采集电路的具体实施方式。 本发明实现通道数可扩展的中频信号采集系统电路实现与方法的构建,如图1所示其主要电路由模块识别单元、公用资源单元、模块组态单元、采集数据与传输单元构成,具体实施方式如下文。 结合图2,由1片4位数据比较器74HC85、1个4位4位拨码开关和2或3个移位寄存器74HC595组成模块识别单元。此单元通过拨码开关为每一块ADC模块板设置物理地址,当ADC模块板接入MCU模块板时通过软件寻址实现对接入ADC模块板的识别功能。 拨码开关SX1的1脚定义为COD0经电阻RX11接+3.3V,COD0接UX3的输入引脚10脚;拨码开关SX1的2脚定义为COD1经电阻RX12接+3.3V,COD1接UX3的输入引脚12脚;拨码开关SX1的3脚定义为COD2经电阻RX13接+3.3V,COD2接UX3的输入引脚13脚,SX1的4脚、5脚和6脚都接地实现对ADC模块板的编码功能。通过控制拨码开关SX1每一路的通断来实现对COD2、COD1、COD0端口的高低电平配置,以此来达到为ADC模块板配置物理地址的目的。比较器74HC85的P输入端10脚、12脚、13脚分别与拨码开关的一端COD0、COD1、COD2相连,通过上述拨码开关的控制来对每块ADC模块板编码。P3与地相连,微处理器的IO口PE5通过连接器CN2经RX22连接UX3的输入脚9脚定义为RGA0;PE4通过连接器CN2经RX23连接UX3的输入脚11脚定义为RGA1;PE3通过连接器CN2经RX31连接UX3的输入脚14脚定义为RGA2;PE6通过连接器CN2经RX29连接UX8的输入脚13脚定,UX8导通通过7脚输出定义为RGEN连接UX3的1脚。设置比较器74HC85的输入端RGA2、RGA1、RGA0与目标ADC板的COD2、COD1、COD0的电平相同,通过控制74HC85的1脚RGEN实现6脚RGLD输出的变化。移位寄存器74HC595锁存时钟输入引脚也连接UX3的6脚RGLD,当RGLD从低电平变成高电平即STcp时钟上升沿时移位寄存器中的数据进入存储寄存器中并实现数据并行加载发送。当比较器输出端6脚输出高电平时,接入比较器74HC85的6脚与地之间的发光二极管会发光提示。比较器74HC85的15脚输入端接地固定一直为低电平,COD2、COD1、COD0电平选择共有八种情况刚好匹配MCU模块板可携带的8块ADC模块板,使每一块ADC模块板有单独的物理地址且1块MCU板最多可携带8块ADC模块板。当有多块ADC模块接入MCU模块时,对其中某块板进行识别和逻辑控制则需要利用MCU设置RGA2、RGA1、RGA0与该ADC模块板的COD2、COD1、COD0相同。再控制RGEN使输出RGLD有上升沿使移位寄存器中的数据进入存储寄存器中并实现数据并行加载更新此块ADC模块板的逻辑控制信号SET5、SET4、SET3、SET2、SET1、SET0,其余ADC板块因RGA2、RGA1、RGA0与自己的COD2、COD1、COD0不相同无法识别输出,RGLD不产生上升沿移位寄存器中的存储寄存器数据不更新,移位寄存器并行输出不改变逻辑控制信号SET5、SET4、SET3、SET2、SET1、SET0不改变。 参考图3为公用资源单元,包含2片晶振8.192M和25M、1片基准电压源ADR4525、1片DCDC转换器、1片线性稳压器7805。MCU模块板作为主板为各个携带的ADC模块板提供时钟、基准电压、总线、触发,保证ADC模块板接入时可实现同步数据传输。MCU模块板上的25M晶振为微处理器STM32H7x3IIT提供时钟,8.192M晶振为各块ADC模块板上的ADC芯片提供时钟。通过双插孔DC输入电压产生24V电压与12V电压,24V电压接入DCDC芯片的1脚与2脚,DCDC芯片7脚与8脚输出+3.3V电压为数字部分供电。DCDC的3脚、4脚、5脚和6脚接地,24V经过电容C50与C51并联接地,+3.3V经E2与R40并联接地。12V通过0.4A保险丝接入V1的1脚,V1的1脚经E6接地,V1的3脚输出+5V为模拟部分供电,2脚与地相连,+5V经并联电容C52与C53接地。+5V电压与基准电压源U4的2脚连接,U4的6脚输出基准电压VREF经连接器传输给ADC模块板为ADC芯片提供外部基准。MCU模块板为整个电路提供总线,其中包括数据总线、控制总线、地址总线。MCU模块板中微处理器为ADC模块板提供的传输数据线ADDO、ADRDY、ADCS、ADCK、ADRST、ADDI、RGEN、RGA0、RGA1、RGA2,X1提供的时钟信号线FSYS均通过连接器CN2传输给各ADC模块板。MCU模块板中微处理器提供的BK1_IO0、BK1_IO1、BK1_IO2、BK1_IO3、BK2_IO0、BK2_IO1、BK2_IO2、BK2_IO3接上拉电阻通过连接器CN1与ADC模块板连接。MCU模块板上的基准电压VREF、+3.3V、+5V、DC24V通过连接器与ADC模块板连接。微处理器芯片STM32H7x3IIT向ADC模块板发送控制指令,控制模块识别单元、模块组态单元、采集数据与传输单元,实现多通道单ADC模块或多ADC模块数据采集与传输。MCU模块板提供触发,同时触发MCU模块板所携带的单块或多块ADC模块板。 图4为模块组态单元,由1片3组二选一开关74HC4053、1片八选一开关74HC4051、2或3片74HC595构成。此发明数据传输采用SPI为主、双QSPI为从实现对多ADC模块的串行数据并行读取。对模块组态与ADC芯片的控制指令由微处理器U1C的134脚PI3输出通过电阻RX20与UX8的14脚连接,UX8的6脚输出定义为ADDI与ADC芯片的20脚DIN相连,同时与UX5的输入引脚14脚连接。UX5的并行输出引脚15脚输出SET0、1脚输出SET1、2脚输出SET2、3脚输出SET3、4脚输出SET4、5脚输出SET5、6脚输出SET6、7脚输出SET7;UX5串行输出引脚9脚级联另一个串行移位寄存器UX6的14脚,UX6并行输出信号控制调理电路的开关。MCU模块板提供的时钟信号经电阻RX18与UX8的16脚连接,UX8的4脚输出定义为ADCK与ADC芯片的22脚SCLK连接,同时ADCK连接UX5与UX6的11脚时钟输入引脚。UX5与UX6的12脚锁存时钟输入引脚连接UX3的6脚RGLD,UX5与UX6的13脚/OE引脚接地使其一直处于低电平有效状态,10脚/MR主复位引脚接+3.3V电压使其一直处于高电平。当单块ADC模块板为8通道时则需要采用3个串行移位寄存器连接方式和上述内容相同,第三个移位寄存器也为模拟调理电路部分提供电源开关。 UX5并行输出的SET0连接UX1的11脚A端;SET1连接UX1的10脚B端;SET2连接UX1的9脚C端;SET3连接UX1的6脚INH端。UX1的13脚、14脚、15脚、12脚、1脚、5脚、2脚、4脚分别定义为ADDO0、ADDO1、ADDO2、ADDO3、ADDO4、ADDO5、ADDO6、ADDO7接上拉电阻通过连接器与MCU模块板的微处理器连接,UX1的3脚与ADC芯片的21脚连接定义为XDDO,通过SET0、SET1、SET2控制XDDO与ADDO7、ADDO6、ADDO5、ADDO4、ADDO3、ADDO2、ADDO1、ADDO0导通。XDDO也接入UX7的13脚X1端,UX7的14脚定义为ADDO通过连接器与微处理器U1C的133脚PI2连接,UX5的3脚SET3与UX7的控制引脚11脚相连控制UX7的X端导通,SET3置0使74HC4051的6脚处于低电平,6脚INH低电平有效,当SET3置1时74HC85的13脚X0与14脚X导通,ADC的数据输出引脚XDDO与ADDO导通实现SPI通信,因此时74HC4051的6脚INH被置高电平其各通道不启用。ADC芯片19脚定义为DBOK接入UX7的1脚Y1端,UX7的15脚定义为DRDY通过连接器与微处理器U1A的40脚PA0连接,UX5的4脚SET4与UX7的控制引脚10脚相连控UX7的Y端导通。MCU模块提供的片选信号通过电阻RX17与UX8的17脚连接,UX8的3脚输出定义为ADCS与UX7的3脚Z1端连接,UX7的5脚Z0端接+3.3V,UX7的4脚定义为ADEN与ADC芯片的23脚连接,UX5的5脚SET5与UX7的控制引脚9脚相连控制UX7的Z端导通,UX7的6脚、7脚、8脚接地16脚接+3.3V电压源。SET5为SPI的片选信号ADC的片选连接使能信号,1使能连接、0关断,能够使任意多个ADC模块的ADC芯片针对设置状态同步读取采集数据,不同ADC模块使能实现对各ADC模块的ADC芯片差异化设置,系统中每个ADC芯片的每个寄存器均可以独立设置,提高了系统的应用灵活性。通过控制UX7的Z通道导通实现ADEN是连接3.3V还是ADCS。当ADEN与3.3V导通时片选引脚置高ADC芯片不传输数据,当与ADCS导通时可利用微处理器将ADCS置高置低实现对片选引脚的控制。SET5通过RX25连接LED0正极,LED0负极接地。当SET5被置高电平时LED0导通小灯发光,当SET5被置低电平时LED0不导通以此提示SET5的有效性。 图5为采集数据与传输单元,采集数据部分的关键ADC芯片选取4通道的ADC型号为ADS131A04,最高128kSPS采样率,选用64kSPS;8通道的ADC型号为ADS131M08,最高64kSPS采样率,晶振8.192MHz;ADC采样率可以是64kSPS及其以下,分辨率最高24bit,ADC采用SPI模式通讯,ADC的基准和控制线来自主控接口模块。ADC的作用为采集模拟信号转换为数字信号传输给MCU,其数字部分供电电压为3.3V,模拟部分工作电压为5V。ADC芯片UX4其数字部分供电电压为3.3V,模拟部分工作电压为5V。当UX4选用4通道时,采集输入信号OUTA±、OUTB±、OUTC±、OUTD±分别与ADC芯片的AIN连接,UX4的30脚M0通过RX7连接+3.3V电压实现置高,31脚M1与32脚M2都与地直接连接实现置低,当UX4选用8通道时,对于信号输入部分OUTA±、OUTB±、OUTC±、OUTD±、OUTE±、OUTF±、OUTG±、OUTH±分别与ADC芯片的AIN连接,无模式选择引脚。除上述差异外UX4的4通道与8通道连接电路相同,UX4的12脚通过滤波电容CX7接地,13脚直接与地相连;UX4的14脚缓冲外部基准连接经电阻RX6连接VREF,基准电压VREF对地并联CX3与EX2,28脚CAP通过电容CX6接地。UX4的19脚DRDY_N端定义的DBOK连接UX7的1脚;微处理器U1B的PC13通过连接器经电阻RX19与UX8的15脚连接,5脚输出定义为ADRST与UX4的17脚连接;UX4的23脚CS_N端定义的ADEN连接UX7的4脚,微处理器U1C的PI0脚连接连接器CN2的4脚,U1B的110脚PG6引脚定义为BK1_NCS通过电阻R43也连接CN2的4脚,连接器CN2的4脚经过电阻RX17连接UX8的17脚,UX8的3脚输出连接UX7的3脚定义为ADCS,控制UX7的9脚就能够控制ADCS与ADEN导通;微处理器U1C的134脚PI3输出通过电阻RX20与UX8的14脚连接,UX8的6脚输出定义为ADDI与ADC芯片的20脚DIN相连;微处理器U1C的131脚PI1定义的ADCK连接到连接器CN2的5脚,微处理器U1B的28脚PF10引脚定义为QSPI_CLK,QSPI_CLK通过电阻R44也连接至连接器CN2的5脚ADCK,CN2的5脚经电阻RX18与UX8的16脚连接,UX84脚输出ADCK与UX4的22脚SCLK连接定义为ADCK;UX4的21脚DOUT端定义的XDDO连接UX7的13脚与UX1的3脚,PF9定义的BK1_IO3接上拉电阻后通过连接器CN1与UX1的ADDO3连接、PF8定义的BK1_IO2接上拉电阻后通过连接器CN1与UX1的ADDO2连接、PF7定义的BK1_IO1接上拉电阻后通过连接器CN1与UX1的ADDO1连接、PF6定义的BK1_IO0接上拉电阻后通过连接器CN1与UX1的ADDO0连接、PG9定义的BK2_IO3接上拉电阻后通过连接器CN1与UX1的ADDO7连接、PG14定义的BK2_IO2接上拉电阻后通过连接器CN1与UX1的ADDO6连接、PH3定义的BK2_IO1接上拉电阻后通过连接器CN1与UX1的ADDO5连接、PH2定义的BK2_IO0接上拉电阻后通过连接器CN1与UX1的ADDO4连接,实现双QSPI的数据线接入的选择。 具体实施方式二 以下是本发明通道数可扩展的中频信号采集电路中模块识别单元的具体实施方式。 需要说明的是,本实施方式下的模块识别单元,既可以单独实施,又可以作为具体实施方式一中通道数可扩展的中频信号采集电路的关键模块,与其他模块协同工作。 结合图2,由1片4位数据比较器74HC85、1个4位4位拨码开关和2或3个移位寄存器74HC595组成模块识别单元。此单元通过拨码开关为每一块ADC模块板设置物理地址,当ADC模块板接入MCU模块板时通过软件寻址实现对接入ADC模块板的识别功能。 拨码开关SX1的1脚定义为COD0经电阻RX11接+3.3V,COD0接UX3的输入引脚10脚;拨码开关SX1的2脚定义为COD1经电阻RX12接+3.3V,COD1接UX3的输入引脚12脚;拨码开关SX1的3脚定义为COD2经电阻RX13接+3.3V,COD2接UX3的输入引脚13脚,SX1的4脚、5脚和6脚都接地实现对ADC模块板的编码功能。通过控制拨码开关SX1每一路的通断来实现对COD2、COD1、COD0端口的高低电平配置,以此来达到为ADC模块板配置物理地址的目的。比较器74HC85的P输入端10脚、12脚、13脚分别与拨码开关的一端COD0、COD1、COD2相连,通过上述拨码开关的控制来对每块ADC模块板编码。P3与地相连,微处理器的IO口PE5通过连接器CN2经RX22连接UX3的输入脚9脚定义为RGA0;PE4通过连接器CN2经RX23连接UX3的输入脚11脚定义为RGA1;PE3通过连接器CN2经RX31连接UX3的输入脚14脚定义为RGA2;PE6通过连接器CN2经RX29连接UX8的输入脚13脚定,UX8导通通过7脚输出定义为RGEN连接UX3的1脚。设置比较器74HC85的输入端RGA2、RGA1、RGA0与目标ADC板的COD2、COD1、COD0的电平相同,通过控制74HC85的1脚RGEN实现6脚RGLD输出的变化。移位寄存器74HC595锁存时钟输入引脚也连接UX3的6脚RGLD,当RGLD从低电平变成高电平即STcp时钟上升沿时移位寄存器中的数据进入存储寄存器中并实现数据并行加载发送。当比较器输出端6脚输出高电平时,接入比较器74HC85的6脚与地之间的发光二极管会发光提示。比较器74HC85的15脚输入端接地固定一直为低电平,COD2、COD1、COD0电平选择共有八种情况刚好匹配MCU模块板可携带的8块ADC模块板,使每一块ADC模块板有单独的物理地址且1块MCU板最多可携带8块ADC模块板。当有多块ADC模块接入MCU模块时,对其中某块板进行识别和逻辑控制则需要利用MCU设置RGA2、RGA1、RGA0与该ADC模块板的COD2、COD1、COD0相同。再控制RGEN使输出RGLD有上升沿使移位寄存器中的数据进入存储寄存器中并实现数据并行加载更新此块ADC模块板的逻辑控制信号SET5、SET4、SET3、SET2、SET1、SET0,其余ADC板块因RGA2、RGA1、RGA0与自己的COD2、COD1、COD0不相同无法识别输出,RGLD不产生上升沿移位寄存器中的存储寄存器数据不更新,移位寄存器并行输出不改变逻辑控制信号SET5、SET4、SET3、SET2、SET1、SET0不改变。 具体实施方式三 以下是本发明通道数可扩展的中频信号采集电路中公用资源单元的具体实施方式。 需要说明的是,本实施方式下的公用资源单元,既可以单独实施,又可以作为具体实施方式一中通道数可扩展的中频信号采集电路的关键模块,与其他模块协同工作。 参考图3为公用资源单元,包含2片晶振8.192M和25M、1片基准电压源ADR4525、1片DCDC转换器、1片线性稳压器7805。MCU模块板作为主板为各个携带的ADC模块板提供时钟、基准电压、总线、触发,保证ADC模块板接入时可实现同步数据传输。MCU模块板上的25M晶振为微处理器STM32H7x3IIT提供时钟,8.192M晶振为各块ADC模块板上的ADC芯片提供时钟。通过双插孔DC输入电压产生24V电压与12V电压,24V电压接入DCDC芯片的1脚与2脚,DCDC芯片7脚与8脚输出+3.3V电压为数字部分供电。DCDC的3脚、4脚、5脚和6脚接地,24V经过电容C50与C51并联接地,+3.3V经E2与R40并联接地。12V通过0.4A保险丝接入V1的1脚,V1的1脚经E6接地,V1的3脚输出+5V为模拟部分供电,2脚与地相连,+5V经并联电容C52与C53接地。+5V电压与基准电压源U4的2脚连接,U4的6脚输出基准电压VREF经连接器传输给ADC模块板为ADC芯片提供外部基准。MCU模块板为整个电路提供总线,其中包括数据总线、控制总线、地址总线。MCU模块板中微处理器为ADC模块板提供的传输数据线ADDO、ADRDY、ADCS、ADCK、ADRST、ADDI、RGEN、RGA0、RGA1、RGA2,X1提供的时钟信号线FSYS均通过连接器CN2传输给各ADC模块板。MCU模块板中微处理器提供的BK1_IO0、BK1_IO1、BK1_IO2、BK1_IO3、BK2_IO0、BK2_IO1、BK2_IO2、BK2_IO3接上拉电阻通过连接器CN1与ADC模块板连接。MCU模块板上的基准电压VREF、+3.3V、+5V、DC24V通过连接器与ADC模块板连接。微处理器芯片STM32H7x3IIT向ADC模块板发送控制指令,控制模块识别单元、模块组态单元、采集数据与传输单元,实现多通道单ADC模块或多ADC模块数据采集与传输。MCU模块板提供触发,同时触发MCU模块板所携带的单块或多块ADC模块板。 具体实施方式四 以下是本发明通道数可扩展的中频信号采集电路中模块组态单元的具体实施方式。 需要说明的是,本实施方式下的模块组态单元,既可以单独实施,又可以作为具体实施方式一中通道数可扩展的中频信号采集电路的关键模块,与其他模块协同工作。 图4为模块组态单元,由1片3组二选一开关74HC4053、1片八选一开关74HC4051、2或3片74HC595构成。此发明数据传输采用SPI为主、双QSPI为从实现对多ADC模块的串行数据并行读取。对模块组态与ADC芯片的控制指令由微处理器U1C的134脚PI3输出通过电阻RX20与UX8的14脚连接,UX8的6脚输出定义为ADDI与ADC芯片的20脚DIN相连,同时与UX5的输入引脚14脚连接。UX5的并行输出引脚15脚输出SET0、1脚输出SET1、2脚输出SET2、3脚输出SET3、4脚输出SET4、5脚输出SET5、6脚输出SET6、7脚输出SET7;UX5串行输出引脚9脚级联另一个串行移位寄存器UX6的14脚,UX6并行输出信号控制调理电路的开关。MCU模块板提供的时钟信号经电阻RX18与UX8的16脚连接,UX8的4脚输出定义为ADCK与ADC芯片的22脚SCLK连接,同时ADCK连接UX5与UX6的11脚时钟输入引脚。UX5与UX6的12脚锁存时钟输入引脚连接UX3的6脚RGLD,UX5与UX6的13脚/OE引脚接地使其一直处于低电平有效状态,10脚/MR主复位引脚接+3.3V电压使其一直处于高电平。当单块ADC模块板为8通道时则需要采用3个串行移位寄存器连接方式和上述内容相同,第三个移位寄存器也为模拟调理电路部分提供电源开关。 UX5并行输出的SET0连接UX1的11脚A端;SET1连接UX1的10脚B端;SET2连接UX1的9脚C端;SET3连接UX1的6脚INH端。UX1的13脚、14脚、15脚、12脚、1脚、5脚、2脚、4脚分别定义为ADDO0、ADDO1、ADDO2、ADDO3、ADDO4、ADDO5、ADDO6、ADDO7接上拉电阻通过连接器与MCU模块板的微处理器连接,UX1的3脚与ADC芯片的21脚连接定义为XDDO,通过SET0、SET1、SET2控制XDDO与ADDO7、ADDO6、ADDO5、ADDO4、ADDO3、ADDO2、ADDO1、ADDO0导通。XDDO也接入UX7的13脚X1端,UX7的14脚定义为ADDO通过连接器与微处理器U1C的133脚PI2连接,UX5的3脚SET3与UX7的控制引脚11脚相连控制UX7的X端导通,SET3置0使74HC4051的6脚处于低电平,6脚INH低电平有效,当SET3置1时74HC85的13脚X0与14脚X导通,ADC的数据输出引脚XDDO与ADDO导通实现SPI通信,因此时74HC4051的6脚INH被置高电平其各通道不启用。ADC芯片19脚定义为DBOK接入UX7的1脚Y1端,UX7的15脚定义为DRDY通过连接器与微处理器U1A的40脚PA0连接,UX5的4脚SET4与UX7的控制引脚10脚相连控UX7的Y端导通。MCU模块提供的片选信号通过电阻RX17与UX8的17脚连接,UX8的3脚输出定义为ADCS与UX7的3脚Z1端连接,UX7的5脚Z0端接+3.3V,UX7的4脚定义为ADEN与ADC芯片的23脚连接,UX5的5脚SET5与UX7的控制引脚9脚相连控制UX7的Z端导通,UX7的6脚、7脚、8脚接地16脚接+3.3V电压源。SET5为SPI的片选信号ADC的片选连接使能信号,1使能连接、0关断,能够使任意多个ADC模块的ADC芯片针对设置状态同步读取采集数据,不同ADC模块使能实现对各ADC模块的ADC芯片差异化设置,系统中每个ADC芯片的每个寄存器均可以独立设置,提高了系统的应用灵活性。通过控制UX7的Z通道导通实现ADEN是连接3.3V还是ADCS。当ADEN与3.3V导通时片选引脚置高ADC芯片不传输数据,当与ADCS导通时可利用微处理器将ADCS置高置低实现对片选引脚的控制。SET5通过RX25连接LED0正极,LED0负极接地。当SET5被置高电平时LED0导通小灯发光,当SET5被置低电平时LED0不导通以此提示SET5的有效性。 具体实施方式五 以下是本发明通道数可扩展的中频信号采集电路中采集数据与传输单元的具体实施方式。 需要说明的是,本实施方式下的采集数据与传输单元,既可以单独实施,又可以作为具体实施方式一中通道数可扩展的中频信号采集电路的关键模块,与其他模块协同工作。 图5为采集数据与传输单元,采集数据部分的关键ADC芯片选取4通道的ADC型号为ADS131A04,最高128kSPS采样率,选用64kSPS;8通道的ADC型号为ADS131M08,最高64kSPS采样率,晶振8.192MHz;ADC采样率可以是64kSPS及其以下,分辨率最高24bit,ADC采用SPI模式通讯,ADC的基准和控制线来自主控接口模块。ADC的作用为采集模拟信号转换为数字信号传输给MCU,其数字部分供电电压为3.3V,模拟部分工作电压为5V。ADC芯片UX4其数字部分供电电压为3.3V,模拟部分工作电压为5V。当UX4选用4通道时,采集输入信号OUTA±、OUTB±、OUTC±、OUTD±分别与ADC芯片的AIN连接,UX4的30脚M0通过RX7连接+3.3V电压实现置高,31脚M1与32脚M2都与地直接连接实现置低,当UX4选用8通道时,对于信号输入部分OUTA±、OUTB±、OUTC±、OUTD±、OUTE±、OUTF±、OUTG±、OUTH±分别与ADC芯片的AIN连接,无模式选择引脚。除上述差异外UX4的4通道与8通道连接电路相同,UX4的12脚通过滤波电容CX7接地,13脚直接与地相连;UX4的14脚缓冲外部基准连接经电阻RX6连接VREF,基准电压VREF对地并联CX3与EX2,28脚CAP通过电容CX6接地。UX4的19脚DRDY_N端定义的DBOK连接UX7的1脚;微处理器U1B的PC13通过连接器经电阻RX19与UX8的15脚连接,5脚输出定义为ADRST与UX4的17脚连接;UX4的23脚CS_N端定义的ADEN连接UX7的4脚,微处理器U1C的PI0脚连接连接器CN2的4脚,U1B的110脚PG6引脚定义为BK1_NCS通过电阻R43也连接CN2的4脚,连接器CN2的4脚经过电阻RX17连接UX8的17脚,UX8的3脚输出连接UX7的3脚定义为ADCS,控制UX7的9脚就能够控制ADCS与ADEN导通;微处理器U1C的134脚PI3输出通过电阻RX20与UX8的14脚连接,UX8的6脚输出定义为ADDI与ADC芯片的20脚DIN相连;微处理器U1C的131脚PI1定义的ADCK连接到连接器CN2的5脚,微处理器U1B的28脚PF10引脚定义为QSPI_CLK,QSPI_CLK通过电阻R44也连接至连接器CN2的5脚ADCK,CN2的5脚经电阻RX18与UX8的16脚连接,UX84脚输出ADCK与UX4的22脚SCLK连接定义为ADCK;UX4的21脚DOUT端定义的XDDO连接UX7的13脚与UX1的3脚,PF9定义的BK1_IO3接上拉电阻后通过连接器CN1与UX1的ADDO3连接、PF8定义的BK1_IO2接上拉电阻后通过连接器CN1与UX1的ADDO2连接、PF7定义的BK1_IO1接上拉电阻后通过连接器CN1与UX1的ADDO1连接、PF6定义的BK1_IO0接上拉电阻后通过连接器CN1与UX1的ADDO0连接、PG9定义的BK2_IO3接上拉电阻后通过连接器CN1与UX1的ADDO7连接、PG14定义的BK2_IO2接上拉电阻后通过连接器CN1与UX1的ADDO6连接、PH3定义的BK2_IO1接上拉电阻后通过连接器CN1与UX1的ADDO5连接、PH2定义的BK2_IO0接上拉电阻后通过连接器CN1与UX1的ADDO4连接,实现双QSPI的数据线接入的选择。 具体实施方式六 以下是本发明通道数可扩展的中频信号采集方法的具体实施方式。 本实施方式下的通道数可扩展的中频信号采集方法,为单一ADC模块SPI采集数据情况下的中频信号采集方法,包括以下步骤: 步骤a、对ADC内部控制寄存器写操作; 步骤a1、配置各ADC模块的移位寄存器已经且确认SET5已写操作的有效性; 步骤a2、当显示写操作有效初始化让ADC芯片的ADCS置1,关闭QSPI功能并且让RGEN为1使74HC85的P3 步骤a3、DRDY中断有效后置ADCS为低电平,启动SPI写操作;按ADC芯片使用说明通过STM32H7x3IIT对ADC芯片内部的各寄存器写操作;实现任意个工作状态相同的ADC模块的批量写操作; 步骤b、对移位寄存器写操作; 步骤b1、MCU程序首先进行控制逻辑操作,且确保ADCS为1,使所有ADC的ADDO为高组态; 步骤b2、QSPI功能关闭,RGEN为1; 步骤b3、RGA2、RGA1、RGA0设置为需要操作的ADC模块序号,启动1次16bit的SPI写操作,REGN来1个正脉冲,实现SPI的写入串行移位寄存器的数据并行加载(如8通道,则需3个移位寄存器,24bit数据长度);高8(16)位用于设置4(8)通道的电流源开关和AC/DC测量模式开关,低8位用于设置模块数据传输组态; 所述步骤a和步骤b的顺序能够调换或同步进行; 步骤c、中频信号采集; 步骤c1、配置ADC模块的移位寄存器设置为SET3置1,SET4置1,SET5置1;SET3置1使UX7的13脚X1与14脚X导通,XDDO与ADDO连接可利用SPI通信;SET4置1使UX7的1脚Y1与15脚Y导通,DBOK与DRDY导通,可通过微处理器控制引脚输出置0置1实现DRDY使能与禁用;SET5置1使UX7的3脚Z1与4脚Z导通,ADCS与ADEN导通此时对ADCS连接的IO口置高低电平就可实现控制ADC芯片使能; 步骤c2、QSPI功能关闭,RGEN为1; 步骤c3、DRDY中断有效后置ADCS为低电平,启动SPI读操作,按ADC芯片使用说明通过STM32H7x3IIT读取各通道转换数据。 具体实施方式七 以下是本发明通道数可扩展的中频信号采集方法的具体实施方式。 本实施方式下的通道数可扩展的中频信号采集方法,为多ADC模块QSPI采集数据情况下的中频信号采集方法,包括以下步骤: 步骤a、对ADC内部控制寄存器写操作; 步骤a1、配置各ADC模块的移位寄存器已经且确认SET5已写操作的有效性; 步骤a2、当显示写操作有效初始化让ADC芯片的ADCS置1,关闭QSPI功能并且让RGEN为1使74HC85的P3 步骤a3、DRDY中断有效后置ADCS为低电平,启动SPI写操作;按ADC芯片使用说明通过STM32H7x3IIT对ADC芯片内部的各寄存器写操作;实现任意个工作状态相同的ADC模块的批量写操作; 步骤b、对移位寄存器写操作; 步骤b1、MCU程序首先进行控制逻辑操作,且确保ADCS为1,使所有ADC的ADDO为高组态; 步骤b2、QSPI功能关闭,RGEN为1; 步骤b3、RGA2、RGA1、RGA0设置为需要操作的ADC模块序号,启动1次16bit的SPI写操作,REGN来1个正脉冲,实现SPI的写入串行移位寄存器的数据并行加载(如8通道,则需3个移位寄存器,24bit数据长度);高8(16)位用于设置4(8)通道的电流源开关和AC/DC测量模式开关,低8位用于设置模块数据传输组态; 所述步骤a和步骤b的顺序能够调换或同步进行; 步骤c、中频信号采集; 步骤c1、设置模块的移位寄存器,将每块ADC模块板的SET2、SET1、SET0与拨码开关状态保持相同; 步骤c2、SET3置0,SET4置0,SET5置1; 步骤c3、QSPI功能关闭且RGEN为1;模块识别功能开启将RGA0、RGA1、RGA2设置为与目标ADC模块板的拨码开关状态保持相同; 步骤c4、对目标操作ADC模块板的SET4为1,其他为0不更新; 步骤c5、DRDY中断有效后置ADCS为低电平,QSPI从输入功能启动,启动SPI读操作; 步骤c6、按ADC芯片使用说明通过STM32H7x3IIT读取并缓存QSPI输入数据,SPI的输入数据无用;通过控制目标ADC模块板的模块识别单元使移位寄存器锁存时钟产生上升沿起到更新并行输出更新作用,为操作的ADC模块按原来设置的并行输出信号工作。 需要说明的是,以上所述的仅为本发明的具体实例,并不用于限定本发明的保护范围,凡在本发明精神和原则之内的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 通道数可扩展的中频信号采集电路、关键模块与采集方法

- 一种可变换通道数的WDM模块封装系统