解码方法及相关的闪存控制器与电子装置

文献发布时间:2023-06-19 11:49:09

本申请是申请日为2018年08月08日、申请号为201810898689.2、发明创造名称为“解码方法及相关的闪存控制器与电子装置”的中国发明申请的分案申请。

技术领域

本发明涉及解码方法,尤其涉及一种应用在闪存控制器的解码方法。

背景技术

为了进一步提升存储装置的容量,立体NAND型闪存(3D NAND-type flash)模块被开发出来,以通过多层堆栈的制程来提升闪存的存储密度。然而,由于立体NAND型闪存模块中的位线(bit line)是具有较大宽高比(aspect ratio)的垂直线,因此其蚀刻制程并无法使得位线的每一个区段都具有相同的宽度,例如位线的上方端具有较粗的宽度,而位线的上方端则较细,因此容易造成位线与字线(word line)之间的短路,或是其他的短路/断路问题。特别地,上述短路问题可能会使得立体NAND型闪存中某些特定地址出现高可靠度错误(High Reliability Error,HRE),也就是当读取所述多个特定地址上的信息并进行软解码的过程中,会出现某些具有较高可靠度的错误位,而这些具有较高可靠度的错误位会严重影响到解码操作,并有可能造成解码失败。

发明内容

因此,本发明的目的之一在于提供一种解码方法,其可以解决闪存模块因为上述高可靠度错误而造成解码负担的问题。

在本发明的一个实施例中,公开了一种应用于一闪存控制器的解码方法,其包括有以下步骤:自一闪存模块中读取一第一数据;对所述第一数据进行解码,并根据所述第一数据的解码结果标记所述闪存模块中至少一特定地址,其中所述特定地址对应到所述第一数据中具有高可靠度错误的数据;自所述闪存模块中读取一第二数据;以及参考所述特定地址来对所述第二数据进行解码。

在本发明的另一个实施例中,公开了一种闪存控制器,其中所述闪存控制器是用来存取一闪存模块,且所述闪存控制器包括有一只读存储器、一微处理器以及一解码器,其中所述只读存储器是用来存储一程序代码,且所述微处理器是用来执行所述程序代码以控制对所述闪存模块的存取。在所述闪存控制器的操作中,所述解码器自所述闪存模块中读取一第一数据后对所述第一数据进行解码,并根据所述第一数据的解码结果标记所述闪存模块中至少一特定地址,其中所述特定地址对应到带第一数据中具有高可靠度错误的数据;所述解码器自所述闪存模块中读取一第二数据,并参考所述特定地址来对所述第二数据进行解码。

在本发明的另一个实施例中,公开了一种电子装置,其包括有一闪存模块以及一闪存控制器。在所述电子装置的操作中,所述闪存控制器自所述闪存模块中读取一第一数据后对所述第一数据进行解码,并根据所述第一数据的解码结果标记所述闪存模块中至少一特定地址,其中所述特定地址对应到所述第一数据中具有高可靠度错误的数据;所述闪存控制器自所述闪存模块中读取一第二数据,并参考所述特定地址来对所述第二数据进行解码。

附图说明

图1为依据本发明一实施例的一种记忆装置的示意图。

图2为一立体NAND型闪存的范例示意图。

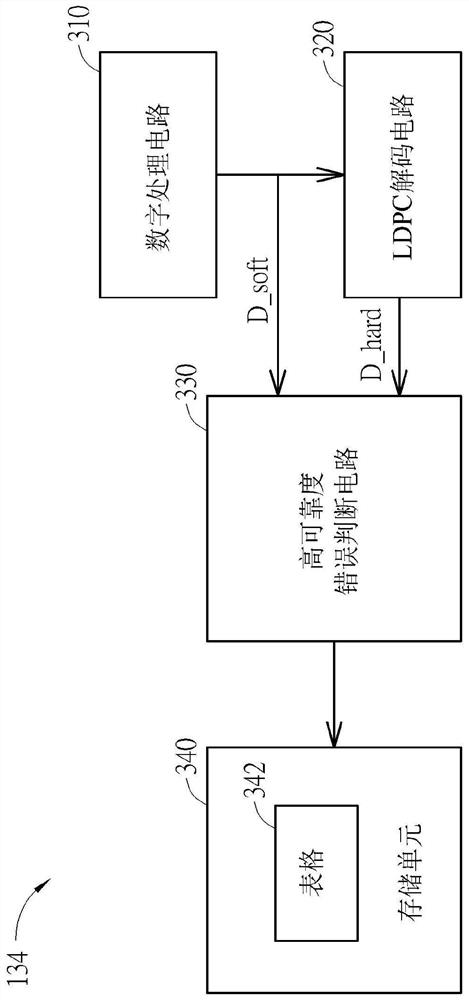

图3所示为本发明一实施例的解码器的示意图。

图4为解码器依序处理自八个浮闸晶体管所读取的数据的示意图。

图5为本发明一实施例的表格的示意图。

图6为本发明一实施例的解码方法的流程图。

其中,附图标记说明如下:

110 闪存控制器

112 微处理器

112C 程序代码

112M 只读存储器

114 控制逻辑

116 缓冲存储器

118 界面逻辑

120 闪存模块

130 主装置

132 编码器

134 解码器

202、202_1~202_8 浮闸晶体管

134 解码器

310 数字处理电路

320 LDPC解码电路

330 高可靠度错误判断电路

340 存储单元

342 表格

600~614 步骤

BL1~BL3 位线

WL0~WL2、WL4~WL6 字线

D_soft 软信息

D_hard 最终位值

具体实施方式

请参考图1,图1为依据本发明一实施例的一种记忆装置100的示意图。记忆装置100包括有一闪存(Flash Memory)模块120以及一闪存控制器110,且闪存控制器110用来存取闪存模块120。依据本实施例,闪存控制器110包括一微处理器112、一只读存储器(ReadOnly Memory,ROM)112M、一控制逻辑114、一缓冲存储器116、与一界面逻辑118。只读存储器112M是用来存储一程序代码112C,而微处理器112则用来执行程序代码112C以控制对闪存模块120的存取(Access)。控制逻辑114包括了一编码器132与一解码器134。在本实施例中,编码器132与解码器134是用来进行准循环低密度奇偶校检(Quasi-Cyclic Low DensityParty-Check,QC-LDPC)码的编解码操作。

于典型状况下,闪存模块120包括了多个闪存芯片,而每一个闪存芯片包括多个区块(Block),而所述控制器(例如:通过微处理器112执行程序代码112C的闪存控制器110)对闪存模块120进行抹除等运作是以区块为单位来进行。另外,一区块可记录特定数量的数据页(Page),其中所述控制器(例如:通过微处理器112执行程序代码112C的存储器控制器110)对闪存模块120进行写入数据的运作是以数据页为单位来进行写入。在本实施例中,闪存模块120为一立体NAND型闪存(3D NAND-type flash)。

实作上,通过微处理器112执行程序代码112C的闪存控制器110可利用其本身内部的组件来进行诸多控制运作,例如:利用控制逻辑114来控制闪存模块120的存取运作(尤其是对至少一区块或至少一数据页的存取运作)、利用缓冲存储器116进行所需的缓冲处理、以及利用界面逻辑118来与一主装置(Host Device)130沟通。缓冲存储器116可以是静态随机存取存储器(Static RAM,SRAM),但本发明不限于此。

在一实施例中,记忆装置100可以是可携式记忆装置(例如:符合SD/MMC、CF、MS、XD标准的记忆卡),且主装置130为一可与记忆装置连接的电子装置,例如手机、笔记本电脑、桌面计算机…等等。而在另一实施例中,记忆装置100可以是固态硬盘或符合通用闪存存储(Universal Flash Storage,UFS)或嵌入式多媒体记忆卡(Embedded Multi Media Card,EMMC)规格的嵌入式存储装置,以设置在一电子装置中,例如设置在手机、笔记本电脑、桌面计算机的中,而此时主装置130可以是所述电子装置的一处理器。

在本实施例中,闪存模块120是一立体NAND型闪存(3D NAND-type flash)模块,请参考图2,其为一立体NAND型闪存的范例示意图。如图2所示,立体NAND型闪存包括了多个浮闸晶体管202,其通过多条位线(图示仅绘示了BL1~BL3)及多条字线(例如图示的WL0~WL2、WL4~WL6)来构成立体NAND型闪存架构。在图2中,以最上面的一个平面为例,字线WL0上的所有浮闸晶体管构成了至少一数据页,字线WL1上的所有浮闸晶体管构成了另至少一数据页,而字线WL2的所有浮闸晶体管构成了另外至少一数据页…以此类堆。此外,根据闪存写入方式的不同,字线WL0与数据页(逻辑数据页)之间的定义也会有所不同,详细来说,当使用单层式存储(Single-Level Cell,SLC)的方式写入时,字线WL0上的所有浮闸晶体管仅对应到单一逻辑数据页;当使用多层式存储(Multi-Level Cell,MLC)的方式写入时,字线WL0上的所有浮闸晶体管对应到两个、三个或是四个逻辑数据页,其中字线WL0上的所有浮闸晶体管对应到三个逻辑数据页的情形可以称为三层式存储(Triple-Level Cell,TLC)架构,而字线WL0上的所有浮闸晶体管对应到四个逻辑数据页的情形可以称为四层式存储(Quad-Level Cell,QLC)架构。由于本技术领域中具有通常知识者应能了解立体NAND型闪存的结构以及字线及数据页之间的关系,故相关的细节在此不予赘述。另外,在闪存控制器110的操作中,“数据页”为一最小写入单位,且“区块”为一最小抹除单位。

在一实施例中,每一个浮闸晶体管的栅极及浮闸是围绕在源极与漏极周围(gateall around),以增强通道感应能力。

需注意的是,图2所示的仅为立体NAND型闪存与浮闸晶体管202的范例,而并非是作为本发明的限制,本技术领域中具有通常知识者应能了解立体NAND型闪存尚有其他种型式,例如部分的字线可彼此连接..等等。

如现有技术中所述,立体NAND型闪存模块中的位线BL1~BL3具有较大宽高比,因此其蚀刻制程并无法使得位线的每一个区段都具有相同的宽度,因此容易造成位线BL1~BL3与字线WL0~WL2、WL4~WL6之间的短路,或是其他的短路/断路问题,上述短路问题可能会使得某些浮闸晶体管202上所存储的位出现高可靠度错误(High Reliability Error,HRE),也就是当读取所述浮闸晶体管202上的信息并进行软解码的过程中,会出现某些具有较高可靠度的错误位,而这些具有较高可靠度的错误位会严重影响到解码操作,并有可能造成解码失败。特别地,上述短路问题会随着写入抹除次数(program/erase cycle,P/Ecycle)的增加而变的严重,也就是当写入抹除次数增加,出现高可靠度错误的浮闸晶体管202的数量也会增加,因而成解码上的困扰。因此,本实施例中的解码器134是设计用来在解码过程中记录具有高可靠度错误的浮闸晶体管202的实体地址,以作为解码时的辅助来增加解码成功的机率。

图3所示为本发明一实施例的解码器134的示意图。如图3所示,解码器134包括了一数字处理电路310、一低密度奇偶检查码(Low-density parity-check code,LDPC)解码电路320、一高可靠度错误判断电路330以及一存储单元340,其中存储单元340包括了一表格342。在解码器134的操作中,首先,解码器134自闪存模块120中读取一第一数据,其中所述第一数据可以是闪存模块120中一区块内的一数据页的一个区段(sector)或是组块(chunk)。在本实施例中,所述第一数据是通过使用至少两个不同的感测电压来对闪存模块120中的浮闸晶体管202进行存取所得到,且所述第一数据包括了多个位的软信息D_soft,而每一个位的软信息D_soft包括了一初始位值(或可称为标记位(sign bit))以及至少两个软位(soft bit),其中每一个位的信息中的所述初始位值是“0”或是“1”,而每一个位的信息中的所述至少两个软位是用来表示/计算所述初始位值的可靠度,举例来说,假设所述初始位值为“1”且两个软位为(1,1),则表示所述初始位值“1”具有很高的可靠度(或可以称作很高的机率);假设所述初始位值为“1”且两个软位为(1,0),则表示所述初始位值“1”具有较高的可靠度;假设所述初始位值为“1”且两个软位为(0,1),则表示所述初始位值“1”具有较低的可靠度;而假设所述初始位值为“1”且两个软位为(0,0),则表示所述初始位值“1”具有最低的可靠度。在另一例子中,假设所述初始位值为“0”且两个软位为(1,1),则表示所述初始位值“1”具有很低的可靠度(或可以称作很高的机率);假设所述初始位值为“0”且两个软位为(1,0)或是(0,1),则表示所述初始位值“0”具有中等的可靠度;而假设所述初始位值为“0”且两个软位为(0,0),则表示所述初始位值“0”具有最高的可靠度。

需注意的是,上述使用两个软位来判断可靠度的方式仅为一范例说明,而并非是作为本发明的限制。在本发明的其他实施例中,两个软位可以在闪存模块120便已经根据一映像表或是其他计算方式而转换为不同的可靠度表现方式,及/或可靠度的判断可以同时根据初始位值以及软位的位值来判断。

接着,LDPC解码电路320对软信息D_soft进行解码,以产生所述第一数据的多个最终位值D_hard。

由于上述有关于软信息D_soft或是LDPC解码电路320的细节操作并非本发明的重点,且相关的细节可以参考中国台湾地区专利申请案:申请号100102086,或是其他的相关文献,故数字处理电路310以及LDPC解码电路320的细节在此不予赘述。

接着,高可靠度错误判断电路330逐位地比对所述第一数据的软信息D_soft以及最终位值D_hard,以判断出所述第一数据中哪些位具有高可靠度但是其位值是错误的,并将这些具有高可靠度但是其位值是错误的位所对应的实体地址记录在表格342中。以图4为例来进行说明,图4绘示了解码器134依序处理自八个浮闸晶体管202_1~202_8所读取的数据的示意图。在图4中,首先解码器134读取浮闸晶体管202_1,假设其所产生的软信息D_soft中的初始位值为“1”且两个软位为(1,1),而LDPC解码电路320输出的最终位值D_hard则是“0”,因此,由于初始位值不同于最终位值(也就是说,初始位值是错误的),再加上两个软位(1,1)代表着高可靠度,故浮闸晶体管202_1是被判断为对应至具有高可靠度错误的位(也就是说,浮闸晶体管202_1所记录的信息在被读出之后是具有高可靠度的错误位),且浮闸晶体管202_1的实体地址会被记录在表格342中。接着,解码器134读取浮闸晶体管202_2,假设其所产生的软信息D_soft中的初始位值为“1”且两个软位为(1,0),而LDPC解码电路320输出的最终位值D_hard则是“1”,因此,由于初始位值相同于最终位值(也就是说,初始位值是正确的),故浮闸晶体管202_2是被判断为并非对应至具有高可靠度错误的位,且浮闸晶体管202_2的实体地址不会被记录在表格342中。接着,解码器134读取浮闸晶体管202_3,假设其所产生的软信息D_soft中的初始位值为“1”且两个软位为(0,1),而LDPC解码电路320输出的最终位值D_hard则是“1”,因此,由于初始位值相同于最终位值(也就是说,初始位值是正确的),故浮闸晶体管202_3是被判断为并非对应至具有高可靠度错误的位,且浮闸晶体管202_3的实体地址不会被记录在表格342中。接着,解码器134读取浮闸晶体管202_4,假设其所产生的软信息D_soft中的初始位值为“1”且两个软位为(0,0),而LDPC解码电路320输出的最终位值D_hard则是“1”,虽然初始位值不同于最终位值(也就是说,初始位值是错误的),但由于两个软位(0,0)代表着低可靠度,故浮闸晶体管202_4是被判断为并非对应至具有高可靠度错误的位,且浮闸晶体管202_4的实体地址不会被记录在表格342中。接着,解码器134读取浮闸晶体管202_5,假设其所产生的软信息D_soft中的初始位值为“0”且两个软位为(0,0),而LDPC解码电路320输出的最终位值D_hard则是“0”,因此,由于初始位值相同于最终位值(也就是说,初始位值是正确的),故浮闸晶体管202_5是被判断为并非对应至具有高可靠度错误的位,且浮闸晶体管202_5的实体地址不会被记录在表格342中。接着,解码器134读取浮闸晶体管202_6,假设其所产生的软信息D_soft中的初始位值为“0”且两个软位为(0,1),而LDPC解码电路320输出的最终位值D_hard则是“0”,因此,由于初始位值相同于最终位值(也就是说,初始位值是正确的),故浮闸晶体管202_6是被判断为并非对应至具有高可靠度错误的位,且浮闸晶体管202_6的实体地址不会被记录在表格342中。接着,解码器134读取浮闸晶体管202_7,假设其所产生的软信息D_soft中的初始位值为“0”且两个软位为(1,0),而LDPC解码电路320输出的最终位值D_hard则是“1”,虽然初始位值不同于最终位值(也就是说,初始位值是错误的),但由于两个软位(1,0)代表着中等可靠度而非高可靠度,故浮闸晶体管202_7是被判断为并非对应至具有高可靠度错误的位,且浮闸晶体管202_7的实体地址不会被记录在表格342中。最后,解码器134读取浮闸晶体管202_8,假设其所产生的软信息D_soft中的初始位值为“0”且两个软位为(1,1),而LDPC解码电路320输出的最终位值D_hard则是“0”,因此,由于初始位值相同于最终位值(也就是说,初始位值是正确的),故浮闸晶体管202_8是被判断为并非对应至具有高可靠度错误的位,且浮闸晶体管202_8的实体地址不会被记录在表格342中。

图5为本发明一实施例的表格342的示意图。如图5所示,表格342所记录的发生过高可靠度错误的浮闸晶体管202的区块编号、数据页编号、组块编号以及地址信息。此外,表格342也会记录浮闸晶体管202在解码过程中发生过高可靠度错误的次数。

在一实施例中,图3所示的解码器134可以另外包括一缓存器,以暂存高可靠度错误判断电路330所产生的具有高可靠度错误的位的浮闸晶体管202的地址,并等待所暂存的地址数量到达一临界值(例如,10笔地址)之后,再一并写入到表格342中。

另外,由于存储单元342的空间有限,故表格342在写入的过程中可以使用一最近最少使用(Least recently used,LRU)算法,也就是将一段时间没有发生高可靠度错误位的浮闸晶体管202的地址自表格342中移除。

图6为本发明一实施例的解码方法的流程图,其流程步骤如下所述:

步骤600:流程开始。

步骤602:闪存控制器110自闪存模块120中读取一数据。

步骤604:解码器134对所述数据进行解码,其中当解码成功时(也就是说,LDPC解码电路320可以产生最终位值),流程进入步骤606;而若是解码失败时,流程进入步骤608。

步骤606:解码器134输出解码后数据,且高可靠度错误判断电路判断出所述数据中哪些位具有高可靠度但是其位值却是错误的,并将这些具有高可靠度但是其位值错误的位所对应的实体地址记录在表格342中。

步骤608:判断所述数据所对应到的闪存模块120中的地址是否有一部分被记录在表格342中,若是,流程进入步骤612;若否,流程进入步骤610。

步骤610:采用其他解码方式,例如采用类似容错式磁盘阵列(Redundant Arrayof Independent Disks,RAID)的错误更正方式、或是磁盘救援的方法,来帮助解码进行。

步骤612:将所述数据中对应具有高可靠度错误地址的多个位的至少一部分位进行修改以产生一修改后数据。

步骤614:对所述修改后数据进行解码。

在步骤612中,解码器134可以先将一个位进行修改后进行解码,其中所述位对应到高可靠度错误发生次数最多的浮闸晶体管,之后若是解码再次失败的话则在修改其他的位。举例来说,假设所述数据中的第1、5、6、8个位所对应到的浮闸晶体管202有被记录在表格342中,且第5个位所对应的浮闸晶体管202具有最多高可靠度错误的发生次数,因此当所述数据解码失败时,解码器134可以先将第5个位的初始位值翻转(例如“0”改为“1”,或是“1”改为“0”)以产生修改后数据进行解码。若是解码仍然失败,则再将第1、6、8个位的初始位值翻转以产生修改后数据后再次进行解码。

需注意的是,上一段落所述的仅是作为范例说明,而并非是本发明的限制。在其他的实施例中,解码器134也可以一开始就将第1、5、6、8个位的初始位值翻转以产生修改后数据后进行解码。只要位翻转的选择是基于表格342中所记录的有发生高可靠度错误的地址,相关设计上的变化应隶属于本发明的范畴。

在一实施例中,表格342中所记录的信息也可用来判断区块中时常发生高可靠度错误的浮闸晶体管202的数量是否过多,并据以判断是否要据此抹除并不再使用此区块。具体来说,当表格342的内容指出一特定区块内对应到高可靠度错误的地址高于一临界值时,为了避免后续所述特定区块内对应到高可靠度错误的地址持据增加而导致数据完全无法成功解码的问题,微处理器112可以先将所述特定区块内的有效数据搬移至其他区块中(也就是说,垃圾收集(garbage collection)操作),之后再将所述特定区块标记为无效,并设定闪存控制器110后续不会再将数据写入至所述特定区块中。

简要归纳本发明,在本发明的解码方法中,是在解码过程中不断在一表格中记录发生高可靠度错误的位所对应到的实体地址,且所述表格的内容可以供后续解码失败时使用。由于会发生高可靠度错误的浮闸晶体管持续发生错误的机率很高,因此会严重影响解码的成功与否,因此,通过本发明可以在解码过程中降低这些会发生高可靠度错误的浮闸晶体管的影响,以提升解码成功的机率。

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 解码方法及相关的闪存控制器与电子装置

- 解码方法及相关的闪存控制器与电子装置