音频同步处理电路及其方法

文献发布时间:2023-06-19 11:52:33

技术领域

本发明是属于音频同步技术,特别是一种可通过调整时钟单元来与主机端之间达到同步,从而改善音频品质的音频同步处理电路及其方法。

背景技术

随着3C产业的快速成长,各装置相互间传递数据用的传输接口也不断地在演进。目前,以通用序列汇流排(Universal Serial Bus,USB)的技术最为成熟并且普及。因此,通用序列汇流排于近年来已成为主要的传输接口之一。

在通用序列汇流排的规格中,包含了控制传输型式(control transfer type)、中断传输型式(interrupt transfer type)、大量传输型式(bulk transfer type)以及等时传输型式(isochronous transfer type)共四种传输型式。对于需要保证即时性与连续性的音频数据而言,通常会使用到等时传输型式来将音频数据例如从主机端传送至装置端。

然而,在音频数据传输过程中,常因主机端的时钟与装置端的时钟的不同步而造成音频品质不佳等问题出现,例如出现杂音、音频数据毁损、播放停顿等。

发明内容

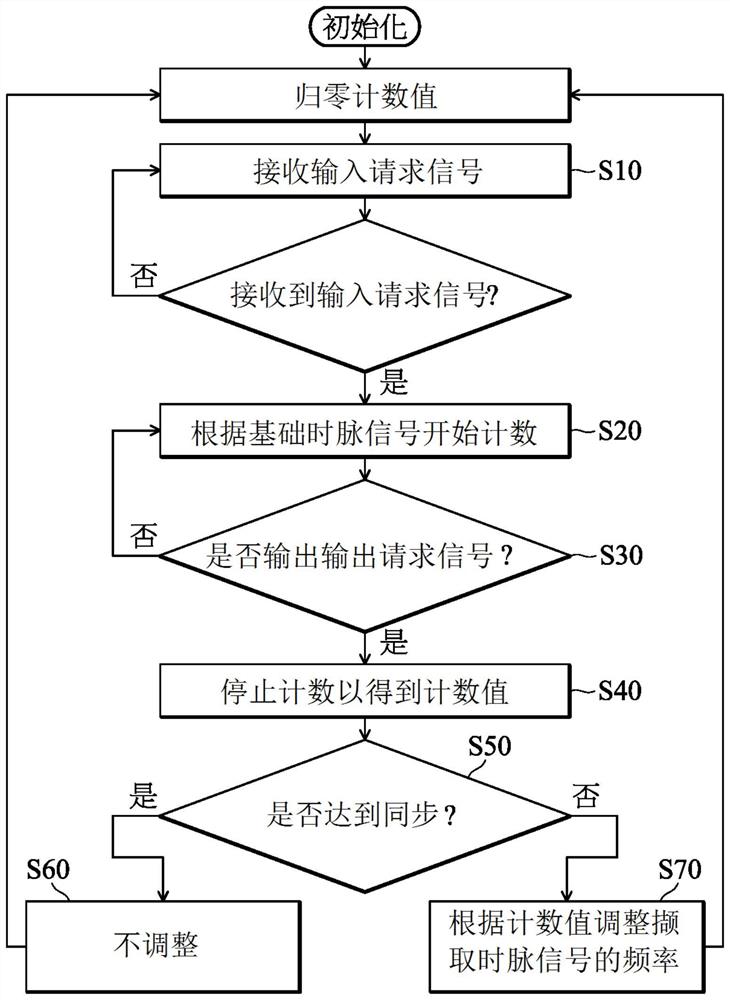

本发明的一实施例揭露一种音频同步处理方法。音频同步处理方法包含:接收输入请求信号;于接收到输入请求信号时,根据基础时脉信号开始计数;根据撷取时脉信号输出输出请求信号;于输出输出请求信号时,停止计数以得到计数值;根据计数值判断是否达到同步;及于判定未到达同步时,根据计数值调整撷取时脉信号的频率。

本发明的一实施例揭露一种音频同步处理电路。音频同步处理电路包含第一传输接口、第二传输接口以及处理模块。处理模块用以经由第一传输接口接收输入请求信号,并于接收到输入请求信号时根据基础时脉信号开始计数。处理模块更用以根据撷取时脉信号经由第二传输接口输出输出请求信号,并且于输出输出请求信号时停止计数以得到计数值。并且,处理模块更用以根据计数值判断是否达到同步。其中,于判定未达到同步时,处理模块根据计数值调整撷取时脉信号的频率。

附图说明

图1为应用本发明一实施例的音频同步处理电路的系统的方块示意图。

图2为本发明一实施例的音频同步处理方法的流程示意图。

图3为本发明一实施例的计数单元的相关信号的波形示意图。

符号说明:

100 音频同步处理电路

110 第一传输接口

120 第二传输接口

130 处理模块

131 计数单元

132 时钟单元

133 处理单元

134 控制单元

140 缓冲存储器

200 主机端

300 音频编解码单元

400 音频输出单元

A1 调整信号

C1 计数值

CK1 撷取时脉信号

CK2 基础时脉信号

D1 输入音频数据

D2 缓冲音频数据

R1 输入请求信号

R1’ 输入回复信号

R2 输出请求信号

R2’ 输出回复信号

S10~S70 步骤

具体实施方式

为使本发明的实施例的上述目的、特征和优点能更明显易懂,下文配合所附图式,作详细说明如下。

必须了解的是,使用于本说明书中的「包含」、「包括」等词,是用以表示存在特定的技术特征、数值、方法步骤、作业处理、元件以及/或组件,但并不排除可加上更多的技术特征、数值、方法步骤、作业处理、元件、组件,或以上的任意组合。

「第一」、「第二」等词是用来修饰元件,并非用来表示之间优先顺序或先行关系,而仅用来区别具有相同名字的元件。

图1为应用本发明一实施例的音频同步处理电路的系统的方块示意图。请参阅图1,音频同步处理电路100耦接于主机端200与音频编解码单元300之间。在一些实施例中,音频同步处理电路100可透过但不限定于汇流排来和主机端200及音频编解码单元300连接。在一些实施例中,汇流排可例如但不限定于先进高速汇流排(Advanced High performanceBus,AHB)。

主机端200可根据一发送频率(例如,每隔一固定时间1毫秒、125微秒等)依序发送输入音频数据D1至音频同步处理电路100,并且音频同步处理电路100可依据撷取时脉信号CK1的频率依序输出缓冲音频数据D2至音频编解码单元300,以交由音频编解码单元300进行特定处理后,再进一步透过后级的音频输出单元400播放出相应的音频。

在一些实施例中,音频编解码单元300的特定处理可包含将缓冲音频数据D2从数位形式的电子信号转换至类比形式的电子信号,但本发明并非以此为限。在一些实施例中,音频输出单元400可为但不限于扬声器。

音频同步处理电路100可包含至少二传输接口(以下分别称的为第一传输接口110与第二传输接口120)以及处理模块130。其中,处理模块130耦接于第一传输接口110与第二传输接口120。此外,处理模块130可根据本发明任一实施例的音频同步处理方法来调整撷取时脉信号CK1的频率,以使得音频同步处理电路100的输出频率(即,撷取时脉信号CK1的频率)可同步于主机端200的发送频率,从而改善音频因不同步所出现的品质问题,例如降低杂音、毁损、播放停顿等现象出现。

值得注意的是,为了清楚阐述本发明,图1为一简化的方块图,其中仅显示出与本发明相关的元件。本领域内技术人员应了解系统亦可能包含其他元件,用以提供特定的功能。

图2为本发明一实施例的音频同步处理方法的流程示意图。请参阅图1与图2,在音频同步处理方法的一实施例中,音频同步处理电路100的处理模块130可经由第一传输接口110接收到主机端200根据其发送频率所传送的输入请求信号R1(步骤S10)。于接收到输入请求信号R1时,处理模块130便可根据基础时脉信号CK2开始计数(步骤S20)。接续,处理模块130可根据撷取时脉信号CK1经由第二传输接口120输出输出请求信号R2(步骤S30),并且于输出请求信号R2输出时,处理模块130便可停止计数,以得到输入请求信号R1和输出请求信号R2之间的计数值C1(步骤S40)。之后,处理模块130可根据所得的计数值C1去判断主机端200的发送频率是否与撷取时脉信号CK1的频率达到同步(步骤S50)。

当处理模块130于步骤S50中判定达到同步时,处理模块130可不调整撷取时脉信号CK1的频率(步骤S60)。此外,于步骤S60之后,处理模块130可更返回步骤S10,以重启音频同步处理流程。

而当处理模块130于步骤S50中判定未达到同步时,处理模块130便可根据计数值C1去调整撷取时脉信号CK1的频率(步骤S70)。此外,于步骤S70之后,处理模块130可更返回步骤S10,以通过重复执行音频同步处理方法,使得取时脉信号CK1的频率可逐步趋于和主机端200的发送频率同步,进而可改善音频品质问题。

在一些实施例中,如图1所示,处理模块130可包含计数单元131、时钟单元132、处理单元133以及控制单元134。计数单元131耦接于处理单元133,处理单元133耦接于时钟单元132,并且控制单元134耦接于计数单元131、时钟单元132、第一传输接口110以及第二传输接口120。

计数单元131受控于控制单元134。于此,计数单元131可于控制单元134的致使下根据基础时脉信号CK2开始计数,并且可于控制单元134的致使下停止计数以得到并输出计数值C1给处理单元133。

时钟单元132用以产生撷取时脉信号CK1,并且可受控于处理单元133。于此,时钟单元132可根据处理单元133的控制调整撷取时脉信号CK1的频率。

处理单元133用以根据计数单元131所输出的计数值C1判断是否达到同步。其中于判定未达到同步时,处理单元133可输出调整信号A1给时钟单元132,以致使时钟单元132根据调整信号A1对应地调整撷取时脉信号CK1的频率。

控制单元134用以经由第一传输接口110接收输入请求信号R1,并且于接收到输入请求信号R1时致能计数单元131开始计数。此外,控制单元134更用以根据撷取时脉信号CK1经由第二传输接口120输出输出请求信号R2,并且于输出输出请求信号R2时致使计数单元131停止计数。

在一些实施例中,音频同步处理电路100可更包含缓冲存储器140,且缓冲存储器140耦接于控制单元134。在一些实施例中,缓冲存储器140可利用但不限于随机存取存储器(RAM)来实现。此外,缓冲存储器140可为随机存取存储器中的暂存区(buffer)。

在步骤S10的一实施例中,处理模块130的控制单元134于经由第一传输接口110接收到输入请求信号R1之后,控制单元134更可经由第一传输接口110回传输入回复信号R1’给主机端200,以通知主机端200可输出输入音频数据D1。此外,控制单元134于经由第一传输接口110接收到主机端200所传送的输入音频数据D1后,控制单元134可将输入音频数据D1储存至缓冲存储器140中,以进行缓冲。

在一些实施例中,控制单元134中可包含先进先出(FIFO)存储器(图未示)。因此,输入音频数据D1可通过控制单元134的先进先出存储器后再储存至缓冲存储器140中。

在步骤S20的一实施例中,控制单元134于收到输入请求信号R1时可转传输入请求信号R1至计数单元131的计数端,以致使计数单元131可开始根据其时脉端所输入的基础时脉信号CK2开始计数。

在步骤S30的一实施例中,控制单元134可根据撷取时脉信号CK1经由第二传输接口120输出输出请求信号R2给音频编解码单元300,以请求输出缓冲音频数据D2至编解码单元300。此外,编解码单元300于接收到输出请求信号R2时可回传输出回复信号R2’给控制单元134,以通知控制单元134可输出缓冲音频数据D2。在一些实施例中,控制单元134于输出输出请求信号R2并且接收到输出回复信号R2’的后,控制单元134便可从缓冲存储器140中取出缓冲音频数据D2,并经由第二传输接口120输出给编解码单元300。其中,缓冲音频数据D2为主机端200先前输出并储存至缓冲存储器140中的输入音频数据D1。但此并非限定,刚储存至缓冲存储器140中的输入音频数据D1会最先被控制单元134作为缓冲音频数据D2而取出。在一些实施例中,控制单元134每次取出时会以当前储存最久的输入音频数据D1(即根据各输入音频数据D1的输入顺序)作为缓冲音频数据D2而取出。

在一些实施例中,缓冲音频数据D2可通过控制单元134的先进先出存储器后再输出给编解码单元300。

在步骤S40的一实施例中,控制单元134可于经由第二传输接口120输出输出请求信号R2时,亦输出输出请求信号R2至计数单元131的停止端,以致使计数单元131停止计数,并且控制单元134可取得当前计数单元131所计算到的计数值C1。如图3所示的一例示波形图为例,此时计数单元131在输入请求信号R1与输出请求信号R2之间所计数到的计数值C1为5。

在步骤S50的一实施例中,当计数值C1不为零时,处理单元133可判定未达到同步并接续执行步骤S70。

在步骤S70的一实施例中,处理单元133可将计数值C1和多个预设区间进行比较,以判断计数值C1是落于哪一个预设区间之中,并且处理单元133可根据计数值C1所落入的预设区间产生相应的调整信号A1给时钟单元132,以致使时钟单元132可根据调整信号A1相应地调整撷取时脉信号CK1的频率。

举例而言,假设共有三个预设区间。于此,第一预设区间为计数值C1小于第一值,第二预设区间为计数值C1大于第一值但小于第二值,且第三预设区间为计数值C1大于第二值。当处理单元133判定计数值C1落入第一预设区间时,处理单元133产生的调整信号A1可致使时钟单元132将撷取时脉信号CK1的频率调快一第一百分比,亦即撷取时脉信号CK1的基础频率加上其基础频率和第一百分比的乘积值。当处理单元133判定计数值C1落入第二预设区间时,处理单元133产生的调整信号A1可致使时钟单元132将撷取时脉信号CK1的频率调快一第二百分比,亦即撷取时脉信号CK1的基础频率加上其基础频率和第二百分比的乘积值。并且,当处理单元133判定计数值C1落入第三预设区间时,处理单元133产生的调整信号A1可致使时钟单元132将撷取时脉信号CK1的频率调快一第三百分比,亦即撷取时脉信号CK1的基础频率加上其基础频率和第三百分比的乘积值。其中,第三百分比大于第二百分比,且第二百分比大于第一百分比。

在一些实施例中,所述的第一值可为但不限于5,且第二值可为但不限于10。所述的撷取时脉信号CK1的基础频率可为但不限于20千赫兹(kHz)。所述的第一百分比可为但不限于1%。所述的第二百分比可为但不限于2%。此外,所述的第三百分比可为但不限于3%。

在一些实施例中,撷取时脉信号CK1的基础频率、多个预设区间以及各预设区间所对应的调整信号等皆可由使用者自行设定。举例而言,此些可编写于一设定档中,使得音频同步处理电路100于初始化时可根据设定档进行相关设定。

在一些实施例中,计数单元131于每次开始计数前可先归零,即将前次所得的计数值清除掉。在一些实施例中,计数单元131可利用同步计数器、非同步计数器等来实现。此外,计数单元131可透过硬体描述语言以数位电路合成方式制成,但本发明并非以此为限。

在一些实施例中,第一传输接口110与第二传输接口120分别可利用通用序列汇流排(Universal Serial Bus,USB)、序列周边接口(Serial Peripheral Interface,SPI)、通用非同步收发(Universal Asynchronous Receiver/Transmitter,UART)传输接口、无线网路传输接口、整合晶片传音(Integrated Interchip Sound,I2S)传输接口、脉冲编码调变(PCM)传输接口、脉冲密度调变(PDM)传输接口等来实现。此外,第一传输接口110所采用的传输标准可相同于或不同于第二传输接口120所采用的传输标准。

在一些实施例中,音频同步处理电路100可为包含于直接存储器存取(DirectMemory Access,DMA)控制器中的内部电路。其中,所述的控制单元134可为直接存储器存取控制器中的周边接口控制器,并且所述的输入请求信号R1、输出请求信号R2为一种直接存储器存取请求(DMA request)信号,但本发明并非以此为限。

特别的是,本案将撷取时脉信号CK1的频率的调整功能直接附加在直接存储器存取控制器之中时可减少所需的耗费成本。此外,使用直接存储器存取请求信号(即所述的输入请求信号R1和输出请求信号R2)来决定时序,更可使得调整的误差降到最低。

综上所述,本发明的实施例提供一种音频同步处理电路及其方法,其通过于输入请求信号和输出请求信号之间所得的计数值来判断是否达到同步,并于判定未达到同步时来根据计数值的大小去相应地调整撷取时脉信号的频率,以使得主机端和装置端可趋于同步,藉此改善音频品质不佳的问题。此外,本发明的音频同步处理电路及其方法的一实施例可以直接存储器存取控制器为基础后再附加上对撷取时脉信号的频率的调整功能即可实现,因此可减少所需的耗费成本。再者,本发明的音频同步处理电路及其方法的一实施例使用直接存储器存取请求信号来决定时序,而更可将调整的误差降到最低。

本发明的实施例揭露如上,然其并非用以限定本发明的范围,任何所属技术领域中具有通常知识者,在不脱离本发明实施例的精神和范围内,当可做些许的更动与润饰,因此本发明的保护范围当视前述的权利要求所界定者为准。

- 音频处理电路、音频处理装置和音频处理方法

- 用于同步音频数据处理的音频数据处理设备和方法