一种三维存储器失效分析样品制备方法

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及集成电路的失效分析技术领域,具体为一种三维存储器失效分析样品制备方法。

背景技术

三维存储器,通过在硅内部垂直制作电路的方法,大大提高了芯片单位面积的存储密度,是存储容量获得极大的提高。目前,三维存储技术已经发展到128层堆叠,而未来将向200层以上推进。三维矩阵式结构虽然可以提高芯片容量,但对分析技术提出了更高的要求,如说明书图1和图2分别给出了一个典型三维存储结构的结构图和平面图,三维存储结构由一系列基本存储单元矩阵构成,分别由Bit Line(B/L)和Word Line(W/L)控制,B/L和W/L分布在2个垂直截面上,一个基本存储单元的尺寸为100nm以下,一个垂直方向的存储单元形成一个通孔(Channel Hole),当其中一个存储单元发生故障时,需要在垂直方向实现纳米级精准的定位,而由于存储器的设计特点,图形重复性高,容易发生错误定位的情况,增加了分析难度。

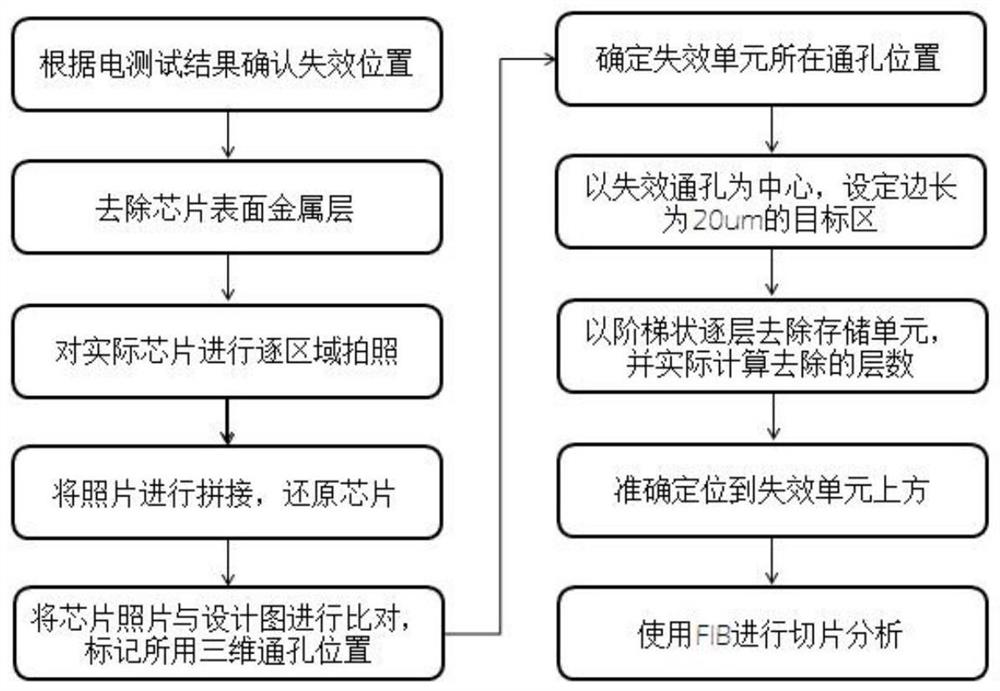

目前常用的三维存储器分析定位流程如图3所示,首先根据电测试结果在芯片设计Layout图纸上找到对应的B/L和W/L,并测量其到芯片边缘的距离,以测量点坐标(X,Y)为中心,选择100*100um的区域作为分析目标区,使用激光或者FIB(聚焦离子束)在芯片表面进行预处理,标记出分析目标区,然后去除该区域的Top Metal层,根据通孔(ChannelHole)查找W/L层数,最终定位到目标W/L上方1~2层W/L,最后使用FIB进行切片分析或平面取样。

现有方法的主要问题在于,分析目标区域定位完全由人工根据测量数据与理论图纸比对进行,由于封装完成的芯片与原始芯片存在差异,如切割偏差以及芯片翘曲变形,人工定位区域可能与实际失效位置存在一定偏差,为了弥补此偏差,需要比较大的分析目标区设定,但这样将导致在目标区内寻找通孔(Channel Hole)的难度增加,分析效率及准确度都受到影响。

发明内容

(一)解决的技术问题

针对现有技术的不足,本发明提供了一种三维存储器失效分析样品制备方法,解决了上述问题。

(二)技术方案

为实现上述目的,本发明提供如下技术方案:

一种三维存储器失效分析样品制备方法,包括以下步骤:

步骤一、对封装进行电测试,根据电测试结果确认失效位置,并记录下失效的log,使用封装开封技术去除待分析芯片上方的塑封料(EMC)及芯片;

步骤二、使用芯片表面delayer技术,去除待分析芯片表面的金属互连层,将通孔(Channel Hole)阵列全部暴露;

步骤三、将芯片置于聚焦离子束设备中,使用图像采集系统,对芯片整个区域,并按照固定放大倍率进行局部放大并按照设定步幅移动拍照,完成照片矩阵,生成照片序列;

步骤四、将步骤三拍摄的照片按照固定顺序传输到图像处理及合成系统中,通过系统合成,将以上照片按序列合成一张完整的实际芯片图;

步骤五、将上述实际芯片图与芯片设计图一同传输到图像校对及修正系统中,并使用图像识别技术对实际芯片照片与设计图进行比对修正,在实际芯片图上标注出发生失效的通孔的位置,并记录相对应的照片序号及在照片中的相对位置;

步骤六、将聚焦离子束样品台按照设定位移移动到步骤五中确认的照片序号及在照片中的对应位置,并找到失效通孔;

步骤七、使用离子束以确定的失效通孔为中心,设定边长为20um的目标区,以阶梯状逐层递减去除存储单元,通过单元高度及层数控制下挖深度,同时利用坑壁确认实际层数,最终精确定位到失效单元正上方;

步骤八、最后使用离子束切片技术提取切面分析。

优选的,所述芯片上的塑封料用发烟硝酸去除,加热温度185℃。

优选的,所述步骤一如存在多层芯片堆叠情况,可以使用化学开封或机械研磨开封或激光开封等方法。

优选的,步骤三所述放大倍率拍照时放大倍率一般固定为10000或者20000倍。

(三)有益效果

与现有技术相比,本发明提供了一种三维存储器失效分析样品制备方法,具备以下有益效果:

(1)本发明利用实时图像采集及拼接技术,将真实芯片与设计图纸进行比对,并进行位置修正,确定失效精确位置后,缩小目标区域,通过阶梯开口方式,精确掌握垂直层数,最终实现快速定位及分析。

(2)本发明通过对实际芯片的位置修正和定位,能够更准确及快速的实现失效位置确定,大大缩减了误判的发生率,并且由于定位准确,失效目标区域可以尽可能缩小,提高了分析操作效率。

附图说明

图1为背景技术中的典型三维存储结构的结构图;

图2为背景技术中的典型三维存储结构的平面图;

图3为现有技术常用的三维存储器分析定位流程图;

图4为本发明的流程图;

图5为本发明具体实施方式步骤三中芯片按照固定放大倍率的图片;

图6为本发明具体实施方式步骤四中还原拼接实际芯片过程图;

图7为本发明具体实施方式步骤五的示意图;

图8为本发明具体实施方式步骤七的示意图。

具体实施方式

下面将结合本发明的实施例,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

请参阅图4-8,一种三维存储器失效分析样品制备方法,包括以下步骤:

步骤一、对封装进行电测试,根据电测试结果确认失效位置,并记录下失效的log,使用封装开封技术去除待分析芯片上方的塑封料(EMC)及芯片;

步骤二、使用芯片表面delayer技术,去除待分析芯片表面的金属互连层,将通孔(Channel Hole)阵列全部暴露;

步骤三、将芯片置于聚焦离子束设备中,使用图像采集系统,对芯片整个区域,并按照固定放大倍率进行局部放大并按照设定步幅移动拍照,完成照片矩阵,生成照片序列,拍照时放大倍率拍照时放大倍率一般固定为10000或者20000倍,请参阅图5;

步骤四、将步骤三拍摄的照片按照固定顺序传输到图像处理及合成系统中,通过系统合成,将以上照片按序列合成一张完整的实际芯片图,请参阅图6;

步骤五、将上述实际芯片图与芯片设计图一同传输到图像校对及修正系统中,并使用图像识别技术对实际芯片照片与设计图进行比对修正,在实际芯片图上标注出发生失效的通孔的位置,并记录相对应的照片序号及在照片中的相对位置,请参阅图7;

步骤六、将聚焦离子束样品台按照设定位移移动到步骤五中确认的照片序号及在照片中的对应位置,并找到失效通孔;

步骤七、使用离子束以确定的失效通孔为中心,设定边长为20um的目标区,以阶梯状逐层递减去除存储单元(即开出20um见方的窗口,然后逐渐递减至10um及5um见方),通过单元高度及层数控制下挖深度,同时利用坑壁确认实际层数,最终精确定位到失效单元正上方,请参阅图8;

步骤八、最后使用离子束切片技术提取切面分析。

进一步的,芯片上的塑封料用发烟硝酸去除,加热温度185℃。

进一步的,步骤一如存在多层芯片堆叠情况,可以使用化学开封或机械研磨开封或激光开封等方法。

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

- 一种三维存储器失效分析样品制备方法

- 一种待失效分析样品的制备方法及待失效分析样品