数据存取方法、存储器控制电路单元以及存储器存储装置

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及一种存储器数据存取技术,尤其涉及一种数据存取方法、存储器控制电路单元以及存储器存储装置。

背景技术

数码相机、手机与MP3在这几年来的成长十分迅速,使得消费者对存储媒体的需求也急速增加。由于可复写式非易失性存储器(rewritable non-volatile memory module)(例如,快闪存储器)具有数据非易失性、省电、体积小、无机械结构、读写速度快等特性,最适于可携式电子产品,例如笔记型计算机。固态硬盘就是一种以快闪存储器作为存储媒体的存储器存储装置。因此,近年快闪存储器产业成为电子产业中相当热门的一环。

许多存储器控制器配置有错误检查与校正电路。此错误检查与校正电路用以对从可复写式非易失性存储器模块中读取出的数据进行错误检查与更正。然而,数据比特处于抹除状态的临界电压分布通常会异于处于其他程序化状态的临界电压分布,造成某些错误不容易被找到,使得解码失败的机率增加。

发明内容

本发明提供一种数据存取方法、存储器控制电路单元以及存储器存储装置,可提高解码效率。

本发明的范例实施例提供一种数据存取方法,用于可复写式非易失性存储器模块。所述可复写式非易失性存储器模块包括多个实体抹除单元,所述多个实体抹除单元的每一实体抹除单元具有多个实体程序化单元。所述数据存取方法包括:读取实体程序化单元存储的码字,并计算所述码字包括的虚拟数据中比特值发生变化的比特变化比例;根据所述比特变化比例调整读取电压电平或对数可能性比值;以及利用调整后的所述读取电压电平或调整后的所述对数可能性比值对所述码字进行解码操作。

在本发明的一范例实施例中,上述根据所述比特变化比例调整所述读取电压电平或所述对数可能性比值的步骤包括:根据所述比特变化比例决定补偿值,并根据所述补偿值调整所述读取电压电平。

在本发明的一范例实施例中,上述根据所述比特变化比例调整所述读取电压电平或所述对数可能性比值的步骤包括:根据所述比特变化比例决定补偿值,并根据所述补偿值调整所述对数可能性比值。

在本发明的一范例实施例中,上述虚拟数据为比特全为1的数据。

在本发明的一范例实施例中,上述比特变化比例包括所述虚拟数据中比特1变化为0的比例。

在本发明的一范例实施例中,上述解码操作包括硬比特模式解码操作。所述数据存取方法包括:利用调整后的所述读取电压电平读取所述实体程序化单元存储的所述码字,并对所述码字进行所述硬比特模式解码操作。

在本发明的一范例实施例中,上述解码操作包括软比特模式解码操作。所述数据存取方法包括:根据调整后的所述对数可能性比值对所述码字进行所述软比特模式解码操作。

本发明的范例实施例提供一种存储器控制电路单元,用于控制可复写式非易失性存储器模块。所述存储器控制电路单元包括主机接口、存储器接口、错误检查与校正电路以及存储器管理电路。所述主机接口用以耦接至主机系统。所述存储器接口用以耦接至所述可复写式非易失性存储器模块,其中所述可复写式非易失性存储器模块包括多个实体抹除单元,所述多个实体抹除单元的每一实体抹除单元具有多个实体程序化单元。所述存储器管理电路耦接至所述主机接口、所述存储器接口以及所述错误检查与校正电路。所述存储器管理电路用以读取实体程序化单元存储的码字,并计算所述码字包括的虚拟数据中比特值发生变化的比特变化比例。所述存储器管理电路更用以根据所述比特变化比例调整读取电压电平或对数可能性比值。并且,所述错误检查与校正电路更用以利用调整后的所述读取电压电平或调整后的所述对数可能性比值对所述码字进行解码操作。

在本发明的一范例实施例中,上述根据所述比特变化比例调整所述读取电压电平或所述对数可能性比值的操作包括:根据所述比特变化比例决定补偿值,并根据所述补偿值调整所述读取电压电平。

在本发明的一范例实施例中,上述根据所述比特变化比例调整所述读取电压电平或所述对数可能性比值的操作包括:根据所述比特变化比例决定补偿值,并根据所述补偿值调整所述对数可能性比值。

在本发明的一范例实施例中,上述虚拟数据为比特全为1的数据。

在本发明的一范例实施例中,上述比特变化比例包括所述虚拟数据中比特1变化为0的比例。

在本发明的一范例实施例中,上述解码操作包括硬比特模式解码操作。所述错误检查与校正电路更用以利用调整后的所述读取电压电平读取所述实体程序化单元存储的所述码字,并对所述码字进行所述硬比特模式解码操作。

在本发明的一范例实施例中,上述解码操作包括软比特模式解码操作,所述错误检查与校正电路更用以根据调整后的所述对数可能性比值对所述码字进行所述软比特模式解码操作。

本发明的范例实施例提供一种存储器存储装置,包括连接接口单元、可复写式非易失性存储器模块以及存储器控制电路单元。所述连接接口单元用以耦接至主机系统。所述可复写式非易失性存储器模块包括多个实体抹除单元,所述多个实体抹除单元的每一实体抹除单元具有多个实体程序化单元。所述存储器控制电路单元耦接至所述连接接口单元与所述可复写式非易失性存储器模块。所述存储器控制电路单元用以读取实体程序化单元存储的码字,并计算所述码字包括的虚拟数据中比特值发生变化的比特变化比例。所述存储器控制电路单元更用以根据所述比特变化比例调整读取电压电平或对数可能性比值。所述存储器控制电路单元更用以利用调整后的所述读取电压电平或调整后的所述对数可能性比值对所述码字进行解码操作。

在本发明的一范例实施例中,上述根据所述比特变化比例调整所述读取电压电平或所述对数可能性比值的操作包括:根据所述比特变化比例决定补偿值,并根据所述补偿值调整所述读取电压电平。

在本发明的一范例实施例中,上述根据所述比特变化比例调整所述读取电压电平或所述对数可能性比值的操作包括:根据所述比特变化比例决定补偿值,并根据所述补偿值调整所述对数可能性比值。

在本发明的一范例实施例中,上述虚拟数据为比特全为1的数据。

在本发明的一范例实施例中,上述比特变化比例包括所述虚拟数据中比特1变化为0的比例。

在本发明的一范例实施例中,上述解码操作包括硬比特模式解码操作,所述存储器控制电路单元更用以利用调整后的所述读取电压电平读取所述实体程序化单元存储的所述码字,并对所述码字进行所述硬比特模式解码操作。

在本发明的一范例实施例中,上述解码操作包括软比特模式解码操作,所述存储器控制电路单元更用以根据调整后的所述对数可能性比值对所述码字进行所述软比特模式解码操作。

基于上述,本发明实施例会根据虚拟数据的比特变化比例调整读取电压电平或对数可能性比值,并根据调整后的读取电压电平或对数可能性比值执行解码操作。据此,可提升解码效率,进而提升读取数据的效率与正确性。

附图说明

图1是根据一范例实施例所示出的主机系统、存储器存储装置及输入/输出(I/O)装置的示意图;

图2是根据另一范例实施例所示出的主机系统、存储器存储装置及输入/输出(I/O)装置的示意图;

图3是根据另一范例实施例所示出的主机系统与存储器存储装置的示意图;

图4是根据一范例实施例所示出的主机系统与存储器存储装置的概要方块图;

图5是根据一范例实施例所示出的存储器控制电路单元的概要方块图;

图6与图7是根据一范例实施例所示出的管理实体抹除单元的范例示意图;

图8是根据一范例实施例所示出的存储单元的临界电压分布的示意图;

图9是根据一范例实施例所示出的从存储单元中读取数据的示意图;

图10是根据另一范例实施例所示出的从存储单元中读取数据的示意图;

图11是根据一范例实施例所示出的存储单元的临界电压分布发生变化的示意图;

图12是根据一范例实施例所示出的硬比特模式解码操作的示意图;

图13是根据一范例实施例所示出的软比特模式解码操作的示意图;

图14A及图14B是根据一范例实施例所示出的将写入数据、对应于写入数据的虚拟数据写入至实体程序化单元的范例;

图15A至图15C是根据一范例实施例所示出的虚拟数据的范例;

图16是根据一范例实施例所示出的存储单元的临界电压分布发生变化的示意图;

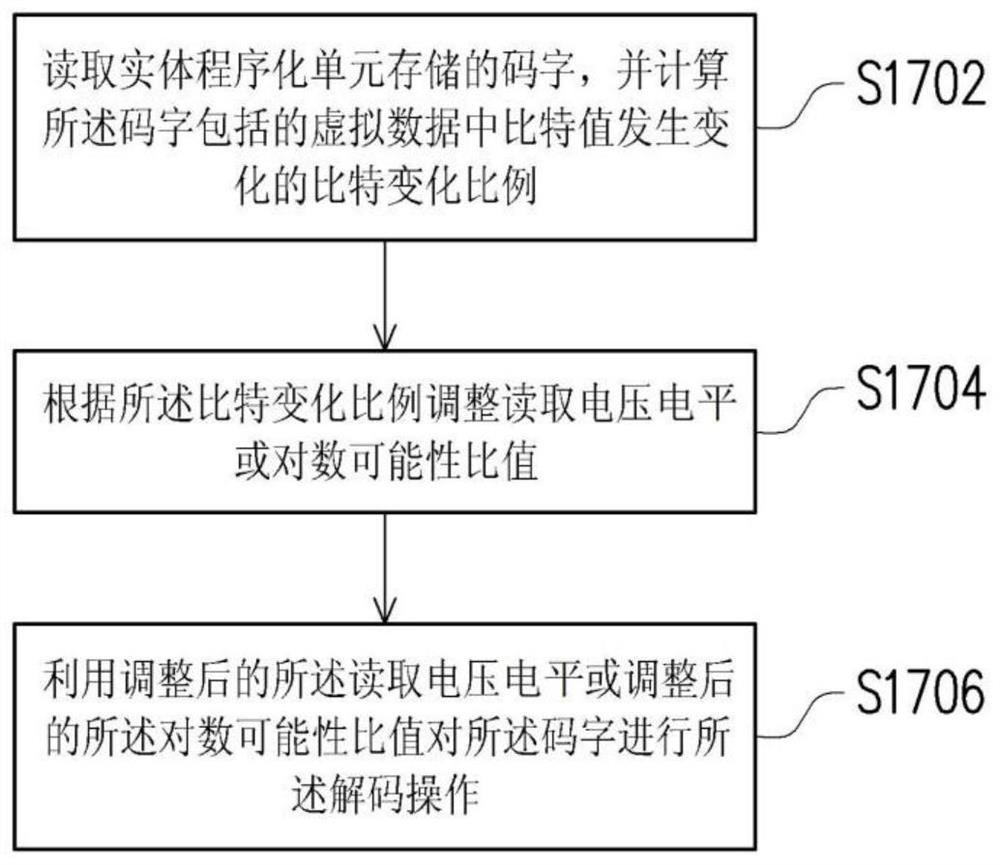

图17是根据一范例实施例所示出的数据存取方法的流程图。

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

一般而言,存储器存储装置(亦称,存储器存储系统)包括可复写式非易失性存储器模块与控制器(亦称,控制电路单元)。通常存储器存储装置是与主机系统一起使用,以使主机系统可将数据写入至存储器存储装置或从存储器存储装置中读取数据。

图1是根据一范例实施例所示出的主机系统、存储器存储装置及输入/输出(I/O)装置的示意图,并且图2是根据另一范例实施例所示出的主机系统、存储器存储装置及输入/输出(I/O)装置的示意图。

请参照图1与图2,主机系统11一般包括处理器111、随机存取存储器(randomaccess memory,RAM)112、只读存储器(read only memory,ROM)113及数据传输接口114。处理器111、随机存取存储器112、只读存储器113及数据传输接口114皆耦接至系统总线(system bus)110。

在本范例实施例中,主机系统11是通过数据传输接口114与存储器存储装置10耦接。例如,主机系统11可经由数据传输接口114将数据写入至存储器存储装置10或从存储器存储装置10中读取数据。此外,主机系统11是通过系统总线110与I/O装置12耦接。例如,主机系统11可经由系统总线110将输出信号传送至I/O装置12或从I/O装置12接收输入信号。

在本范例实施例中,处理器111、随机存取存储器112、只读存储器113及数据传输接口114是可设置在主机系统11的主机板20上。数据传输接口114的数目可以是一或多个。通过数据传输接口114,主机板20可以经由有线或无线方式耦接至存储器存储装置10。存储器存储装置10可例如是U盘201、存储卡202、固态硬盘(Solid State Drive,SSD)203或无线存储器存储装置204。无线存储器存储装置204可例如是近距离无线通信(Near FieldCommunication Storage,NFC)存储器存储装置、无线传真(WiFi)存储器存储装置、蓝牙(Bluetooth)存储器存储装置或低功耗蓝牙存储器存储装置(例如,iBeacon)等以各式无线通信技术为基础的存储器存储装置。此外,主机板20也可以通过系统总线110耦接至全球定位系统(Global Positioning System,GPS)模块205、网络接口卡206、无线传输装置207、键盘208、屏幕209、喇叭210等各式I/O装置。例如,在一范例实施例中,主机板20可通过无线传输装置207存取无线存储器存储装置204。

在一范例实施例中,所提及的主机系统为可实质地与存储器存储装置配合以存储数据的任意系统。虽然在上述范例实施例中,主机系统是以计算机系统来作说明,然而,图3是根据另一范例实施例所示出的主机系统与存储器存储装置的示意图。请参照图3,在另一范例实施例中,主机系统31也可以是数码相机、摄影机、通信装置、音频播放器、视频播放器或平板电脑等系统,而存储器存储装置30可为其所使用的SD卡32、CF卡33或嵌入式存储装置34等各式非易失性存储器存储装置。嵌入式存储装置34包括嵌入式多媒体卡(embeddedMMC,eMMC)341和/或嵌入式多芯片封装存储装置(embedded Multi Chip Package,eMCP)342等各类型将存储器模块直接耦接于主机系统的基板上的嵌入式存储装置。

图4是根据一范例实施例所示出的主机系统与存储器存储装置的概要方块图。

请参照图4,存储器存储装置10包括连接接口单元402、存储器控制电路单元404与可复写式非易失性存储器模块406。

在本范例实施例中,连接接口单元402是相容于串行高级附件(Serial AdvancedTechnology Attachment,SATA)标准。然而,必须了解的是,本发明不限于此,连接接口单元402亦可以是符合并行高级附件(Parallel Advanced Technology Attachment,PATA)标准、电气和电子工程师协会(Institute of Electrical and Electronic Engineers,IEEE)1394标准、高速周边零件连接接口(Peripheral Component Interconnect Express,PCI Express)标准、通用串行总线(Universal Serial Bus,USB)标准、超高速一代(UltraHigh Speed-I,UHS-I)接口标准、超高速二代(Ultra High Speed-II,UHS-II)接口标准、安全数字(Secure Digital,SD)接口标准、存储棒(Memory Stick,MS)接口标准、多芯片封装(Multi-Chip Package)接口标准、多媒体存储卡(Multi Media Card,MMC)接口标准、嵌入式多媒体存储卡(Embedded Multimedia Card,eMMC)接口标准、通用快闪存储器(Universal Flash Storage,UFS)接口标准、嵌入式多芯片封装(embedded Multi ChipPackage,eMCP)接口标准、小型快闪(Compact Flash,CF)接口标准、整合式驱动电子接口(Integrated Device Electronics,IDE)标准或其他适合的标准。在本范例实施例中,连接接口单元402可与存储器控制电路单元404封装在一个芯片中,或者连接接口单元402是布设于一包含存储器控制电路单元的芯片外。

存储器控制电路单元404用以执行以硬件型式或固件型式实作的多个逻辑门或控制指令,并且根据主机系统11的指令在可复写式非易失性存储器模块406中进行数据的写入、读取与抹除等运作。

可复写式非易失性存储器模块406是耦接至存储器控制电路单元404,并且用以存储主机系统11所写入的数据。可复写式非易失性存储器模块406具有实体抹除单元410(0)~410(N)。例如,实体抹除单元410(0)~410(N)可属于同一个存储器晶粒(die)或者属于不同的存储器晶粒。每一实体抹除单元分别具有多个实体程序化单元,其中属于同一个实体抹除单元的实体程序化单元可被独立地写入且被同时地抹除。然而,必须了解的是,本发明不限于此,每一实体抹除单元是可由64个实体程序化单元、256个实体程序化单元或其他任意个实体程序化单元所组成。

更详细来说,实体抹除单元为抹除的最小单位。亦即,每一实体抹除单元含有最小数目之一并被抹除的存储单元。实体程序化单元为程序化的最小单元。即,实体程序化单元为写入数据的最小单元。每一实体程序化单元通常包括数据比特区与冗余比特区。数据比特区包含多个实体存取地址用以存储使用者的数据,而冗余比特区用以存储系统的数据(例如,控制信息与错误更正码)。在本范例实施例中,每一个实体程序化单元的数据比特区中会包含8个实体存取地址,且一个实体存取地址的大小为512字节(byte)。然而,在其他范例实施例中,数据比特区中也可包含数目更多或更少的实体存取地址,本发明并不限制实体存取地址的大小以及个数。例如,在一范例实施例中,实体抹除单元为实体区块,并且实体程序化单元为实体页面(physical page)或实体扇区,但本发明不以此为限。

在本范例实施例中,可复写式非易失性存储器模块406可以是单阶存储单元(Single Level Cell,SLC)NAND型快闪存储器模块(即,一个存储单元中可存储1个数据比特的快闪存储器模块)、多阶存储单元(Multi Level Cell,MLC)NAND型快闪存储器模块(即,一个存储单元中可存储2个数据比特的快闪存储器模块)、三阶存储单元(TripleLevel Cell,TLC)NAND型快闪存储器模块(即,一个存储单元中可存储3个数据比特的快闪存储器模块)、其他快闪存储器模块或其他具有相同特性的存储器模块。

图5是根据一范例实施例所示出的存储器控制电路单元的概要方块图。

请参照图5,存储器控制电路单元404包括存储器管理电路502、主机接口504、存储器接口506、缓冲存储器508、电源管理电路510与错误检查与校正电路512。

存储器管理电路502用以控制存储器控制电路单元404的整体运作。具体来说,存储器管理电路502具有多个控制指令,并且在存储器存储装置10运作时,此些控制指令会被执行以进行数据的写入、读取与抹除等运作。以下说明存储器管理电路502的操作时,等同于说明存储器控制电路单元404的操作。

在本范例实施例中,存储器管理电路502的控制指令是以固件型式来实作。例如,存储器管理电路502具有微处理器单元(未示出)与只读存储器(未示出),并且此些控制指令是被烧录至此只读存储器中。当存储器存储装置10运作时,此些控制指令会由微处理器单元来执行以进行数据的写入、读取与抹除等运作。

图6与图7是根据一范例实施例所示出的管理实体抹除单元的范例示意图。

必须了解的是,在此描述可复写式非易失性存储器模块406的实体抹除单元的运作时,以“提取”、“分组”、“划分”、“关联”等词来操作实体抹除单元是逻辑上的概念。也就是说,可复写式非易失性存储器模块的实体抹除单元的实际位置并未更动,而是逻辑上对可复写式非易失性存储器模块的实体抹除单元进行操作。

请参照图6,存储器管理电路502会将实体抹除单元410(0)~410(N)逻辑地分组为数据区602、闲置区604、系统区606与取代区608。

逻辑上属于数据区602与闲置区604的实体抹除单元是用以存储来自于主机系统11的数据。具体来说,数据区602的实体抹除单元是被视为已存储数据的实体抹除单元,而闲置区604的实体抹除单元是用以替换数据区602的实体抹除单元。也就是说,当从主机系统11接收到写入指令与欲写入的数据时,存储器管理电路502会使用从闲置区604中提取实体抹除单元来写入数据,以替换数据区602的实体抹除单元。

逻辑上属于系统区606的实体抹除单元是用以记录系统数据。例如,系统数据包括关于可复写式非易失性存储器模块的制造商与型号、可复写式非易失性存储器模块的实体抹除单元数、每一实体抹除单元的实体程序化单元数等。

逻辑上属于取代区608中的实体抹除单元是用于坏实体抹除单元取代程序,以取代损坏的实体抹除单元。具体来说,倘若取代区608中仍存有正常的实体抹除单元并且数据区602的实体抹除单元损坏时,存储器管理电路502会从取代区608中提取正常的实体抹除单元来更换损坏的实体抹除单元。

特别是,数据区602、闲置区604、系统区606与取代区608的实体抹除单元的数量会根据不同的存储器规格而有所不同。此外,必须了解的是,在存储器存储装置10的运作中,实体抹除单元关联至数据区602、闲置区604、系统区606与取代区608的分组关系会动态地变动。例如,当闲置区604中的实体抹除单元损坏而被取代区608的实体抹除单元取代时,则原本取代区608的实体抹除单元会被关联至闲置区604。

请参照图7,存储器管理电路502会配置逻辑区块地址LBA(0)~LBA(H)以映射数据区602的实体抹除单元,其中每一逻辑区块地址具有多个逻辑地址以映射对应的实体抹除单元的实体程序化单元。并且,当主机系统11欲写入数据至逻辑地址或更新存储于逻辑地址中的数据时,存储器管理电路502会从闲置区604中提取一个实体抹除单元作为作动实体抹除单元来写入数据,以轮替数据区602的实体抹除单元。并且,当此作为作动实体抹除单元的实体抹除单元被写满时,存储器管理电路502会再从闲置区604中提取空的实体抹除单元作为作动实体抹除单元,以继续写入对应来自于主机系统11的写入指令的更新数据。此外,当闲置区604中可用的实体抹除单元的数目小于预设值时,存储器管理电路502会执行垃圾搜集(garbage collection)操作(亦称为,有效数据合并操作)来整理数据区602中的有效数据,以将数据区602中无存储有效数据的实体抹除单元重新关联至闲置区604。

为了识别每个逻辑地址的数据被存储在哪个实体程序化单元,在本范例实施例中,存储器管理电路502会记录逻辑地址与实体程序化单元之间的映射关系。例如,在本范例实施例中,存储器管理电路502会在可复写式非易失性存储器模块406中存储逻辑至实体映射表来记录每一逻辑地址所映射的实体程序化单元。当欲存取数据时存储器管理电路502会将逻辑至实体映射表载入至缓冲存储器508来维护,并且依据逻辑至实体映射表来写入或读取数据。

值得一提的是,由于缓冲存储器508的容量有限无法存储记录所有逻辑地址的映射关系的映射表,因此,在本范例实施例中,存储器管理电路502会将逻辑区块地址LBA(0)~LBA(H)分组为多个逻辑区域LZ(0)~LZ(M),并且为每一逻辑区域配置一个逻辑至实体映射表。特别是,当存储器管理电路502欲更新某个逻辑区块地址的映射时,对应此逻辑区块地址所属的逻辑区域的逻辑至实体映射表会被载入至缓冲存储器508来被更新。具体来说,若对应此逻辑区块地址所属的逻辑区域的逻辑至实体映射表未被暂存在缓冲存储器508中(即,缓冲存储器508中所暂存的逻辑至实体映射表未记录欲更新的逻辑区块地址的映射时,存储器管理电路502会执行映射表交换操作(mapping table swapping operation)以将目前暂存在缓冲存储器508中逻辑至实体映射表回存至可复写式非易失性存储器模块406,并且将记录有欲更新的逻辑区块地址所映射的逻辑至实体映射表载入至缓冲存储器508中。

在本发明另一范例实施例中,存储器管理电路502的控制指令亦可以代码型式存储于可复写式非易失性存储器模块406的特定区域(例如,存储器模块中专用于存放系统数据的系统区)中。此外,存储器管理电路502具有微处理器单元(未示出)、只读存储器(未示出)及随机存取存储器(未示出)。特别是,此只读存储器具有驱动码,并且当存储器控制电路单元404被致能时,微处理器单元会先执行此驱动码段来将存储于可复写式非易失性存储器模块406中的控制指令载入至存储器管理电路502的随机存取存储器中。之后,微处理器单元会运转此些控制指令以进行数据的写入、读取与抹除等运作。

此外,在本发明另一范例实施例中,存储器管理电路502的控制指令亦可以一硬件型式来实作。例如,存储器管理电路502包括微控制器、存储单元管理电路、存储器写入电路、存储器读取电路、存储器抹除电路与数据处理电路。存储单元管理电路、存储器写入电路、存储器读取电路、存储器抹除电路与数据处理电路是耦接至微控制器。其中,存储单元管理电路用以管理可复写式非易失性存储器模块406的实体抹除单元;存储器写入电路用以对可复写式非易失性存储器模块406下达写入指令以将数据写入至可复写式非易失性存储器模块406中;存储器读取电路用以对可复写式非易失性存储器模块406下达读取指令以从可复写式非易失性存储器模块406中读取数据;存储器抹除电路用以对可复写式非易失性存储器模块406下达抹除指令以将数据从可复写式非易失性存储器模块406中抹除;而数据处理电路用以处理欲写入至可复写式非易失性存储器模块406的数据以及从可复写式非易失性存储器模块406中读取的数据。

请再参照图5,主机接口504是耦接至存储器管理电路502并且用以耦接至连接接口单元402,以接收与识别主机系统11所传送的指令与数据。也就是说,主机系统11所传送的指令与数据会通过主机接口504来传送至存储器管理电路502。在本范例实施例中,主机接口504是相容于SATA标准。然而,必须了解的是本发明不限于此,主机接口504亦可以是相容于PATA标准、IEEE 1394标准、PCI Express标准、USB标准、UHS-I接口标准、UHS-II接口标准、SD标准、MS标准、MMC标准、CF标准、IDE标准或其他适合的数据传输标准。

存储器接口506是耦接至存储器管理电路502并且用以存取可复写式非易失性存储器模块406。也就是说,欲写入至可复写式非易失性存储器模块406的数据会经由存储器接口506转换为可复写式非易失性存储器模块406所能接受的格式。

缓冲存储器508是耦接至存储器管理电路502并且用以暂存来自于主机系统11的暂存数据与指令或来自于可复写式非易失性存储器模块406的数据。

电源管理电路510是耦接至存储器管理电路502并且用以控制存储器存储装置10的电源。

错误检查与校正电路512是耦接至存储器管理电路502并且用以执行错误检查与校正程序以确保数据的正确性。例如,当存储器管理电路502从主机系统11中接收到写入指令时,错误检查与校正电路512会为对应此写入指令的数据产生对应的错误检查与校正码(Error Checking and Correcting Code,ECC Code),并且存储器管理电路502会将对应此写入指令的数据与对应的错误检查与校正码写入至可复写式非易失性存储器模块406中。之后,当存储器管理电路502从可复写式非易失性存储器模块406中读取数据时会同时读取此数据对应的错误检查与校正码,并且错误检查与校正电路512会根据此错误检查与校正码对所读取的数据执行错误检查与校正程序。

图8是根据一范例实施例所示出的存储单元的临界电压分布的示意图。图9是根据一范例实施例所示出的从存储单元中读取数据的示意图。请参照图8与图9,以MLC NAND型快闪存储器为例,基于不同的临界电压,每一存储单元具有4种存储状态,并且此些存储状态分别地代表“11”、“10”、“01”与“00”等比特。换言之,每一个存储状态包括LSB以及MSB。在本范例实施例中,每一个存储状态中从左侧算起的第1个比特为LSB,而从左侧算起的第2个比特为MSB。因此,在此范例实施例中,每一存储单元可存储2个比特。必须了解的是,图8所示出的临界电压及其存储状态的对应仅为一个范例。在另一范例实施例中,临界电压与存储状态的对应亦可是随着临界电压越大而以“11”、“10”、“00”与“01”排列,或是其他排列。此外,在另一范例实施例中,亦可定义从左侧算起的第1个比特为MSB,而从左侧算起的第2个比特为LSB。

存储单元的读取运作是通过施予读取电压于控制门极,通过存储单元通道的导通状态,来识别存储单元存储的数据。以MLC NAND型快闪存储器为例,验证比特(VA)是用以指示施予读取电压VA时存储单元通道是否为导通;验证比特(VB)是用以指示施予读取电压VB时,存储单元通道是否为导通;验证比特(VC)是用以指示施予读取电压VC时,存储单元通道是否为导通。在此假设验证比特是“1”时表示对应的存储单元通道导通,而验证比特是“0”时表示对应的存储单元通道没有导通。如图9所示,通过验证比特(VA)~(VC)可以判断存储单元是处于哪一个存储状态,进而取得所存储的比特。

图10是根据另一范例实施例所示出的从存储单元中读取数据的示意图。请参照图10,以TLC NAND型快闪存储器为例,每一个存储状态代表一个存储单元所存储的3个比特。例如,在本范例实施例中,每一个存储状态包括从左侧算起的第1个比特的LSB、从左侧算起的第2个比特的中间有效比特(Center Significant Bit,CSB)以及从左侧算起的第3个比特的MSB。在此范例实施例中,依照不同的临界电压,存储单元具有8种存储状态(即,“111”、“110”、“101”、“100”、“011”、“010”、“001”与“000”)。通过施加读取电压VA~VG于控制门极,可以识别存储单元所存储的比特。其中,值得说明的是,此8种存储状态的排列顺序,可依制造商的设计而订,本发明不加以限制。此外,在另一范例实施例中,一个存储单元所存储的3个比特中的某一个比特为LSB、CSB或MSB,可视实务上需求调整。

须注意的是,为了说明方便,在以下范例实施例中,若某一个存储单元可存储2个比特,则假设这2个比特中从左侧算起的第1个比特为LSB并且属于下实体程序化单元,而从左侧算起的第2个比特为MSB并且属于上实体程序化单元。此外,若某一个存储单元可存储3个比特,则假设这3个比特中从左侧算起的第1个比特为LSB并且属于下实体程序化单元,从左侧算起的第2个比特为CSB并且属于中实体程序化单元,并且从左侧算起的第3个比特为MSB并且属于上实体程序化单元。

当存储器管理电路502从可复写式非易失性存储器模块406中读取n个数据比特(形成一个码字)时,则存储器管理电路502也会取得每一个数据比特的可靠度信息(亦称为通道可靠度信息)。此可靠度信息是用以表示对应的数据比特被解码为比特“1”或是“0”的机率(或称信心度)。错误检查与校正电路512会根据可靠度信息来执行解码操作。例如,此解码操作会包括叠代解码操作。

以低密度奇偶检查校正码(Low-density parity-check code,LDPC code)为例,在低密度奇偶检查校正码中,是用一个奇偶检查矩阵来定义有效的码字。码字包括了信息比特与奇偶比特。以下将信息比特与奇偶比特统称为数据比特。一般来说,奇偶检查矩阵可以表示为二分图(bipartite graph),其包括奇偶节点与信息节点。每一个奇偶节点是对应到一个校验子,而每一个信息节点是对应一个数据比特。数据比特与校验子之间的对应关系(即,信息节点与奇偶节点之间的连结)是根据奇偶检查矩阵所产生。具体来说,若奇偶检查矩阵中第i行(row)第j列(column)的元素为1,则第i个奇偶节点便会连接到第j个信息节点,其中i与j为正整数。

当存储器管理电路502从可复写式非易失性存储器模块406中读取n个数据比特(形成一个码字)时,在二分图中,信息节点也会接收到对应的可靠度信息。错误检查与校正电路512会根据二分图的结构与可靠度信息来执行解码操作。例如,此解码操作会包括叠代解码操作。在叠代解码操作中,信息节点会计算出可靠度信息给奇偶节点,并且奇偶节点也会计算出可靠度信息给信息节点。这些可靠度信息会沿着这些二分图中的边(edge)来传送。这些可靠度信息是用来表示一个节点认为某一个数据比特被解码为“1”或是“0”的机率(即,信心度)。此外,信息节点与奇偶节点的可靠度信息来计算输出的可靠度信息,其近似于计算一个数据比特被解码为“1”或是“0”的条件机率。因此,上述传送可靠度信息的过程又被称为置信传播(belief propagation)。

基于不同的算法,信息节点和/或奇偶节点会计算出不同的可靠度信息。例如,错误检查与校正电路512可以采用总和-乘积算法(Sum-Product Algorithm)、最小值-总和算法(Min-Sum Algorithm)、或是比特翻转(bit-flipping Algorithm)等算法,本发明不加以限制。

在叠代解码操作的每一次叠代中,信息节点会传递可靠度信息给奇偶节点,并且奇偶节点也会传递可靠度信息给信息节点。在每一次叠代过后,信息节点会根据目前的可靠度信息计算出每一个数据比特应该被解码为比特“1”或是“0”。在对这些计算出的数据比特执行奇偶检查程序(例如,将数据比特所形成的码字与奇偶检查矩阵相乘)后,可判断该码字是否为有效的码字。若所产生的码字为有效的码字,表示解码成功并且叠代解码操作会停止。然而,若所产生的码字不是有效的码字,则会进行下一次的叠代。若叠代解码操作的叠代次数达到一个预设值,则表示解码失败并且叠代解码操作也会停止。

在一范例实施例中,可靠度信息包括对数可能性比值(Log Likelihood Ratio,LLR)。一般来说,某一个数据比特的对数可能性比值(可能是正或负的)的绝对值越大,表示此数据比特的可靠度越高。因此,此数据比特当前的比特值就有越高的机率被视为是正确的。反之,某一个数据比特的对数可能性比值的绝对值越小,则表示此数据比特的可靠度越低。因此,此数据比特当前的比特值就有越高的机率被视为是错误的并且在当前的叠代解码操作中被更正。在一范例实施例中,叠代解码操作中使用的可靠度信息(例如,对数可能性比值)是通过查表而获得。然后,在另一范例实施例中,叠代解码操作中使用的可靠度信息亦可以是在叠代解码操作中根据特定的算法而动态地计算产生。

在可复写式非易失性存储器模块406对于存储单元的程序化操作中,若欲程序化的数据(即,欲存储的数据)是正确的,则被程序化的存储单元的临界电压可能会因不同存储单元的损耗程度不一而发生小幅度的偏移。受到此偏移影响,后续从此存储单元读取的数据可能会存在错误。一般来说,这种错误有很高的机率可以由错误检查与校正电路512执行解码操作来加以更正。例如,错误检查与校正电路512可以通过小幅度地调整用于读取此存储单元的读取电压电平或执行几次的叠代解码操作即可有效纠错。

图11是根据一范例实施例所示出的存储单元的临界电压分布发生变化的示意图。请参照图11,假设一开始可复写式非易失性存储器模块406中的多个存储单元的损耗程度很低(例如,此些存储单元的P/E计数很小)。因此,在程序化可复写式非易失性存储器模块406中的多个存储单元后,假设一部分存储状态处于抹除状态的存储单元的临界电压分布为分布1110,而另一部分存储状态处于被程序化的存储单元的临界电压分布为分布1120。若要读取此些存储单元中的至少一存储单元所存储的数据,存储器管理电路502会发送一个读取指令序列至可复写式非易失性存储器模块406。根据此读取指令序列,可复写式非易失性存储器模块406会使用一个(预设的)读取电压电平V

然而,随着可复写式非易失性存储器模块406的使用时间增加(例如,P/E计数增加)和/或操作环境改变,可复写式非易失性存储器模块406中的存储单元可能会发生性能衰退(degradation)。例如,在属于分布1110与1120的存储单元发生性能衰退后,分布1110与1120可能会逐渐相互靠近甚至相互重叠。例如,分布1111与1121分别用来表示性能衰退后的分布1110与1120。相对于分布1110与1120,分布1111与1121包含一个重叠区域1131(以斜线表示)。

发生性能衰退后,若持续使用相同的读取电压电平V

图12是根据一范例实施例所示出的硬比特模式解码操作的示意图。请参照图12,假设可复写式非易失性存储器模块406中一部分存储状态处于抹除状态的存储单元的临界电压分布为分布1210,而另一部分存储状态处于被程序化的存储单元的临界电压分布为分布1220。当欲读取存储于此些存储单元中的数据时,存储器管理电路502会发送一个读取指令序列(亦称为硬决策读取指令序列)至可复写式非易失性存储器模块406。根据此硬决策读取指令序列,可复写式非易失性存储器模块406会使用一个硬决策读取电压电平(例如,读取电压电平V

错误检查与校正电路512会根据所获得的硬比特HB

错误检查与校正电路512会根据所获得的硬比特HB

请回到图11,对于临界电压属于分布1111与1121的存储单元来说,若持续地使用此些存储单元,则此些存储单元可能会持续地发生性能衰退。例如,分布1111与1121可能会进一步改变为分布1112与1122。例如,分布1112与1122包含一个重叠区域1141(以斜线表示)。重叠区域1141的面积会大于重叠区域1131的面积。或者,临界电压属于重叠区域1141的存储单元的总数会多于临界电压属于重叠区域1131的存储单元的总数。此时,受限于硬比特模式解码操作的解码能力(或错误更正能力),即便使用再多的硬决策读取电压电平来读取存储单元并对应执行再多次的硬解码程序,可能都无法通过单次读取的硬比特来更正所有错误。

在一范例实施例中,对于临界电压属于分布1112与1122(或类似分布)的存储单元,错误检查与校正电路512会根据所获得的数据比特执行另一预设解码操作(亦称为第二预设解码操作),从而尝试使用更多信息来侦错。在一范例实施例中,第二预设解码操作亦称为软比特模式(soft-bit mode)解码操作,并且软比特模式解码操作是用于解码所读取的软比特。

图13是根据一范例实施例所示出的软比特模式解码操作的示意图。请参照图13,存储器管理电路502会发送一个读取指令序列(亦称为软决策读取指令序列)至可复写式非易失性存储器模块406。根据此软决策读取指令序列,可复写式非易失性存储器模块406会使用多个读取电压电平V

在图13的一范例实施例中,读取电压电平V

在一范例实施例中,错误检查与校正电路512会根据某一个数据比特所对应的软比特信息来获得此数据比特的可靠度信息。例如,在图13的一范例实施例中,若对应于某一个数据比特的软比特信息为“11111”,则错误检查与校正电路512会根据此软比特信息查询一查找表,以获得对应于电压区间1301的对数可能性比值。此对数可能性比值会被视为是此数据比特的可靠度信息。举例来说,错误检查与校正电路512可根据软比特信息1331查询查找表1332,以获得对应于电压区间1301的对数可能性比值-7。

然后,错误检查与校正电路512会根据此数据比特与此数据比特的可靠度信息执行软比特模式解码操作。此外,此数据比特的可靠度信息亦可能在软比特模式解码操作中经由查询其他的查找表或动态产生而被更新至少一次。关于软比特模式解码操作的细节可参照前述根据二分图的结构与可靠度信息来执行解码操作的实施例,在此便不赘述。

须注意的是,根据上述关于硬比特模式解码操作与软比特模式解码操作的说明可知,若数据比特中的错误只是单纯地因为存储单元的临界电压发生小幅度的偏移而产生(例如,存在于图11中重叠区域1131或1141),则错误检查与校正电路512执行硬比特模式解码操作或软比特模式解码操作可有效地加以更正。以图13为例,若某一个数据比特所对应的存储单元的临界电压越接近分布1310与1320之间的V形处(例如,位于电压区间1303或1304),则配置给此数据比特的对数可能性比值的绝对值可能会越小;反之,若某一个数据比特所对应的存储单元的临界电压越远离分布1310与1320之间的V形处(例如,位于电压区间1301或1306),则配置给此数据比特的对数可能性比值的绝对值可能会越大。

图14A及图14B是根据一范例实施例所示出的将写入数据、对应于写入数据的虚拟数据写入至实体程序化单元的范例。

请参照图14A,在本范例实施例中,每一个实体程序化单元会包括数据比特区1420与冗余比特区1440。其中,冗余比特区可包括一或多个记录区。例如,本范例实施例的冗余比特区1440包括第一记录区1442与第二记录区1444。

在本范例实施例中,当主机系统11传送写入指令与对应此写入指令的数据D1-1给存储器存储装置10时,存储器管理电路502会产生对应数据D1-1的虚拟数据(dummy data)。例如,虚拟数据可以是比特全为“1”的数据,本发明不在此限制。

如图14A所示,存储器管理电路502会产生对应数据D1-1的虚拟数据U1-1,并且自闲置区604提取实体抹除单元410(F)作为作动实体抹除单元。之后,存储器管理电路502会将此数据D1-1以及对应此数据D1-1的虚拟数据U1-1依序地写入至实体抹除单元410(F)的第0个实体程序化单元中。也就是说,数据D1-1是被程序化至实体抹除单元410(F)的第0个实体程序化单元的数据比特区1420中,且虚拟数据U1-1是被程序化至冗余比特区1440的第一记录区1442。此外,第二记录区1444可写入对应数据D1-1的其他数据。例如,错误检查与校正码、实体程序化单元的好坏标记等,本发明不在此限制。

请参照图14B,当主机系统11传送另一个写入指令与对应此写入指令的数据D1-2给存储器存储装置10时,存储器管理电路502会产生对应此数据D1-2的虚拟数据U1-2。在此,存储器管理电路502会将此数据D1-2以及对应此数据D1-2的虚拟数据U1-2依序地写入至实体抹除单元410(F)的第1个实体程序化单元中。也就是说,数据D1-2是被程序化至实体抹除单元410(F)的第1个实体程序化单元的数据比特区1420中,且虚拟数据U1-2是被程序化至冗余比特区1440的第一记录区1442。

在本范例实施例中,当主机系统11欲从存储器存储装置10读取数据D1-1时,存储器管理电路502会从数据D1-1写入的实体抹除单元410(F)的第0个实体程序化单元中读取多个数据比特以形成码字。并且,错误检查与校正电路512会对码字执行解码操作。此解码操作会包括叠代解码操作。具体来说,存储器管理电路502将所欲解码的码字传送至错误检查与校正电路512以进行对应的叠代解码操作,进而解码对应于此码字的数据D1-1。在接收到此码字时,错误检查与校正电路512会对所接收的码字进行叠代解码操作以辨识所接收的码字的多个数据比特。在一范例实施例中,解码操作可包括硬比特模式解码操作与软比特模式解码操作。

接着,错误检查与校正电路512会判断解码操作是否成功。如前所述,若经由叠代解码操作所产生的码字为有效的码字,表示解码成功并且叠代解码操作会停止。然而,若所产生的码字不是有效的码字,则会进行下一次的叠代。若叠代解码操作的叠代次数达到一个预设值,则表示解码失败。此预设值可由厂商设置,本发明不在此限制。需说明的是,本范例实施例所述的解码操作失败,可以是硬比特模式解码操作、软比特模式解码操作或是两者皆失败的情形,本发明不在此限制。

在本范例实施例中,若判断解码操作失败,存储器管理电路502会从码字中取得对应数据D1-1写入的实体抹除单元410(F)的第0个实体程序化单元中第一记录区1442的虚拟数据U1-1。接着,存储器管理电路502计算所取得的虚拟数据U1-1中比特值发生变化的比特变化比例,并根据比特变化比例调整解码参数。解码参数可以是在解码操作中使用的任何参数,包括但不限于读取电压电平或是对数可能性比值,本发明不在此限制。

图15A至图15C是根据一范例实施例所示出的虚拟数据的范例。请参照图15A,假设存储数据时对应数据D1-1的虚拟数据U1-1的比特全为“1”。经过时间推移,存储虚拟数据U1-1的存储单元可能会损耗而使得此存储单元的临界电压发生偏移,而造成虚拟数据U1-1存在错误。如图15B所示,存储器管理电路502所读取的虚拟数据U1-1中有部分/全部的数据比特包括比特“0”,此现象表示当前临界电压的偏移。于此,存储器管理电路502可计算所读取的虚拟数据U1-1中比特“1”变化为“0”的比特变化比例(如,图15B比特为“0”的比特变化比例为1/24)。如图15C所示,存储器管理电路502所读取的虚拟数据U1-1中有6个数据比特包括比特“0”,此现象表示当前临界电压的偏移更为严重。于此,存储器管理电路502可计算所读取的虚拟数据U1-1中比特“1”变化为“0”的比特变化比例为6/24。

在一范例实施例中,存储器管理电路502可根据比特变化比例决定一个补偿值,并根据此补偿值调整解码参数为新的解码参数。例如,存储器管理电路502会根据此比特变化比例查询一查找表,以获得补偿值。此外,存储器管理电路502也可以根据一方程式计算此比特变化比例对应的补偿值,本发明不在此限制。

以下实施例以读取电压电平为例进行具体说明。图16是根据一范例实施例所示出的存储单元的临界电压分布发生变化的示意图。请参照图16,在程序化可复写式非易失性存储器模块406中的多个存储单元后,假设一部分存储状态处于抹除状态的存储单元的临界电压分布为分布1610,而另一部分存储状态处于被程序化的存储单元的临界电压分布为分布1620。在可复写式非易失性存储器模块406的存储单元发生性能衰退后,存储状态处于抹除状态的存储单元的临界电压分布可能从分布1610逐渐衰退为分布1611或分布1612。在本范例实施例中,解码操作中包括搜寻最佳读取电压电平算法,存储器管理电路502可执行此搜寻最佳读取电压算法以计算用于解码操作的读取电压电平V

表1

以存储状态处于抹除状态的存储单元的临界电压分布衰退为分布1611为例。假设当前的读取电压电平为读取电压电平V

在本发明另一实施例中,存储器管理电路502也可以根据比特变化比例修正执行搜寻最佳读取电压算法,以使得执行修正后的搜寻最佳读取电压算法可获得上述实施例的读取电压电平V

以下实施例以对数可能性比值为例进行具体说明。在本范例实施例中,解码操作中包括对数可能性比值预测算法,存储器管理电路502可执行此对数可能性比值预测算法来计算用于解码操作的对数可能性比值。在本范例实施例中,存储器管理电路502可根据比特变化比例查询查找表来决定补偿值,并且根据此补偿值调整对数可能性比值。表2示出比特变化比例与补偿值的查找表范例,其中比特变化比例为比特“1”变化为“0”的比例。

表2

假设存储器管理电路502执行对数可能性比值预测算法后,当前计算出对应每个电压区间的对数可能性比值如下表3所示,且存储器管理电路502计算出的比特变化比例为95%。

表3

存储器管理电路502会根据比特变化比例95%查询表2来决定补偿值为-1,并且将对应各电压区间的对数可能性比值减1以调整对数可能性比值为如下表4所示。在本范例实施例中,电压区间1~4的对数可能性比值调整为正值时最高调整至+1,区间5~8的对数可能性比值调整为负值时最低调整至-1,本发明不在此限制。如此一来,存储器管理电路502可决定执行对数可能性比值预测算法得到的对数可能性比值需要做多少补偿才能得到真正符合当前存储单元的临界电压分布的对数可能性比值。

表4

在本发明另一实施例中,存储器管理电路502也可以根据比特变化比例修正对数可能性比值预测算法,以使得执行修正后的对数可能性比值预测算法可获得如上表4的对数可能性比值。如此一来,下次欲计算对数可能性比值时,即可执行修正后的对数可能性比值预测算法来计算用于解码操作的对数可能性比值。

之后,错误检查与校正电路512会利用调整后的读取电压电平或调整后的对数可能性比值对码字进行解码操作。具体来说,在获得调整后的读取电压电平或调整后的对数可能性比值后,存储器管理电路502可利用所述读取电压电平从实体程序化单元(数据D1-1写入的实体抹除单元410(F)的第0个实体程序化单元)再次读取多个数据比特以形成码字,并且错误检查与校正电路512对所述码字进行硬比特模式解码操作。此外,错误检查与校正电路512也可根据所述对数可能性比值对原先读取的所述码字进行软比特模式解码操作。

需注意的是,存储器管理电路502也可在解码操作时即实施上述范例实施例提供的方法,本发明不限制必须在解码操作失败后才实施上述方法。

图17是根据一范例实施例所示出的数据存取方法的流程图。

请参照图17,在步骤S1702中,读取实体程序化单元存储的码字,并计算所述码字包括的虚拟数据中比特值发生变化的比特变化比例。在步骤S1704中,根据所述比特变化比例调整读取电压电平或对数可能性比值。在步骤S176中,利用调整后的所述读取电压电平或调整后的所述对数可能性比值对所述码字进行所述解码操作。

然而,图17中各步骤已详细说明如上,在此便不再赘述。值得注意的是,图17中各步骤可以实作为多个代码或是电路,本发明不加以限制。此外,图17的方法可以搭配以上范例实施例使用,也可以单独使用,本发明不加以限制。

综上所述,本发明实施例所提供的数据存取方法、存储器控制电路单元以及存储器存储装置,可在解码时根据存储数据时与数据一同写入可复写式非易失性存储器模块的虚拟数据的比特变化比例调整读取电压电平或对数可能性比值,并根据调整后的读取电压电平或对数可能性比值执行解码操作。另外,本发明实施例还可在解码失败后根据虚拟数据的比特变化比例调整读取电压电平或对数可能性比值,并再次执行解码操作。如此一来,本发明实施例可预测出符合当前存储单元的临界电压分布的读取电压电平或对数可能性比值。此外,针对数据比特处于抹除状态的临界电压分布异于处于其他程序化状态的临界电压分布的问题,可通过本发明提供的实施例获得符合处于抹除状态的临界电压分布的读取电压电平或对数可能性比值。据此,可提升解码效率,进而提升读取数据的效率与正确性。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 数据存取方法、存储器控制电路单元以及存储器存储装置

- 数据存取方法、存储器控制电路单元与存储器存储装置