一种SPI访问控制方法、系统、计算设备及存储介质

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及存储设备技术领域,尤其涉及一种SPI访问控制方法、系统、计算设备及存储介质。

背景技术

SPI(Serial Peripheral Interface,串行外设接口)通信总线具有高速、全双工和同步的特质,在芯片的管脚上只占用四根线,能够节约芯片的管脚,同时为PCB的布局上节省空间。由于SPI简单易行的优势,在多个领域得以广泛应用,SPI存储设备作为一种常用的数据存储部件,在系统设计中常被用于存储固件程序及其相关的配置数据。

目前,由于应用场景的需求,一些SPI主设备上会接入多个SPI从设备,当其中一个SPI从设备内的固件程序无法完成系统启动,例如该SPI从设备的固件程序遭到破坏时,则切换到另一个SPI从设备以载入新的固件启动系统,从而以满足使用需求。但由于这种方式需要用到两个SPI从设备,成本较高;此外,由于需要为多个SPI从设备的安装预留空间,因此存在一定的安装限制。

发明内容

针对现有技术的不足,本发明提供一种SPI访问控制方法、系统、计算设备及存储介质,解决现有技术中,当需要使用多个SPI从设备时,成本较高且存在安装限制的问题。

为实现上述目的,本发明提供以下的技术方案:

一种SPI访问控制方法,应用于SPI主设备对SPI从设备的访问,所述SPI从设备的存储空间至少划分成两个存储区间;

所述SPI访问控制方法包括:

在所述SPI主设备请求访问所述SPI从设备时,截获所述SPI主设备向所述SPI从设备发送的访问信号;所述访问信号包括逻辑地址和信号来源标志;

依据所述信号来源标志修改所述逻辑地址,将所述SPI主设备对所述SPI从设备的访问请求,映射至与修改后的逻辑地址对应的存储区间;

将修改后的逻辑地址对应的存储区间作为访问区间,使所述SPI主设备与所述访问区间之间建立通信连接。

可选地,每个所述存储区间分别包括多个物理地址;

所述使SPI主设备与所述访问区间之间建立通信连接,包括:

获取所述访问区间中的所述多个物理地址;

将所述多个物理地址依次作为访问对象进行访问,直至截获到所述SPI主设备向SPI从设备发送的终止访问信号时,停止所述访问。

可选地,所述将所述多个物理地址依次作为访问对象进行访问,包括:

以所述访问区间中位于首位的物理地址作为首个访问对象;

比较所述当前访问的物理地址和所述访问区间中位于末位的物理地址;

若所述当前访问的物理地址小于或等于所述访问区间中位于末位的物理地址,接收所述访问对象返回的应答信息,将所述应答信息转发至所述SPI主设备,并对当前访问的物理地址进行附加计算,将计算所得的物理地址作为下一访问对象继续访问。

可选地,所述将所述多个物理地址依次作为访问对象进行访问,还包括:

若所述当前访问的物理地址大于所述访问区间中位于末位的物理地址,向所述SPI主设备发送预设的虚假应答信息,使所述SPI主设备向所述SPI从设备发送终止访问信号;

当截获到所述SPI主设备向SPI从设备发送的终止访问信号时,停止将当前访问对象返回的应答信息转发至所述SPI主设备。

可选地,在所述SPI主设备请求访问SPI从设备时,还包括:

将所述SPI从设备中除所述访问区间之外的存储区间设置为即写保护状态。

本发明还提供了一种SPI访问控制系统,用于实现如上任一项所述的SPI访问控制方法,包括SPI主设备和SPI从设备,所述SPI从设备的存储空间至少划分成两个存储区间,所述SPI主设备与SPI从设备之间通过一逻辑器件桥接;

所述逻辑器件用于:

在所述SPI主设备请求访问所述SPI从设备时,截获所述SPI主设备向所述SPI从设备发送的访问信号;所述访问信号包括逻辑地址和信号来源标志;

依据所述信号来源标志修改所述逻辑地址,使所述SPI主设备对所述SPI从设备的访问请求,映射至与修改后的逻辑地址对应的存储区间;

将修改后的逻辑地址对应的存储区间作为访问区间,并使所述SPI主设备与所述访问区间之间建立通信连接。

可选地,每个所述存储区间分别包括多个物理地址;

所述逻辑器件用于在使所述SPI主设备与所述访问区间之间建立通信连接时:

获取所述访问区间中的所述多个物理地址;

以所述访问区间中位于首位的物理地址作为首个访问对象,对当前访问的物理地址进行附加计算,将计算所得的物理地址作为下一个访问对象;

将所述多个物理地址依次作为访问对象进行访问,直至截获到所述SPI主设备向SPI从设备发送的终止访问信号时,停止所述访问;

所述将所述多个物理地址依次作为访问对象进行访问,包括:

以所述访问区间中位于首位的物理地址作为首个访问对象;

比较所述当前访问的物理地址和所述访问区间中位于末位的物理地址;

若所述当前访问的物理地址小于或等于所述访问区间中位于末位的物理地址,接收所述访问对象返回的应答信息,将所述应答信息转发至所述SPI主设备,并对当前访问的物理地址进行附加计算,将计算所得的物理地址作为下一访问对象继续访问;

若所述当前访问的物理地址大于所述访问区间中位于末位的物理地址,向所述SPI主设备发送预设的虚假应答信息,使所述SPI主设备向所述SPI从设备发送终止访问信号;

当截获到所述SPI主设备向SPI从设备发送的终止访问信号时,停止将当前访问对象返回的应答信息转发至所述SPI主设备。

可选地,所述逻辑器件还用于在所述SPI主设备与所述访问区间之间建立通信连接时:

将所述SPI从设备中除所述访问区间之外的存储区间设置为即写保护状态。

本发明还提供了一种计算设备,包括:

存储器,用于存储程序指令;

处理器,用于调用所述存储器中存储的程序指令,按照获得的程序执行如上任一项所述的SPI访问控制方法。

本发明还提供了一种计算机可读非易失性存储介质,包括计算机可读指令,当计算机读取并执行所述计算机可读指令时,使得计算机执行如上任一项所述的SPI访问控制方法。

与现有技术相比,本发明具有以下有益效果:

本发明通过监控SPI主设备向SPI从设备的访问请求,并修改访问请求中的逻辑地址,使得SPI主设备访问请求得以映射至SPI从设备中各个存储区间中的其中一个,以利用单个SPI从设备达到多个SPI从设备的效果,降低成本的同时也克服了存在安装限制的问题。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其它的附图。

图1为8Pin脚封装的SPI Flash的结构示意图;

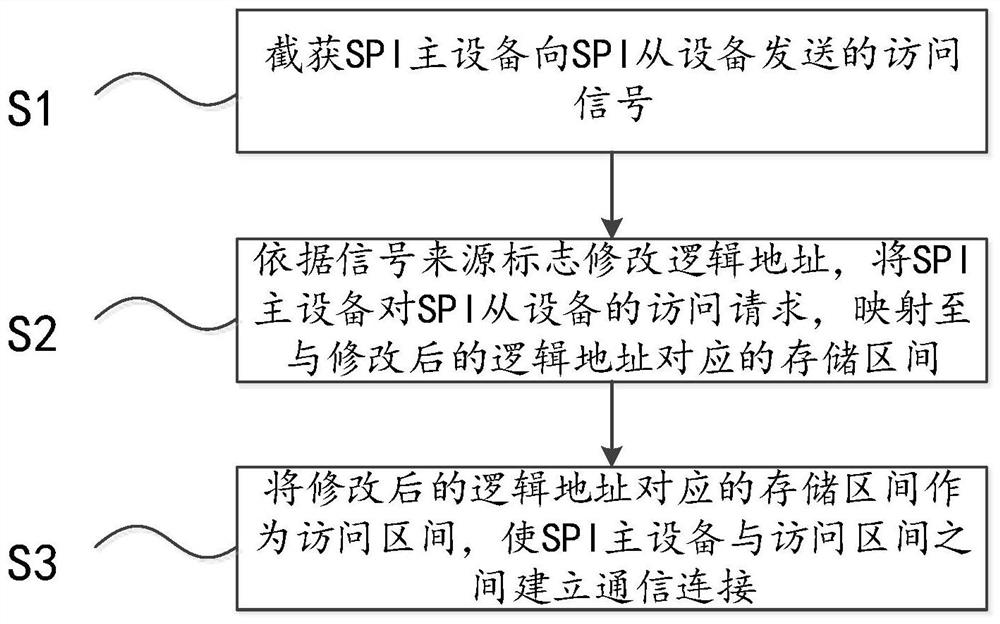

图2为本发明提供的一种SPI访问控制方法的流程图;

图3为本发明提供的一种SPI访问控制方法中步骤S3的流程图;

图4为本发明提供的一种SPI访问控制方法中步骤S32的流程图;

图5为本发明提供的一种SPI访问控制方法中步骤S4的流程图;

图6为本发明提供的一种SPI访问控制系统的结构示意图;

图7为华邦电子公司型号为25Q128FV的SPI Flash中,“Read Data”命令的SPI时序图。

具体实施方式

为使得本发明的目的、特征、优点能够更加的明显和易懂,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,下面所描述的实施例仅仅是本发明一部分实施例,而非全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

由于应用场景的需求,一些SPI主设备上会接入多个SPI从设备,通过SPI主设备引脚/CS(chip select,芯片选择)的使能以实现SPI主设备对SPI从设备的访问。以两个SPI从设备的设计为例,接入方式包括如下情形:

同一个SPI主设备上接入两个SPI从设备,并在两个SPI从设备中分别放入系统固件;若其中的一个SPI从设备内的固件程序无法完成系统启动(例如遭到破坏时),则切换到另一个SPI从设备中并载入新的固件启动系统;这种方式需要用到两个SPI从设备,成本较高;此外,由于需要为两个SPI从设备的安装预留空间,因此存在一定的安装限制。

本发明旨在于提供一种SPI访问方案,以克服现有技术的如上问题。

为便于理解本发明提供的技术方案,在此对本发明所涉及的专业术语进行解释:

SPI(Serial Peripheral Interface),串行外设接口,是一种高速、双全工且同步的通信总线,在芯片的管脚上只占四根线。

SPI Flash(SPI NOR Flash),具有读速度块,可字节访问等特点,通常用来做固件程序的存储,是一种长寿命的非易失性存储器,在断电情况下仍能保持所存储的数据信息;数据删除不是以单个字节为单位,是以固定区块为单位,区块大小一般为256KB到20MB。

BIOS(Basic Input Output System),即基本输入/输出系统。

CPLD(Complex Programmable Logic Device),即复杂可编程逻辑器件。

SOC(System on Chip,系统级芯片)厂商一般需要将识别引导介质类型的程序固化到芯片的ROM(Read Only Memory,只读存储器)中,由于ROM是只读的,为了保证对多种类型SPI Flash的兼容,需要引导代码对启动介质进行识别和引导。

ROM从SPI Flash搬移启动引导程序至内部RAM(random access memory,随机存取存储器),并跳转至RAM执行启动引导程序,由启动引导程序完成频率配置、板级配置和DDR初始化等,下载并执行操作系统。

请参考图1,在此以8Pin脚封装的SPI Flash为例,对其各引脚的功能进行解释:

/CS-chip select(芯片选择):该信号被拉低后,SPI从设备被SPI主设备选中并对SPI Master的请求做出响应。

CLK-clock(时钟):由SPI主设备送出的时钟同步信号。

/WP–write protect(写入保护):该信号被拉低后,SPI从设备的状态和控制寄存器被禁止写入新数据,直到重新上电。

DI–data in(输入数据):SPI主设备的请求数据在该信号上通过串行方式送入SPI从设备。

DO–data out(输出数据):SPI从设备对SPI主设备的请求的响应数据在该信号上通过串行方式返回给SPI主设备。

请参考图2,本发明实施例提供一种SPI访问控制方法,应用于SPI主设备对SPI从设备的访问,SPI从设备的存储空间至少划分成两个存储区间。

具体地,在SPI主设备请求访问SPI从设备时,该SPI访问控制方法包括:

S1、截获SPI主设备向SPI从设备发送的访问信号。

具体地,步骤S1中,由SPI主设备发出的访问信号包括逻辑地址和信号来源标志。

可以理解的是,SPI主设备可以包括至少两个用于选择所访问的存储区间的/CS(chip select,芯片选择)引脚,如/CS0和/CS1;在请求访问SPI从设备时,SPI主设备基于访问需求使能/CS0和/CS1中的任一个,使得SPI主设备向SPI从设备发送的访问信号中包含/CS0或/CS1的信号来源标志,从而为该步骤中修改逻辑地址提供依据。

S2、依据信号来源标志修改逻辑地址,将SPI主设备对SPI从设备的访问请求,映射至与修改后的逻辑地址对应的存储区间。

可以理解的是,事先建立好SPI从设备中各存储区间与不同的逻辑地址之间的映射关系,使得按照信号来源标志修改后的逻辑地址所映射的存储区间,与SPI主设备的访问请求相符合。

在该步骤中,当截获到来自SPI主设备的访问信号时,根据该信号来源标志,对访问信号中原本包含的逻辑地址进行修改,使得修改后的逻辑地址与SPI从设备中的其中一个存储区间具有唯一的对应关系,从而将SPI主设备对SPI从设备的访问请求,映射至与修改后的逻辑地址对应的存储区间。

S3、将修改后的逻辑地址对应的存储区间作为访问区间,使SPI主设备与访问区间之间建立通信连接。

通过前述步骤,使得SPI主设备访问请求得以映射至SPI从设备中各个存储区间中的其中一个,以利用单个SPI从设备达到多个SPI从设备的效果,降低成本的同时也克服了存在安装限制的问题。

当系统上电后,首先执行一段特定程序判断哪一个固件(即SPI从设备中的存储区间)用于启动系统,例如,该特定程序首先校验第一固件的完整性,一旦校验失败则使用第二固件启动系统。

可以理解的是,一个容量为16MB的SPI从设备,其容量是容量为8MB的SPI从设备的两倍,但16MB的SPI从设备在成本上仍然优于两个8MB的SPI从设备,因此能够达到节约成本的目的。此外,对于一些小板卡型的系统设计,空间往往是制约其部件选型的关键;利用单个SPI从设备节约空间,能够为系统布局提供更多的选择空间。

可以理解的是,利用软件方式使单个SPI从设备具备双固件功能的设计存在一定的缺陷,具体如下:由于两个系统固件同处于一个SPI从设备中,两个固件之间缺乏隔离保护。在任意一次系统启动中,无论是使用了哪个固件,另一个系统固件都能够被SPI主设备直接访问到,甚至有被擦除的可能,导致可靠性降低。

由于目前的SPI存储设备普遍具有单指令读取整个SPI从设备存储空间中数据的能力,例如,当SPI从设备在接受“Read(读)”指令后,从指定地址开始逐个返回应答信息,直到SPI主设备的所有/CS引脚信号拉高时才停止数据获取。因此,SPI主设备在获取第一个应答信息后,通过延长/CS信号的时钟周期即可获取到SPI从设备存储空间中的所有数据。

为了提高SPI从设备的存储空间中各存储区间的隔离性,本实施例中,每个存储区间分别包括多个物理地址。

请参考图3,基于此,该SPI访问控制方法中,步骤S3具体包括:

S31、获取访问区间中的多个物理地址;

S32、将多个物理地址依次作为访问对象进行访问,直至截获到SPI主设备向SPI从设备发送的终止访问信号时,停止访问。

请参考图4,进一步地,步骤S32包括:

S321、以访问区间中位于首位的物理地址作为首个访问对象;

S322、比较当前访问的物理地址和访问区间中位于末位的物理地址,判断当前访问的物理地址是否大于访问区间中位于末位的物理地址;若是,执行步骤S324,若否,执行步骤S323;

S323、接收访问对象返回的应答信息,将应答信息转发至SPI主设备;对当前访问的物理地址进行附加计算,将计算所得的物理地址作为下一访问对象继续访问,返回步骤S322;

S324、向SPI主设备发送预设的虚假应答信息,使SPI主设备向SPI从设备发送终止访问信号。

S325、当截获到SPI主设备向SPI从设备发送的终止访问信号时,停止将当前访问对象返回的应答信息转发至SPI主设备。

可以理解的是,利用步骤S321-步骤S325,使得某一时刻只能有一个存储区间被访问到,且对该存储区间的访问操作不对其他区间产生影响。

此外,通过控制所访问的物理地址中的最大值不超过该访问区间中位于末位的物理地址,即,无论SPI主设备访问SPI从设备中划分得到的哪一个存储区间,其访问起始地址始终为0x0,最大访问地址为该存储区间的大小,从而阻止SPI主设备对SPI从设备中除访问区间以外的存储区间进行访问。

可以理解的是,SPI从设备中划分所得的存储区间的容量大小可根据实际需求动态调整,具有较高的灵活性。

进一步地,SPI存储设备通常还具有芯片擦除功能,当SPI主设备向SPI从设备发送“Chip Erase(芯片擦除)”命令,即可擦除SPI从设备的整个存储空间内的数据,包括除访问区间之外的其他存储区间。

请参考图5,基于此,在SPI主设备请求访问SPI从设备时,还包括如下步骤:

S4、将SPI从设备中除访问区间之外的存储区间设置为即写保护状态。

具体地,该步骤中,在SPI主设备请求与SPI从设备建立通信连接之前,将除访问区间之外的存储区间设置为“Protected”(即写保护),对该存储区间发出的“Chip Erase”命令将不会被执行。

如图6所示,基于前述实施例,本发明实施例还提供了一种SPI访问控制系统,包括SPI主设备和SPI从设备,SPI从设备的存储空间至少划分成两个存储区间,SPI主设备与SPI从设备之间通过一逻辑器件桥接。

本实施例中,SPI主设备为SPI Master(主机)的CPU,SPI从设备包括SPI ROM和SPIFlash,逻辑器件为CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)。其中,CPU包括DO引脚、DI引脚、CLK引脚和/CS引脚,且CPU至少包括两种类型的/CS引脚,如/CS0和/CS1;SPI ROM包括DO引脚、DI引脚、CLK引脚和/CS引脚。

进一步地,以SPI ROM的存储空间分为两个存储区间为例,两个存储区间分别为BIOS0和BIOS1。

存储区间BIOS0包括的物理地址为0x000000-0x7FFFFF,存储区间BIOS1包括的物理地址为0x800000-0xFFFFFF。

本实施例中,SPI从设备不与SPI主设备直连,而是中间通过逻辑器件进行桥接。逻辑器件对桥接的SPI信号进行监控并修改特定时序下的DI信号,从而达成将SPI主设备的访问请求映射到指定的SPI从设备存储区间的目的。

本实施例中,逻辑器件用于:

在SPI主设备请求访问SPI从设备时,截获SPI主设备向SPI从设备发送的访问信号;访问信号包括逻辑地址和信号来源标志。逻辑器件依据信号来源标志修改逻辑地址,使SPI主设备对SPI从设备的访问请求,映射至与修改后的逻辑地址对应的存储区间。

请参考图7,图7为华邦电子公司型号为25Q128FV的SPI Flash中,“Read Data”命令(03h)的SPI时序图。可见,当/CS信号使能后,CLK信号上的前8个时钟周期采样DI上的数据为SPI操作命令(03h);紧跟其后的24个时钟周期采样DI信号上的数据为SPI Flash的24-Bit Address(共24Bit的访问地址),该访问地址共16MB容量,也即前述的逻辑地址;最后的8个时钟周期或者多个时钟周期在DO信号上返回存放在该SPI Flash地址的一个或者多个Bytes(字节)数据,该Bytes数据也即应答信息。

通过对该时序图分析可知,当24-Bit Address中的第23个Bit的电平状态(即/CS信号使能后,在第9个时钟周期内采样DI信号上的电平状态)为低时,对SPI Flash的访问空间为0x000000-0x7FFFFF,即SPI Flash的前半段地址空间;当24-Bit Address中的第bit23为高时,对SPI Flash的访问空间为0x800000-0xFFFFFF,即SPI ROM的后半段地址空间。以上,通过修改DI信号线上的bit23即可实现将CPU访问映射到不同的区间。

逻辑器件将修改后的逻辑地址对应的存储区间作为SPI主设备的访问区间,使SPI主设备与访问区间之间建立通信连接。

由于每个存储区间分别包括多个物理地址,逻辑器件用于在使SPI主设备与访问区间之间建立通信连接时,首先获取访问区间中的多个物理地址,然后以访问区间中位于首位的物理地址作为首个访问对象,对当前访问的物理地址进行附加计算,将计算所得的物理地址作为下一个访问对象。将多个物理地址依次作为访问对象进行访问,直至截获到SPI主设备向SPI从设备发送的终止访问信号时,停止访问。

具体地,逻辑器件将多个物理地址依次作为访问对象进行访问时,以访问区间中位于首位的物理地址作为首个访问对象,对当前访问的物理地址进行附加计算,将计算所得的物理地址作为下一个访问对象继续访问;比较当前访问的物理地址和访问区间中位于末位的物理地址。

若当前访问的物理地址小于或等于访问区间中位于末位的物理地址,接收访问对象返回的应答信息,将应答信息转发至SPI主设备;若当前访问的物理地址大于访问区间中位于末位的物理地址,向SPI主设备发送预设的虚假应答信息,使SPI主设备向SPI从设备发送终止访问信号。

当截获到SPI主设备向SPI从设备发送的终止访问信号时,逻辑器件停止将当前访问对象返回的应答信息转发至SPI主设备,从而实现SPI从设备中各存储之间的隔离效果。

例如,逻辑器件首先记录当前访问区间中位于首位的物理地址,当SPI从设备返回一个应答信息后,SPI主设备的/CS引脚信号没有被拉高,则逻辑器件将首位的物理地址加一,得到一个新的访问地址,并将该新访问地址与该访问区间中位于末位的物理地址,也即该访问区间的最大地址做比较。

若新地址大于访问区间的最大地址,则逻辑器件拉高SPI从设备端的/CS信号,阻断后续访问。同时在SPI主设备端,逻辑器件返回一个虚假的应答信息,例如无效值0xFF;当SPI主设备收到无效值0xFF时,拉高CPU端的/CS信号,并向SPI从设备发送终止访问信号;直到CPU端的/CS信号重新被拉低,使/CS引脚的信号重新使能,从而开始新一轮的SPI主设备对SPI从设备的访问。

进一步地,逻辑器件还用于在SPI主设备与访问区间之间建立通信连接时,在SPI主设备对访问区间进行访问之前,将SPI从设备中除访问区间之外的存储区间设置为即写保护状态。

由于SPI Flash还具有Chip Erase(芯片擦除)功能,SPI主设备向SPI Flash发送“Chip Erase”命令即可将SPI从设备中整个存储空间内的数据全部擦除,包括当前的访问区间之外的存储区间。因此,逻辑器件需要阻断Chip Erase功能,以避免未被访问的存储区间中的数据被擦除。

具体地,当SPI Flash的某一个Block(块)被设置为“Protected”(即写保护)时,“Chip Erase”命令将不会被执行。

为实现阻断芯片擦除操作,CPLD在CPU访问SPI Flash前,首先初始化SPI Flash,将当前访问区间之外的存储区间内的任一Block设置为“Protected”状态,并将SPI Flash端的/WP(Write Protect)拉低,防止该“Protected”状态下的Block被重置。当CPU开始访问SPI Flash时,由于“Protected”状态的Block的存在且属性无法被修改,即使发送了“ChipErase”命令也会被SPI Flash拒绝执行,从而保护当前非访问射区间的数据安全。

基于前述实施例,本发明实施例还提供了一种计算设备,包括:

存储器,用于存储程序指令;

处理器,用于调用存储器中存储的程序指令,按照获得的程序执行如上实施例提供的SPI访问控制方法。

基于前述实施例,本发明实施例还提供了一种计算机可读非易失性存储介质,包括计算机可读指令,当计算机读取并执行计算机可读指令时,使得计算机执行如上实施例提供的SPI访问控制方法。

综上,本发明提供的SPI访问控制技术,能够将一颗大容量的SPI存储设备虚拟成多个容量较小且彼此之间相互隔离的存储设备,具有如下优势:

1)节省成本。在成本上一颗16MB容量的SPI ROM依然较2颗8MB容量的SPI ROM更为便宜,因此单个SPI ROM的设计能够降低成本。

2)节省空间。对于一些小板卡型的系统设计,空间往往是制约其部件选型的关键。单颗SPI ROM的设计能够为系统布局提供更多空间选择。

3)有效利用剩余空间。独立使用的单颗SPI ROM在存储数据时往往不能将剩余容量完全用完,造成浪费;若将单颗SPI ROM划分为多个存储空间,则能够有效利用这部分的剩余容量,从而有效利用剩余空间。

4)增加灵活性。由于存储区间是通过分割单个SPI从设备的存储空间虚得到的,因此能够根据需求动态调整存储区间的划分,为灵活的系统设计增加更多可能。

- 一种SPI访问控制方法、系统、计算设备及存储介质

- 一种访问控制方法、系统及计算设备