一种面板画素排列结构及其驱动方法

文献发布时间:2023-06-19 11:57:35

技术领域

本发明涉及面板画素排列结构技术领域,特别涉及一种面板画素排列结构及其驱动方法。

背景技术

Demux(解复用)液晶显示屏在制程上由于制程的不稳定性及不可控性,Demux TFT开关的Ion(TFT打开时的开启电流)会不一样,这样就会造成有的Demux TFT开关连接的Source Line(源极走线)上的子画素(R/G/B)的充电率就会有所不同,从而会导致每一条Source Line上的子画素的显示亮度会不一样,从而出现亮暗竖线的产生,影响Demux液晶显示屏的显示品质。

发明内容

本发明所要解决的技术问题是:提供一种面板画素排列结构及其驱动方法,可使像素的显示亮度得到综合,从而消除面板亮暗竖线的产生。

为了解决上述技术问题,本发明采用的第一种技术方案为:

一种面板画素排列结构,包括两个以上的像素单元、第一Demux走线、第二Demux走线、第三Demux走线、多条数据走线和多条栅极走线,一个所述像素单元配置两条栅极走线且位于两条栅极走线之间;

每个所述像素单元包括从左至右依次排列的六列子像素对和七条数据走线,一列所述子像素对配置两条数据走线且位于两条数据走线之间,相邻的两列所述子像素对共用一条数据走线;

一个所述像素单元中从左至右依次排列的第二条数据走线至第七条数据走线均分别连接一个TFT开关,一个所述像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的TFT开关的栅极均分别与第一Demux走线电连接,一个所述像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的TFT开关的栅极均分别与第二Demux走线电连接,一个所述像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的TFT开关的栅极均分别与第三Demux走线电连接;

每个所述TFT开关的输入端分别连接有一条源极走线,一个所述像素单元中从左至右依次排列的第二条数据走线、第四条数据走线和第六数据走线所连接的TFT开关共用一条源极走线,一个所述像素单元中从左至右依次排列的第三条数据走线、第五条数据走线和第七数据走线所连接的TFT开关共用一条源极走线。

本发明采用的第二种技术方案为:

一种面板画素排列结构的驱动方法,包括以下步骤:

步骤S1、在一个像素单元中,控制两条栅极走线中的一条栅极走线开启;

步骤S2、在一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至一个像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输一个像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至一个像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的像素对中;

步骤S3、控制两条栅极走线中的另一条栅极走线开启;

步骤S4、在另一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至一个像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输一个像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至一个像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的像素对中;

步骤S5、循环步骤S1-S4,驱动每个像素单元。

本发明的有益效果在于:

通过设置第一Demux走线、第二Demux走线和第三Demux走线分别与像素单元中的TFT开关对应连接,第一Demux走线控制一个像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的TFT开关的信号输入情况,第二Demux走线控制一个像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的TFT开关的信号输入情况,第三Demux走线控制一个像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的TFT开关的信号输入情况,这样能够改变像素单元中画素的排列方式,从而改善Demux液晶显示屏显示不良的问题,改善制程不良导致的Demux液晶显示屏显示不良的现象;而且节省了制程优化所需要花费的制程成本,增加材料的利用率,又可达到忽视制程差异造成的不良,改善Demux液晶显示屏的显示品质,发展前景良好。

附图说明

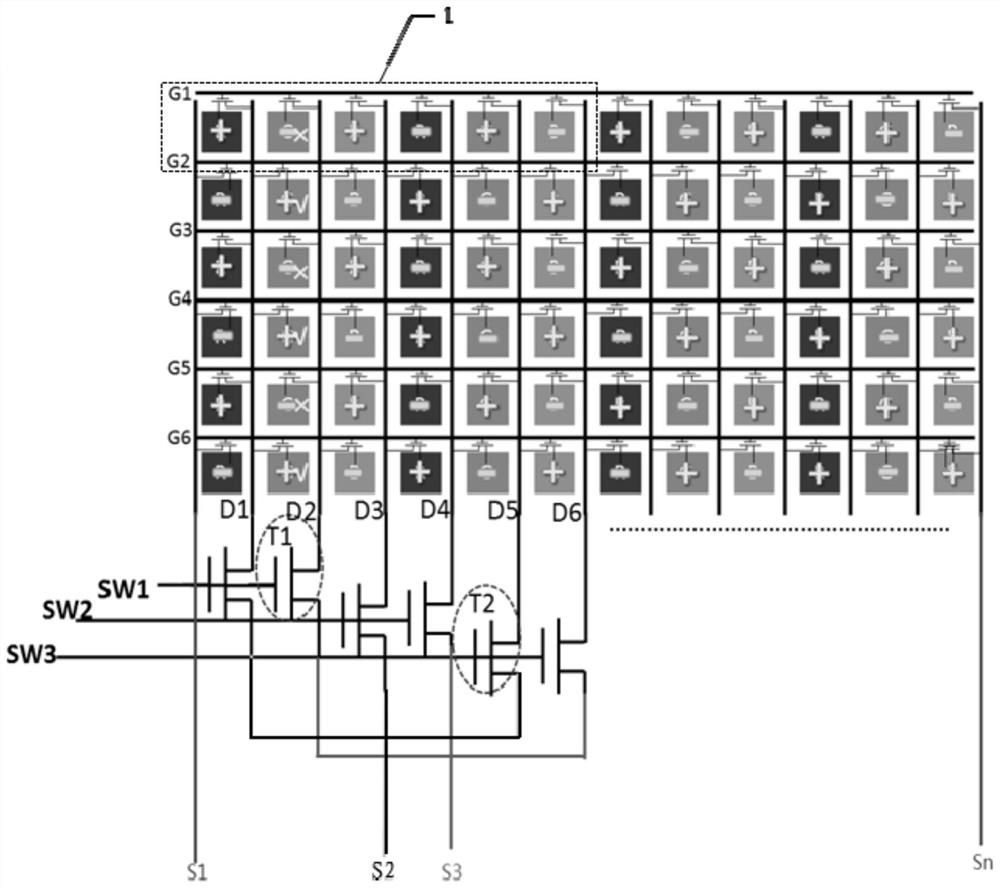

图1为根据本发明的一种面板画素排列结构的结构示意图;

图2为根据本发明的一种面板画素排列结构的正确显示的纯色画面图;

图3为根据本发明的一种面板画素排列结构的异常显示的纯色画面图;

图4为根据本发明的一种面板画素排列结构的优化画素排列的奇数条源极走线数据映射的波形图;

图5为根据本发明的一种面板画素排列结构的优化画素排列的偶数条源极走线数据映射的波形图;

图6为根据本发明的一种面板画素排列结构的驱动方法的步骤流程图;

标号说明:

1、像素单元。

具体实施方式

为详细说明本发明的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

请参照图1,本发明提供的一种技术方案:

一种面板画素排列结构,包括两个以上的像素单元、第一Demux走线、第二Demux走线、第三Demux走线、多条数据走线和多条栅极走线,一个所述像素单元配置两条栅极走线且位于两条栅极走线之间;

每个所述像素单元包括从左至右依次排列的六列子像素对和七条数据走线,一列所述子像素对配置两条数据走线且位于两条数据走线之间,相邻的两列所述子像素对共用一条数据走线;

一个所述像素单元中从左至右依次排列的第二条数据走线至第七条数据走线均分别连接一个TFT开关,一个所述像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的TFT开关的栅极均分别与第一Demux走线电连接,一个所述像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的TFT开关的栅极均分别与第二Demux走线电连接,一个所述像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的TFT开关的栅极均分别与第三Demux走线电连接;

每个所述TFT开关的输入端分别连接有一条源极走线,一个所述像素单元中从左至右依次排列的第二条数据走线、第四条数据走线和第六数据走线所连接的TFT开关共用一条源极走线,一个所述像素单元中从左至右依次排列的第三条数据走线、第五条数据走线和第七数据走线所连接的TFT开关共用一条源极走线。

从上述描述可知,本发明的有益效果在于:

通过设置第一Demux走线、第二Demux走线和第三Demux走线分别与像素单元中的TFT开关对应连接,第一Demux走线控制一个像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的TFT开关的信号输入情况,第二Demux走线控制一个像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的TFT开关的信号输入情况,第三Demux走线控制一个像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的TFT开关的信号输入情况,这样能够改变像素单元中画素的排列方式,从而改善Demux液晶显示屏显示不良的问题,改善制程不良导致的Demux液晶显示屏显示不良的现象;而且节省了制程优化所需要花费的制程成本,增加材料的利用率,又可达到忽视制程差异造成的不良,改善Demux液晶显示屏的显示品质,发展前景良好。

进一步的,一个所述像素单元中从左至右依次排列的第一条数据走线单独连接一条源极走线。

进一步的,一个所述子像素对包括一个子像素,所述像素单元中的所有子像素以R、G和B的方式依次阵列排布。

进一步的,一个所述像素对中的一个子像素分别对应连接一条数据走线和栅极走线。

请参照图2,本发明提供的另一种技术方案:

一种面板画素排列结构的驱动方法,包括以下步骤:

步骤S1、在一个像素单元中,控制两条栅极走线中的一条栅极走线开启;

步骤S2、在一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至一个像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输一个像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至一个像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的像素对中;

步骤S3、控制两条栅极走线中的另一条栅极走线开启;

步骤S4、在另一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至一个像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输一个像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至一个像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的像素对中;

步骤S5、循环步骤S1-S4,驱动每个像素单元。

从上述描述可知,本发明的有益效果在于:

通过设置第一Demux走线、第二Demux走线和第三Demux走线分别与像素单元中的TFT开关对应连接,第一Demux走线控制一个像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的TFT开关的信号输入情况,第二Demux走线控制一个像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的TFT开关的信号输入情况,第三Demux走线控制一个像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的TFT开关的信号输入情况,这样能够改变像素单元中画素的排列方式,从而改善Demux液晶显示屏显示不良的问题,改善制程不良导致的Demux液晶显示屏显示不良的现象;而且节省了制程优化所需要花费的制程成本,增加材料的利用率,又可达到忽视制程差异造成的不良,改善Demux液晶显示屏的显示品质,发展前景良好。

请参照图1至图5,本发明的实施例一为:

请参照图1,一种面板画素排列结构,包括两个以上的像素单元11、第一Demux走线、第二Demux走线、第三Demux走线、多条数据走线(例如图1中的D1-D6)和多条栅极走线(例如图1中的G1-G6),一个所述像素单元11配置两条栅极走线且位于两条栅极走线之间;

每个所述像素单元1包括从左至右依次排列的六列子像素对和七条数据走线,一列所述子像素对配置两条数据走线且位于两条数据走线之间,相邻的两列所述子像素对共用一条数据走线;

一个所述像素单元1中从左至右依次排列的第二条数据走线至第七条数据走线均分别连接一个TFT开关,一个所述像素单元1中从左至右依次排列的第二条数据走线和第三条数据走线所连接的TFT开关的栅极均分别与第一Demux走线电连接,一个所述像素单元1中从左至右依次排列的第四条数据走线和第五条数据走线所连接的TFT开关的栅极均分别与第二Demux走线电连接,一个所述像素单元1中从左至右依次排列的第六条数据走线和第七条数据走线所连接的TFT开关的栅极均分别与第三Demux走线电连接;

每个所述TFT开关的输入端分别连接有一条源极走线,一个所述像素单元1中从左至右依次排列的第二条数据走线、第四条数据走线和第六数据走线所连接的TFT开关共用一条源极走线,一个所述像素单元1中从左至右依次排列的第三条数据走线、第五条数据走线和第七数据走线所连接的TFT开关共用一条源极走线。

一个所述像素单元1中从左至右依次排列的第一条数据走线单独连接一条源极走线。

一个所述子像素对包括一个子像素,所述像素单元11中的所有子像素以R、G和B的方式依次阵列排布。

一个所述像素对中的一个子像素分别对应连接一条数据走线和栅极走线。

所述TFT开关的输出端与数据走线连接。

请参照图1,Demux S2和Demux S3是IC拉出来的Source Line,真正到面板内的Source Line以D1、D2等命名。

在纯色画面下或者灰阶画面下(这两种情况人眼较容易分辨得出来,实际上彩色图片也会有,只不过人眼在彩图画面下不容易发现亮暗竖线,因此以纯色画面和灰阶为例讲解),比如绿色画面下,T1这颗TFT控制第一列G画素(绿画素)亮,T2这颗TFT控制第二列G画素亮,但是由于制程上的不稳定性,T1和T2的开启电流会有差异,当T1的开启电流比较小,T2的开启电流比较大时,会发现第一列(G画素的第一列,不是子画素的第一列)的G画素较暗,而第二列的G画素较亮。

这样就会发现明明我们希望的是两条G-Source Line上的G画素要一样亮的,可实际是第一列G画素比第二列G画素更亮,由于人眼对绿色很敏感,不同的G-Source Line上的G画素亮度不一样,人眼都能够很好的发现。其他的G画素以此类推,都会因为制程上DemuxTFT开关的制程差异,每颗Demux TFT开关的开启电流不一致,导致Demux液晶显示屏会产生如图3所示的现象。其他纯色画面和灰阶画面产生亮暗竖线的原理和绿画面下产生亮暗竖线的原理是一样的。

在灰阶画面下,也会由于Demux TFT开关的开启电流不一致,使得每条SourceLine上的子画素显示亮度不一致,从而导致亮暗竖线的产生,影响了Demux液晶显示屏的显示品质。

在图1中,由于SW1/SW2/SW3开关顺序不同,对应的data mapping也不一样,共有36种SW开关顺序,这里仅列出一种SW的开关顺序和相应的data mapping。

图2为正确显示的纯色画面(G画面),显示无亮暗线,每条Source Line上的G画素充电都能够充饱和,G画素的显示亮度都一致,显示效果很好。

图3为异常显示的纯色画面(G画面),由于Demux TFT开关(如图1的T1/T2,DemuxTFT开关有很多颗,这里只是以控制G画素的Demux TFT开关为例)的开启电流不同,在图3中,较暗的竖线是Demux TFT开关的开启电流较低导致的,它使这一列暗线的G画素充电不能充到饱和,从而显示的亮度较低,人眼就能看到暗线;在图3中,较亮的竖线是因为DemuxTFT开关的开启电流较高,这样就能使这一列亮线的G画素充电能充到饱和,从而显示的亮度比Demux TFT开关的开启电流较低的G画素亮度较高,与旁边较低亮度的暗线相比,人眼就能看到的就是亮暗线;

请参照图1,本专利针对Demux液晶显示屏出现亮暗竖线的现象,特别提出的一种针对Demux液晶显示屏所设计的画素排列,其中S1和Sn不需要接到Demux-Source Line(如Demux S2/Demux S3),不需要Demux走线(SWn)来控制,直接从IC拉到Demux液晶显示屏内。对于Demux偶数条Source Line,如S2,S2与面内的D1/D3/D5相接;对于Demux奇数条SourceLine,如S3,S3与面内的D2/D4/D6相接。以绿画面为例,Demux液晶显示屏要显示绿画面,其中,S2和S3都会送Source电压,G1打开,从而驱动D1和D2上的G画素充电,G画素亮。如果控制D1的Demux TFT开关的开启电流较低,那么D1上的G画素充电会受到影响,G画素显示亮度未能达到理想的值(用×表示此画素显示亮度较低)。如果控制D2的Demux TFT开关的开启电流正常,则D2上的G画素充电能够充到饱和,则显示亮度可达到理想状态(用√表示此画素显示亮度正常)。这样发现D1和D2之间的G画素会出现一种规律,即上一个G画素显示亮度不理想(用×表示此画素显示亮度较低),下面一个G画素显示正常,下一个G画素显示亮度不理想,下一个G画素显示亮度又是理想的(用√表示此画素显示亮度正常),这样显示不好的G画素和显示正常的G画素反复上下相临出现,Demux液晶显示屏显示出的效果(如图5所示),显示亮度较好的G画素和显示亮度较差的G画素显示效果综合掉,加上人眼对这种高频率变化的亮度差别识别不出来,从而使得人眼无法看出有亮暗线的现象。

本方案优化后的画素搭配Demux结构显示,不仅仅是可以使Column的Source驱动实现了Dot的显示效果,而且可以避免Demux开关TFT因制程条件差异,带来的画素充电不一致而产生的亮暗线,优化了Demux的显示效果。

请参照图4,为优化画素排列的奇数条Source Line datamapping,Demux液晶显示屏内的最左和最右的Source Line直接和IC端的S1和Sn相接,不需要Demux走线(SW)来控制。对于Demux IC拉出来的偶数条的Demux Source Line(如S2),其与Demux液晶显示屏内的D2/D4/D6(如图1)通过Demux TFT开关和Demux S2相接,由Demux走线(SW)来控制IC输出到Demux液晶显示屏的data显示;对于奇数条的Demux Source Line(如S3),Demux液晶显示屏内的D3/D5/D7通过Demux TFT开关和Demux S3相接,由Demux走线(SW)来控制IC输出到Demux液晶显示屏的data显示。

结合图1的结构示意图的画素排列可知,当G1和SW1打开时,IC拉出来的奇数条上的Demux S3的data为G画素,当G1和SW2打开时,IC拉出来的奇数条上的Demux S3的data为R画素;当G1和SW3打开时,IC拉出来的奇数调上的Demux S3的data为B画素;

当G2和SW1打开时,IC拉出来的奇数调上的Demux S3的data为B画素;当G2和SW2打开时,IC拉出来的奇数调上的Demux S3的data为G画素,当G2和SW3打开时,IC拉出来的奇数条上的Demux S3的data为R画素;G3打开时,datamapping重复G1打开时的data传输,G4打开时,datamapping重复G2打开时的data传输。则G

请参照图5,为优化画素排列的偶数条Source Line datamapping。对于从IC拉出来的偶数的Demux-Source Line(S2)。当G1和SW1打开时,IC拉出来的偶数条上的Demux S2的data为R画素;当G1和SW2打开时,IC拉出来的偶数条上的Demux S2的data为B画素;当G1和SW3打开时,IC拉出来的偶数条上的Demux S2的data为G画素;当G2和SW1打开时,IC拉出来的偶数条上的Demux S2的data为G画素;当G1和SW2打开时,IC拉出来的偶数条上的DemuxS2的data为R画素;当G1和SW3打开时,IC拉出来的偶数条上的Demux S2的data为B画素;G3打开时,datamapping重复G1打开时的data传输,G4打开时,datamapping重复G2打开时的data传输。则G

请参照图1至图6,本发明的实施例二为:

请参照图6,一种面板画素排列结构的驱动方法,包括以下步骤:

步骤S1、在一个像素单元1中,控制两条栅极走线中的一条栅极走线开启;

步骤S2、在一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至一个像素单元1中从左至右依次排列的第二条数据走线和第三条数据走线所连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输一个像素单元1中从左至右依次排列的第四条数据走线和第五条数据走线所连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至一个像素单元1中从左至右依次排列的第六条数据走线和第七条数据走线所连接的像素对中;

步骤S3、控制两条栅极走线中的另一条栅极走线开启;

步骤S4、在另一条栅极走线开启期间,依次控制第一Demux走线、第二Demux走线和第三Demux走线开启;在第一Demux走线开启期间,控制源极走线将信号传输至一个像素单元1中从左至右依次排列的第二条数据走线和第三条数据走线所连接的像素对中;在第二Demux走线开启期间,控制源极走线将信号传输一个像素单元1中从左至右依次排列的第四条数据走线和第五条数据走线所连接的像素对中;在第三Demux走线开启期间,控制源极走线将信号传输至一个像素单元1中从左至右依次排列的第六条数据走线和第七条数据走线所连接的像素对中;

步骤S5、循环步骤S1-S4,驱动每个像素单元1。

请参照图1,Demux S2和Demux S3是IC拉出来的Source Line,真正到面板内的Source Line以D1、D2等命名。

在纯色画面下或者灰阶画面下(这两种情况人眼较容易分辨得出来,实际上彩色图片也会有,只不过人眼在彩图画面下不容易发现亮暗竖线,因此以纯色画面和灰阶为例讲解),比如绿色画面下,T1这颗TFT控制第一列G画素(绿画素)亮,T2这颗TFT控制第二列G画素亮,但是由于制程上的不稳定性,T1和T2的开启电流会有差异,当T1的开启电流比较小,T2的开启电流比较大时,会发现第一列(G画素的第一列,不是子画素的第一列)的G画素较暗,而第二列的G画素较亮。

这样就会发现明明我们希望的是两条G-Source Line上的G画素要一样亮的,可实际是第一列G画素比第二列G画素更亮,由于人眼对绿色很敏感,不同的G-Source Line上的G画素亮度不一样,人眼都能够很好的发现。其他的G画素以此类推,都会因为制程上DemuxTFT开关的制程差异,每颗Demux TFT开关的开启电流不一致,导致Demux液晶显示屏会产生如图3所示的现象。其他纯色画面和灰阶画面产生亮暗竖线的原理和绿画面下产生亮暗竖线的原理是一样的。

在灰阶画面下,也会由于Demux TFT开关的开启电流不一致,使得每条SourceLine上的子画素显示亮度不一致,从而导致亮暗竖线的产生,影响了Demux液晶显示屏的显示品质。

在图1中,由于SW1/SW2/SW3开关顺序不同,对应的data mapping也不一样,共有36种SW开关顺序,这里仅列出一种SW的开关顺序和相应的data mapping。

图2为正确显示的纯色画面(G画面),显示无亮暗线,每条Source Line上的G画素充电都能够充饱和,G画素的显示亮度都一致,显示效果很好。

图3为异常显示的纯色画面(G画面),由于Demux TFT开关(如图1的T1/T2,DemuxTFT开关有很多颗,这里只是以控制G画素的Demux TFT开关为例)的开启电流不同,在图3中,较暗的竖线是Demux TFT开关的开启电流较低导致的,它使这一列暗线的G画素充电不能充到饱和,从而显示的亮度较低,人眼就能看到暗线;在图3中,较亮的竖线是因为DemuxTFT开关的开启电流较高,这样就能使这一列亮线的G画素充电能充到饱和,从而显示的亮度比Demux TFT开关的开启电流较低的G画素亮度较高,与旁边较低亮度的暗线相比,人眼就能看到的就是亮暗线;

请参照图1,本专利针对Demux液晶显示屏出现亮暗竖线的现象,特别提出的一种针对Demux液晶显示屏所设计的画素排列,其中S1和Sn不需要接到Demux-Source Line(如Demux S2/Demux S3),不需要Demux走线(SWn)来控制,直接从IC拉到Demux液晶显示屏内。对于Demux偶数条Source Line,如S2,S2与面内的D1/D3/D5相接;对于Demux奇数条SourceLine,如S3,S3与面内的D2/D4/D6相接。以绿画面为例,Demux液晶显示屏要显示绿画面,其中,S2和S3都会送Source电压,G1打开,从而驱动D1和D2上的G画素充电,G画素亮。如果控制D1的Demux TFT开关的开启电流较低,那么D1上的G画素充电会受到影响,G画素显示亮度未能达到理想的值(用×表示此画素显示亮度较低)。如果控制D2的Demux TFT开关的开启电流正常,则D2上的G画素充电能够充到饱和,则显示亮度可达到理想状态(用√表示此画素显示亮度正常)。这样发现D1和D2之间的G画素会出现一种规律,即上一个G画素显示亮度不理想(用×表示此画素显示亮度较低),下面一个G画素显示正常,下一个G画素显示亮度不理想,下一个G画素显示亮度又是理想的(用√表示此画素显示亮度正常),这样显示不好的G画素和显示正常的G画素反复上下相临出现,Demux液晶显示屏显示出的效果(如图5所示),显示亮度较好的G画素和显示亮度较差的G画素显示效果综合掉,加上人眼对这种高频率变化的亮度差别识别不出来,从而使得人眼无法看出有亮暗线的现象。

本方案优化后的画素搭配Demux结构显示,不仅仅是可以使Column的Source驱动实现了Dot的显示效果,而且可以避免Demux开关TFT因制程条件差异,带来的画素充电不一致而产生的亮暗线,优化了Demux的显示效果。

请参照图4,为优化画素排列的奇数条Source Line datamapping,Demux液晶显示屏内的最左和最右的Source Line直接和IC端的S1和Sn相接,不需要Demux走线(SW)来控制。对于Demux IC拉出来的偶数条的Demux Source Line(如S2),其与Demux液晶显示屏内的D2/D4/D6(如图1)通过Demux TFT开关和Demux S2相接,由Demux走线(SW)来控制IC输出到Demux液晶显示屏的data显示;对于奇数条的Demux Source Line(如S3),Demux液晶显示屏内的D3/D5/D7通过Demux TFT开关和Demux S3相接,由Demux走线(SW)来控制IC输出到Demux液晶显示屏的data显示。

结合图1的结构示意图的画素排列可知,当G1和SW1打开时,IC拉出来的奇数条上的Demux S3的data为G画素,当G1和SW2打开时,IC拉出来的奇数条上的Demux S3的data为R画素;当G1和SW3打开时,IC拉出来的奇数调上的Demux S3的data为B画素;

当G2和SW1打开时,IC拉出来的奇数调上的Demux S3的data为B画素;当G2和SW2打开时,IC拉出来的奇数调上的Demux S3的data为G画素,当G2和SW3打开时,IC拉出来的奇数条上的Demux S3的data为R画素;G3打开时,datamapping重复G1打开时的data传输,G4打开时,datamapping重复G2打开时的data传输。则G

请参照图5,为优化画素排列的偶数条Source Line datamapping。对于从IC拉出来的偶数的Demux-Source Line(S2)。当G1和SW1打开时,IC拉出来的偶数条上的Demux S2的data为R画素;当G1和SW2打开时,IC拉出来的偶数条上的Demux S2的data为B画素;当G1和SW3打开时,IC拉出来的偶数条上的Demux S2的data为G画素;当G2和SW1打开时,IC拉出来的偶数条上的Demux S2的data为G画素;当G1和SW2打开时,IC拉出来的偶数条上的DemuxS2的data为R画素;当G1和SW3打开时,IC拉出来的偶数条上的Demux S2的data为B画素;G3打开时,datamapping重复G1打开时的data传输,G4打开时,datamapping重复G2打开时的data传输。则G

综上所述,本发明提供的一种面板画素排列结构及其驱动方法,通过设置第一Demux走线、第二Demux走线和第三Demux走线分别与像素单元中的TFT开关对应连接,第一Demux走线控制一个像素单元中从左至右依次排列的第二条数据走线和第三条数据走线所连接的TFT开关的信号输入情况,第二Demux走线控制一个像素单元中从左至右依次排列的第四条数据走线和第五条数据走线所连接的TFT开关的信号输入情况,第三Demux走线控制一个像素单元中从左至右依次排列的第六条数据走线和第七条数据走线所连接的TFT开关的信号输入情况,这样能够改变像素单元中画素的排列方式,从而改善Demux液晶显示屏显示不良的问题,改善制程不良导致的Demux液晶显示屏显示不良的现象;而且节省了制程优化所需要花费的制程成本,增加材料的利用率,又可达到忽视制程差异造成的不良,改善Demux液晶显示屏的显示品质,发展前景良好。

以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本发明的专利保护范围内。

- 一种面板画素排列结构及其驱动方法

- 一种数据信号极性反转驱动方法及液晶面板画面显示方法