半导体装置

文献发布时间:2023-06-19 12:00:51

本申请是如下发明专利申请的分案申请:

发明名称:半导体装置;申请日:2014年3月4日;申请号:201810442488.1。

技术领域

本发明涉及具有沟槽栅构造的半导体装置。

背景技术

一直以来,主要在马达控制系统、电力转换系统等各种功率电子学领域的系统中使用的半导体功率器备受瞩目。

作为这种半导体功率器件,提出例如具有沟槽栅构造的SiC半导体装置。

例如,专利文献1公开了一种MIS晶体管,包括:n

现有技术文献

专利文献

专利文献1:日本特开2012-178536号公报。

发明内容

发明要解决的课题

本发明的目的在于提供不依赖栅极沟槽的深度而能够在半导体层形成稳定的电场分布的半导体装置。

用于解决课题的方案

本发明的半导体装置包含:第1导电型的半导体层,具有单元部及配置在所述单元部的周围的外周部,在所述单元部的表面侧形成有栅极沟槽;以及栅极电极,隔着栅极绝缘膜埋入所述栅极沟槽,当导通时在所述栅极沟槽的侧部形成沟道,所述外周部具有配置在所述栅极沟槽的深度以上的深度位置的半导体表面,进一步包含耐压构造,其具有形成在所述外周部的所述半导体表面的第2导电型的半导体区域。

依据该结构,能够在与栅极沟槽的深度相等或该深度以上的深度位置形成耐压构造。由此,能够使从栅极沟槽的底部到半导体层的背面为止的该半导体层的厚度厚于构成耐压构造的从半导体区域到该背面为止的厚度。其结果,能够使耐压构造稳定地分担施加在半导体层的表面侧-背面侧间的电场。因而,不依赖于栅极沟槽的深度而能够在半导体层形成稳定的电场分布,因此能够良好地缓冲电场对栅极沟槽的底部的集中。

所述半导体装置也可以进一步包含表面绝缘膜,所述表面绝缘膜以横跨所述单元部及所述外周部的方式配置,并且形成为在所述单元部比所述外周部的部分更薄。

依据该结构,通过选择性地减薄单元部的表面绝缘膜,例如在表面绝缘膜形成有开口(接触孔等)的情况下,能够减小表面绝缘膜的表面与单元部的表面(器件表面)的阶梯差(凹凸)。由此,在向该开口埋入金属而在表面绝缘膜上形成表面金属层时,能够提高该表面金属层的平坦性。因此,例如在表面金属层接合引线的情况下,能够提高表面金属层和引线的密合性。其结果,能够良好地接合引线,因此能够提高引线接合部的可靠性。进而,表面金属层的平坦性优良,因此在引线接合时,能够防止超声波振动、压力对器件造成破坏,从而能够防止组装成品率的下降。

另一方面,外周部的表面绝缘膜的厚度能够与单元部的表面绝缘膜的厚度分开设计。因此,通过设计成不会影响外周部的电场分布的厚度,能够维持耐压特性。即,依据该结构,在改善表面金属层的平坦性之际,能够防止耐压特性的变动或该变动造成的耐压不良。

所述半导体装置也可以进一步包含:用于对所述栅极电极取得接触的栅极指(gate finger),所述栅极沟槽包含在所述栅极指的下方横切所述栅极指的线状的沟槽。

依据该结构,由于施加栅极电压时容易集中电场的沟槽的角部(例如,格子状沟槽的交叉部的角等)不配置在栅极指的下方,能够提高栅极绝缘膜的可靠性、耐压。

所述栅极沟槽也可以包含:当导通时所述沟道形成在其侧部的内侧沟槽;以及由该内侧沟槽的延长部构成并且相对于该内侧沟槽配置在外侧的外侧沟槽,所述半导体装置进一步包含形成在所述外侧沟槽的侧部及底部的第2导电型的层。

依据该结构,通过与半导体层的导电型不同的第2导电型的层,能够由该第2导电型的层与半导体层的结(pn结)产生耗尽层。而且,该耗尽层使等电位面远离外侧沟槽,因此能够缓冲施加在外侧沟槽的底部的电场。因而,能够防止外侧沟槽的底部的破坏。

所述半导体装置也可以进一步包含:用于对所述栅极电极取得接触的栅极指,所述栅极沟槽选择性地形成在所述栅极指的下方区域,所述半导体装置进一步包含第1导电型的高浓度层,所述高浓度层形成在该下方区域中未形成所述栅极沟槽的所述半导体层的半导体表面,并且含有杂质浓度高于所述半导体层。

依据该结构,能够使杂质浓度高的高浓度层的氧化速率快于比它低浓度的半导体层。因此,在利用热氧化来形成栅极绝缘膜的情况下,在栅极指的下方区域,能够选择性地形成在栅极沟槽的上部较厚的氧化膜。由此,在施加栅极电压时减弱施加在栅极沟槽的上部边缘的电场,从而能够防止栅极绝缘膜的绝缘破坏。

所述单元部也可以包含:以在所述半导体层的表面露出的方式配置的第1导电型的源极区域;以与所述源极区域相接的方式配置并且在导通时形成所述沟道的第2导电型的沟道区域;以与所述沟道区域相接的方式配置的第1导电型的漏极区域;在所述半导体层的所述表面选择性地形成在以包含所述源极区域的方式划分的源极部的第2沟槽;以及选择性地配置在所述第2沟槽的底部并且与所述沟道区域电连接的第2导电型的沟道接触区域。

所述单元部也可以包含:以在所述半导体层的表面露出的方式配置的第1导电型的源极区域;以与所述源极区域相接的方式配置并且在导通时形成所述沟道的第2导电型的沟道区域;以与所述沟道区域相接的方式配置的第1导电型的漏极区域;在所述半导体层的所述表面选择性地形成在以包含所述源极区域的方式划分的源极部的第2沟槽;埋入所述第2沟槽的沟槽埋入部;以及在所述源极部选择性地配置在比所述第2沟槽的底部高的位置并且与所述沟道区域电连接的第2导电型的沟道接触区域。

依据该结构,通过第2沟槽能够防止栅极沟槽的底部附近的等电位面的集中,并且能够缓和该底部附近的电位梯度。因此,能够缓冲电场对栅极沟槽的底部的集中。

另外,在第2沟槽埋入有沟槽埋入部,因此在半导体层的表面(器件表面),能够减小源极部与它以外的部分的阶梯差(凹凸)。由此,在该器件表面上形成表面金属层时,能够提高表面金属层的平坦性。因此,例如在表面金属层接合引线的情况下,能够提高表面金属层和引线的密合性。其结果,能够很好地接合引线,因此能够提高引线接合部的可靠性。进而,由于表面金属层的平坦性优良,所以在引线接合时,能够防止超声波振动、压力对器件造成破坏,从而能够防止组装成品率的下降。

而且,沟道接触区域配置在比第2沟槽的底部高的位置,因此,即便形成有第2沟槽,也能经由该沟道接触区域可靠地取得对沟道区域的接触。即,在改善表面金属层的平坦性之际,能够防止对栅极耐压、沟道区域的接触性等的器件性能的下降。

所述沟槽埋入部也可以由形成在所述第2沟槽的内表面的绝缘膜和埋入所述绝缘膜的内侧的多晶硅层构成。

依据该结构,例如,在半导体层的表面形成由SiO

所述绝缘膜也可以由SiO

依据该结构,例如,以同一个工序形成栅极绝缘膜和第2沟槽内的绝缘膜,从而能够用上面例示的材料构成栅极绝缘膜。在该情况下,如果用AlON、Al

所述绝缘膜也可以具有包含氮(N)的SiO

依据该结构,例如,通过以同一个工序形成栅极绝缘膜和第2沟槽内的绝缘膜,能够用具有包含氮(N)的SiO

所述绝缘膜也可以形成为在所述第2沟槽的所述底部比在所述第2沟槽的侧部的部分厚。

依据该结构,例如,通过以同一个工序形成栅极绝缘膜和第2沟槽内的绝缘膜,关于栅极绝缘膜,也能够例如在栅极沟槽的底部比在栅极沟槽的侧部的部分厚。由此,能够提高栅极沟槽的底部的耐压。

所述多晶硅层也可以由n

依据该结构,例如,通过以同一个工序形成栅极电极和第2沟槽内的多晶硅层,能够用n

所述沟槽埋入部也可以由回填所述第2沟槽的绝缘层构成。

依据该结构,由于用绝缘层填满第2沟槽内,所以能够防止或降低经由第2沟槽而流过的泄漏电流。

所述绝缘层也可以由SiO

依据该结构,SiO

所述沟槽埋入部也可以由回填所述第2沟槽的多晶硅层构成。

依据该结构,例如,在半导体层的表面形成由SiO

所述多晶硅层也可以由p

依据该结构,例如,在沟道区域及沟道接触区域为p型的情况下,能够利用p

本发明的半导体装置也可以进一步包含:以与所述沟道区域及所述沟道接触区域连续的方式形成在所述第2沟槽的所述底部及侧部的第2导电型的层。

依据该结构,通过与半导体层的导电型不同的第2导电型的层,能够由该第2导电型的层与半导体层的结(pn结)产生耗尽层。而且,该耗尽层使等电位面远离栅极沟槽,因此能够进一步缓冲施加在栅极沟槽的底部的电场。

所述栅极电极也可以包含:形成在所述栅极沟槽的内表面的由多晶硅构成的基底膜;以及埋入所述基底膜的内侧的包含Mo、W、Al、Pt、Ni及Ti的至少一种的埋入金属。

依据该结构,通过埋入金属能够使栅极电阻比较低,因此能够使晶体管的开关速度高速化。

所述半导体装置也可以进一步包含:配置在所述半导体层的表面侧的由包含铜(Cu)的金属构成的表面金属层。在该情况下,在该情况下,所述表面金属层也可以包含Al-Cu类合金。

依据该结构,能够降低表面金属层的片电阻,因此能够提高电流密度。

所述单元部中,多个单位单元既可以被所述栅极沟槽以格子状划分,也可以被所述栅极沟槽以条纹状划分。

所述半导体层也可以由SiC、GaN或金刚石构成。

附图说明

图1是本发明的第1实施方式所涉及的半导体装置的示意平面图。

图2是图1的主要部分放大图,并透视一部分而示出。

图3示出图2的III-III截面上的半导体装置的截面构造。

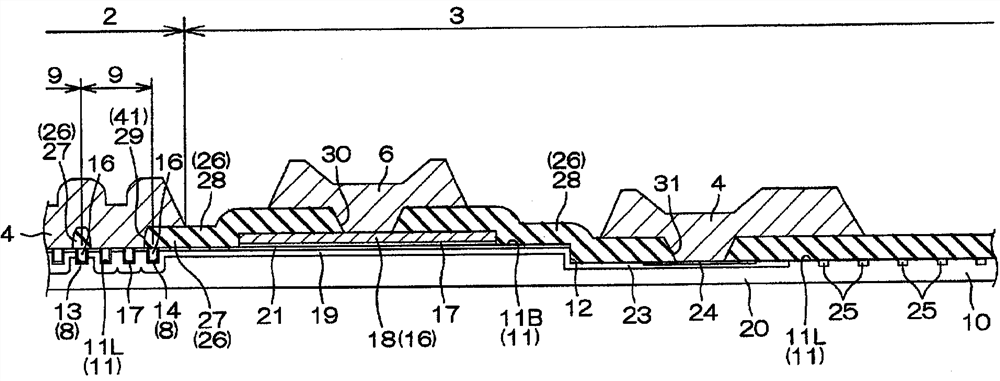

图4示出图2的IV-IV截面上的半导体装置的截面构造。

图5示出图2的V-V截面上的半导体装置的截面构造。

图6是示出图2的VI-VI截面上的半导体装置的截面构造。

图7是放大示出图3的单元部的图。

图8是示出所述单元部的第1变形例的图。

图9是示出所述单元部的第2变形例的图。

图10是示出所述单元部的第3变形例的图。

图11是示出所述单元部的第4变形例的图。

图12是示出所述单元部的第5变形例的图。

图13是本发明的第2实施方式所涉及的半导体装置的示意截面图。

图14是本发明的第2实施方式所涉及的半导体装置的示意截面图。

图15是参考方式所涉及的半导体装置的示意截面图。

图16是参考方式所涉及的半导体装置的示意截面图。

图17是本发明的第3实施方式所涉及的半导体装置的示意截面图。

图18是本发明的第3实施方式所涉及的半导体装置的示意截面图。

图19是本发明的第4实施方式所涉及的半导体装置的示意截面图。

图20是本发明的第4实施方式所涉及的半导体装置的示意截面图。

图21是本发明的第5实施方式所涉及的半导体装置的示意截面图。

具体实施方式

<第1实施方式>

以下,参照附图详细说明本发明的实施方式。

图1是本发明的第1实施方式所涉及的半导体装置的示意平面图。

半导体装置1包含采用了SiC的MISFET(Metal Insulator Field EffectTransistor:金属绝缘体场效应晶体管)。半导体装置1的外形例如如图1所示,是俯视正方形的芯片状。关于芯片状的半导体装置1的尺寸,图1的纸面中的上下左右方向的长度分别为数mm左右。半导体装置1中,设定有单元部2和配置在单元部2的周围的外周部3。在该实施方式中,外周部3以包围单元部2的方式设定为环状,如果相对于单元部2处于芯片的外侧的区域,则无需特别为环状。

半导体装置1包含源极焊盘4、栅极焊盘5及栅极指6。

源极焊盘4配置在单元部2的上方区域。该实施方式中,源极焊盘4以覆盖单元部2的大致整个区域的方式例如以俯视正方形状形成。在源极焊盘4的周缘部,沿着外周部3形成有包围源极焊盘4的中央区域的除去区域7(图1的交叉影线部分)。除去区域7的一部分选择性地向源极焊盘4的中央区域凹陷。凹坑的整体配置在单元部2的上方区域,在此设置有栅极焊盘5。

栅极指6相对于单元部2与外周部3的边界在外周部3侧的位置中,从栅极焊盘5沿着外周部3并遍及除去区域7整体而延伸。该实施方式中,一对栅极指6相对于栅极焊盘5以对称的形状形成。而且,该实施方式中,例如,沿着除去区域7的相对于栅极指6为内侧的部分,设定有前述的单元部2与外周部3的边界(与图2的边界L相同)。

单元部2中,进一步形成有栅极沟槽8。该实施方式中,栅极沟槽8以避开栅极焊盘5的下方区域的方式选择性地形成在源极焊盘4的下方区域。该区域中,栅极沟槽8以划分出多个单位单元9的方式形成。栅极沟槽8的图案如图1所示,既可为格子状,也可为条纹状。由此,单元部2中,多个单位单元9会以矩阵状(行列状)或条纹状(直线状)有规则地排列。此外,虽然未图示,但是单位单元9的图案也可为蜂窝状等的其他形状。

接着,说明半导体装置1的单元部2及外周部3的内部构造。

图2是图1的主要部分放大图,并将一部分透视而示出。具体而言,以实线示出源极焊盘4及栅极指6的下方区域的构造,并以虚线示出源极焊盘4及栅极指6。图3示出图2的III-III截面中的半导体装置的截面构造。图4示出图2的IV-IV截面中的半导体装置的截面构造。图5示出图2的V-V截面中的半导体装置的截面构造。图6示出图2的VI-VI截面中的半导体装置的截面构造。

半导体装置1包含由n

n

该实施方式中,栅极沟槽8包含:用作为MISFET的栅极的内侧沟槽13;相对于内侧沟槽13配置在外侧的外侧沟槽14;以及从外侧沟槽向外周部3引出并成为对栅极电极16(后述)的接触部的接触沟槽15。这些沟槽13~15以互相连通的方式整体地形成。

如图2所示,内侧沟槽13以划分出多个单位单元9的方式使多个线状的沟槽互相交叉而以格子状形成。内侧沟槽13的各线的末端部因外侧沟槽14而互相相连。即,外侧沟槽14以包围内侧沟槽13的方式形成,并且横跨在内侧沟槽13的互相相邻的线的末端部间。

接触沟槽15由内侧沟槽13的各线的延长部构成并以线状形成,沿着单元部2与外周部3的边界L彼此隔开间隔而配置多个。此外,如图2所示,接触沟槽15无需在内侧沟槽13的每一条线上设置,例如,也可以每隔一条内侧沟槽13的线而设置。该线状的接触沟槽15在栅极指6的下方区域以横切栅极指6的方式形成。该实施方式中,接触沟槽15的末端部比栅极指6配置在外侧。即,接触沟槽15的末端部比栅极指6向外侧伸出。

而且,对栅极沟槽8埋入有例如由多晶硅构成的栅极电极16,并且栅极绝缘膜17介于该栅极电极16与n

例如如图3及图4所示,栅极电极16在从栅极指6的下方区域分离的位置形成的内侧沟槽13及外侧沟槽14中,埋入到基极表面11B。由此,栅极电极16也以格子状形成,各单位单元9的上表面不被栅极电极16覆盖而露出。另一方面,在栅极指6的下方区域形成的接触沟槽15中,具有从接触沟槽15的开口端以选择性地覆盖基极表面11B的方式形成的遮盖部18。遮盖部18在该实施方式中,如图2所示,以横切线状的接触沟槽15的方式沿着栅极指6而形成。如图5及图6所示,在该遮盖部18与n

单元部2中,栅极电极16控制单位单元9中的反转层(沟道)的形成。即,该半导体装置1具有所谓的沟槽栅型构造的MISFET。

该实施方式中,低阶部12以遍及外周部3的全周而形成,由此,包围单元部2。该低阶部12以栅极沟槽8的深度以上的深度形成。因此,外周部3中,低阶部12的底面(低表面11L)配置在栅极沟槽8的底面(低表面11L)以上的深度位置。其深度例如以基极表面11B为基准,相对于栅极沟槽8的深度0.7μm~3μm,为0.7μm~5μm。

而且,在这样具有高低差的半导体表面11,选择性地形成有n型及p型的杂质区域。

具体而言,在n

p型阱19中,如图3、图5及图6所示,在栅极指6的下方区域形成有n

在n

另外,在n

另外,在低阶部12中p型层23的外侧形成有作为本发明的耐压构造的一个例子的p型保护环25(例如,浓度为1×10

在n

在表面绝缘膜26形成有对于n

在表面绝缘膜26上形成有源极焊盘4及栅极指6。

源极焊盘4经由各接触孔29、31与全部的单位单元9的p

栅极指6经由接触孔30与栅极电极16(遮盖部18)连接。另外,作为栅极指6及栅极焊盘5的材料,与源极焊盘4同样,能够使用包含铜(Cu)的金属,更优选使用包含Al-Cu类合金的金属。通过使用与源极焊盘4相同的材料,能够同时形成源极焊盘4、栅极焊盘5及栅极指6。

接着,更详细地说明单元部2的构造。图7是放大示出图3的单元部2的图。

在单元部2中,如前所述,各自进行晶体管动作的多个单位单元9被栅极沟槽8(内侧沟槽13及外侧沟槽14)划分为格子状。各单位单元9包含环状的n

具体而言,在单元部2中在p型阱19的表面部形成有n

而且,栅极沟槽8及源极沟槽33贯通n

通过栅极沟槽8及源极沟槽33,各单位单元9被分离为被源极沟槽33包围的柱状部36和配置在源极沟槽33与栅极沟槽8之间并且因源极沟槽33而与柱状部36隔开间隔的环状部37。该实施方式中,环状部37的宽度W

在柱状部36的顶部,以在n

在环状部37从基极表面11B侧依次形成有n

另外,在n

另外,p型层38经由外侧沟槽14的底部也以横跨外侧沟槽14的外周缘的方式形成,在该外周缘中,与向外周部3延伸的p型阱19连接。另外,如图2及图4所示,p型层38也可以在内侧沟槽13中仅形成在构成内侧沟槽13的线的交叉部。此外,内侧沟槽13的交叉部在各单位单元9的每个角部不会在导通时形成沟道,或者即便形成流过该沟道的电流也是微量的。因此,以在该交叉部与p型沟道区域35连接的方式形成p型层38,也几乎不会对器件的性能产生影响。

另外,p型层38与p型层22同样,形成为在栅极沟槽8及源极沟槽33的底部比在源极沟槽33的侧部的部分还厚。但是,在柱状部36中,源极沟槽33的侧部被源极沟槽33包围,离子一样从其周围注入。因此,以充满p

另外,p型层38在该实施方式中,以在内侧沟槽13的交叉部及外侧沟槽14以外的部分不与栅极沟槽8相接的方式(与栅极沟槽8隔开间隔),遍及被栅极沟槽8包围的环状部37的全周而形成。由此,在各单位单元9中n

栅极沟槽8在该实施方式中,形成为具有侧面及底面的截面视大致U字状。在栅极沟槽8的内表面(侧面及底面),以使其一个表面及另一表面沿着栅极沟槽8的内表面的方式形成有栅极绝缘膜17。

栅极绝缘膜17形成为在栅极沟槽8的底部比在栅极沟槽8的侧部的部分还厚。如该实施方式那样在截面视大致U字状的栅极沟槽8中,栅极绝缘膜17的相对厚的部分为与栅极沟槽8的底面相接的部分,而相对薄的部分为与栅极沟槽8的侧面相接的部分。通过加厚容易引起电场集中的栅极沟槽8的底部的绝缘膜,能够提高栅极沟槽8的底部的耐压。此外,根据栅极沟槽8的形状有无法明确判别侧面和底面的情况,但是在此情况下,使与栅极沟槽8的与深度方向交叉的方向的面相接的栅极绝缘膜17相对厚即可。

而且,栅极绝缘膜17的内侧被栅极电极16回填。该实施方式中,栅极电极16以使其上表面与n

源极沟槽33也同样,该实施方式中,以具有侧面及底面的截面视大致U字状形成。在源极沟槽33的内表面(侧面及底面),以使其一个表面及另一表面沿着源极沟槽33的内表面的方式形成有源极沟槽绝缘膜39。

源极沟槽绝缘膜39形成为在源极沟槽33的底部比在源极沟槽33的侧部的部分还厚。此外,因源极沟槽33的形状而有不能明确判别侧面和底面的情况,但是在此情况下,只要与源极沟槽33的与深度方向交叉的方向的面相接的源极沟槽绝缘膜39相对厚即可。而且,源极沟槽绝缘膜39的内侧被沟槽埋入层40回填。该实施方式中,沟槽埋入层40以使其上表面与n

该实施方式中,栅极绝缘膜17和源极沟槽绝缘膜39由相同的材料构成,栅极电极16和沟槽埋入层40由相同的材料构成。

例如,作为栅极绝缘膜17及源极沟槽绝缘膜39的材料,能够使用SiO

作为栅极电极16及沟槽埋入层40的材料,能够使用多晶硅,更优选使用n

此外,栅极绝缘膜17及源极沟槽绝缘膜39也可以互相用不同的材料构成。栅极电极16及沟槽埋入层40也同样,也可以互相用不同的材料构成。

形成在表面绝缘膜26的接触孔29,相对于n

接着,说明用图1~图7说明的半导体装置1的制造方法。

在制造半导体装置1时,通过CVD法、LPE法、MBE法等的外延生长法,在SiC衬底(未图示)的表面一边掺杂n型杂质一边生长SiC结晶。由此,在SiC衬底上形成n

接着,从n

接着,从n

接着,利用在应该形成栅极沟槽8、源极沟槽33及低阶部12的区域具有开口的掩模来选择性地蚀刻n

此外,在使外周部3的低表面11L位于比栅极沟槽8的深度更深的位置的情况下,进行上述蚀刻之后,进一步选择性地蚀刻低阶部12即可。

接着,从n

接着,从n

接着,例如,在1400℃~2000℃对n

接着,例如通过热氧化同时形成栅极绝缘膜17及源极沟槽绝缘膜39。此外,在用高介电常数(High-k)膜构成栅极绝缘膜17及源极沟槽绝缘膜39的情况下,用CVD法沉积膜材料即可。

接着,例如通过CVD法,掺杂了n型杂质的多晶硅材料从n

接着,例如通过CVD法,SiO

接着,通过选择性地蚀刻表面绝缘膜26,同时形成接触孔29~31。

接着,例如通过溅射法,金属材料从n

如以上那样,依据该半导体装置1,形成有p型层23及p型保护环25的半导体表面11成为与栅极沟槽8的深度相等或其以上的深度位置的低表面11L。由此,能够使从栅极沟槽8的底部到n

另外,如图2所示,虽然在栅极指6的下方区域形成有栅极沟槽8,但也只是线状的接触沟槽15以横切栅极指6的方式形成,而且接触沟槽15的末端部比栅极指6配置在外侧。即,由于在施加栅极电压时容易集中电场的沟槽的角部(例如,在内侧沟槽13的交叉部的角等)不会配置在栅极指6的下方,所以能够提高栅极绝缘膜17的可靠性、耐压。

另外,如图7所示,p型层38经由外侧沟槽14的底部还横跨外侧沟槽14的外周缘的方式形成。由此,能够由p型层38与n

另外,如图5及图6所示,在栅极指6的下方区域中,在n

另外,如图7所示,隔着源极沟槽绝缘膜39向源极沟槽33埋入沟槽埋入层40。因此,在n

另一方面,通过源极沟槽33,能够防止栅极沟槽8的底部附近的等电位面的集中,从而能够缓和该底部附近的电位梯度。因此,能够缓冲电场对栅极沟槽8的底部的集中。进而,p

进而,该实施方式中,由于在源极沟槽33的周围形成p型层38,所以能够由该p型层38与n

另外,该实施方式中,采用比Si器件难以引起闭锁的SiC器件,因此能够将p

另外,由于源极沟槽绝缘膜39配置在沟槽埋入层40的外侧,所以能够防止在n

另外,如果埋入源极沟槽33的沟槽埋入层40为多晶硅,则在由SiO

另外,由于同时形成源极沟槽33和栅极沟槽8,所以不会增加制造工序,而能够无对准的偏差且简单地形成源极沟槽33。进而,如果源极沟槽33和栅极沟槽8的宽度相同,则能够使源极沟槽33的蚀刻速率与栅极沟槽8相同,因此能够稳定地控制用于形成源极沟槽33的蚀刻。

接着,参照图8~图12,对单元部2的变形例进行说明。

图8~图12是示出单元部2的第1~第5变形例的图。在图8~图12中,对于与前述的图7所示的各部分对应的部分标注相同的参照标号而加以示出。

在图7的方式中,埋入源极沟槽33的沟槽埋入部,由源极沟槽绝缘膜39及沟槽埋入层40(多晶硅层)构成,但是如图8所示,也可以仅由回填源极沟槽33的绝缘层42构成。

作为绝缘层42的材料,能够使用SiO

图8所示的方式的半导体装置的制造工序与上面说明的工序实质上相同。但是,在形成栅极电极16及沟槽埋入层40之后,选择性地蚀刻除去沟槽埋入层40,使源极沟槽33出现空洞。而且通过在n

依据该结构,由于源极沟槽33被绝缘层42充满,所以能够有效地防止在n

另外,如果绝缘层42为包含磷或硼的SiO

另外,如图9所示,埋入源极沟槽33的沟槽埋入部也可以仅由回填源极沟槽33的多晶硅层43构成。作为多晶硅层43的材料,优选使用p

图8所示的方式的半导体装置的制造工序与上面说明的工序实质上相同。但是,在形成栅极绝缘膜17及源极沟槽绝缘膜39之后,选择性地蚀刻除去源极沟槽绝缘膜39,使源极沟槽33出现空洞。而且,多晶硅从n

依据该结构,由于多晶硅层43埋入源极沟槽33,所以在由SiO

另外,如果多晶硅层43为p

另外,图7的方式中,源极沟槽33在被环状的n

另外,图7的方式中,栅极电极16是回填栅极绝缘膜17的内侧的仅由多晶硅构成的层,但是如图11所示,也可以由在栅极绝缘膜17上以使一个表面及另一表面沿着栅极沟槽8的内表面的方式形成的由多晶硅构成的基底膜46、和埋入基底膜46的内侧的包含Mo、W、Al、Pt、Ni及Ti的至少一种的埋入金属47构成。在该情况下,源极沟槽33内的沟槽埋入部也同样,也可以由在源极沟槽绝缘膜39上以使一个表面及另一表面沿着源极沟槽33的内表面的方式形成的由多晶硅构成的基底膜48、和埋入基底膜48的内侧的由与埋入金属47相同的材料构成的埋入金属49构成。

依据该结构,通过使用埋入金属47的金属栅极,能够使栅极电阻比多晶硅栅极相对较低,因此能够使晶体管的开关速度高速化。

另外,在图7的单元部2形成有沟槽栅型构造的MISFET,但是如图12所示,在单元部2形成平面型构造的MISFET也可。此外,图12的构造并不是说明记载于权利要求书的本发明的实施方式,而是示出本发明的参考方式。

即,在图12所示的方式中,在单元部2以与各单位单元9对应的方式矩阵状(行列状)排列有p型阱19。在各p型阱19的表面部,以在基极表面11B露出的方式形成有环状的n

<第2实施方式>

图13及图14是本发明的第2实施方式所涉及的半导体装置的示意截面图,分别示出与图3及图4对应的截面构造。在图13及图14中,对于与前述的图3及图4所示的各部分对应的部分标注相同的参照标号并加以示出。

在前述的第1实施方式中,由低阶部12形成的基极表面11B和低表面11L的边界,设定在比针对横跨单元部2及外周部3的p型阱19的源极焊盘4的接触位置更靠内侧,但是如图13及图14所示,也可以设定在外侧。在该情况下,p

依据该结构,能够在基极表面11B形成p

<参考方式>

图15及图16是本发明的参考方式所涉及的半导体装置的示意截面图,分别示出与图3及图4对应的截面构造。在图15及图16中,对于与前述的图3及图4所示的各部分对应的部分标注相同的参照标号并加以示出。

前述的第1实施方式中,表面绝缘膜26使单元部2上的内侧部分27形成为与外周部3上的外侧部分28相同的厚度,但是如图15及图16所示,也可以形成为使内侧部分27薄于外侧部分28。该参考方式中,内侧部分27的厚度为5000Å以下,外侧部分26的厚度为5500Å~20000Å左右。这样的膜厚差,能够通过例如在n

另外,该参考方式中,不在外周部3形成低阶部21,外周部3具有与单元部2的基极表面11B相同的高度位置的半导体表面11。

依据该参考方式,通过选择性地减薄单元部2的表面绝缘膜26(内侧部分27),能够减小接触孔29内的源极部41中的半导体表面11(器件表面)与表面绝缘膜26的表面的阶梯差(凹凸)。由此,在向接触孔29埋入源极焊盘4而在表面绝缘膜26上形成源极焊盘4时,能够进一步提高源极焊盘4的平坦性。

另一方面,外周部3的表面绝缘膜26(外侧部分28)的厚度能够与内侧部分27的厚度分开设计。因此,通过设计成为不会影响外周部3的电场分布的厚度,能够维持耐压特性。即,依据该结构,在改善源极焊盘4的平坦性时,能够防止耐压特性的变动或该变动造成的耐压不良。

<第3实施方式>

图17及图18是本发明的第3实施方式所涉及的半导体装置的示意截面图,分别示出与图3及图4对应的截面构造。在图17及图18中,对于与前述的图3及图4所示的各部分对应的部分标注相同的参照标号并加以示出。

图17及图18的构造是对第1实施方式的构造结合了前述的参考方式的表面绝缘膜26的膜厚差的结构的例子。依据该结构,能够同时实现第1实施方式及参考方式的效果。

<第4实施方式>

图19及图20是本发明的第4参考方式所涉及的半导体装置的示意截面图,分别示出与图3及图4对应的截面构造。在图19及图20中,对于与前述的图3及图4所示的各部分对应的部分标注相同的参照标号并加以示出。

图19及图20的构造是对第2实施方式的构造结合了前述的参考方式的表面绝缘膜26的膜厚差的结构的例子。依据该结构,能够同时实现第1实施方式、第2实施方式及参考方式的效果。

<第5实施方式>

图21是本发明的第5实施方式所涉及的半导体装置的示意截面图,示出与图3对应的截面构造。在图21中,对于与前述的图3所示的各部分对应的部分标注相同的参照标号并加以示出。

前述的第1实施方式中,外周部3的耐压构造如p型层23及p型保护环25那样仅由p型的半导体区域构成,但是如图21所示,也可以为包含形成在低表面11L的沟槽和形成在该沟槽的底部的p型的半导体区域的构成。在该情况下,在沟槽内也可以隔着绝缘膜埋入导电材料。该实施方式中,形成有保护环55,其包含:形成在低表面11L并包围单元部2的环状的沟槽53;形成在沟槽53的底部及侧部并且其内部区域与沟槽53相接的p型层54。在沟槽53隔着沟槽绝缘膜56埋入有多晶硅层57。

通过该结构,也能实现与第1实施方式同样的效果。

以上,说明了本发明的实施方式,但是本发明也能以其他方式实施。

例如,也可以采用反转半导体装置1的各半导体部分的导电型的结构。例如,在半导体装置1中,p型的部分为n型,n型的部分为p型也可。

另外,在半导体装置1中,构成半导体层的层不限于由SiC构成的n

另外,各单位单元9不限于俯视正方形(四方形状),例如,俯视三角形、俯视五角形、俯视六角形等的其他俯视多边形状也可。

本发明的半导体装置能够装入构成用于驱动例如作为电动汽车(包括混合动力车)、电车、产业用机器人等的动力源而利用的电动马达的驱动电路的逆变器电路所使用的功率模块。另外,也能装入用于转换太阳能电池、风力发电机其他的发电装置(特别是自家发电装置)产生的电力以与商用电源的电力匹配的逆变器电路的功率模块。

另外,由前述的实施方式的公开所掌握的特征在不同的实施方式间也能互相组合。另外,在各实施方式中出现的构成要素在本发明的范围内能够进行组合。

本发明的实施方式只不过是为明确本发明的技术的内容而利用的具体例,不应当限定于这些具体例而解释本发明,本发明的精神及范围仅由附加的权利要求书限定。

本申请对应于2013年3月5日向日本国专利厅提出的特愿2013-43406号,在此该申请的全部公开内容通过引用而进行结合。

标号说明

1 半导体装置;2 单元部;3 外周部;4 源极焊盘;5 栅极焊盘;6 栅极指;7除去区域;8 栅极沟槽;9 单位单元;10 n

- 晶体、结晶性氧化物半导体、包含结晶性氧化物半导体的半导体膜、包含晶体和/或半导体膜的半导体装置以及包含半导体装置的系统

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置