半导体装置及半导体装置的制造方法

文献发布时间:2023-06-19 12:02:28

技术领域

本公开涉及一种所谓的Fan-Out型(扇出型)的半导体装置。

背景技术

随着近年来的电子设备的小型化,用于该电子设备的半导体装置的小型化正在推进。受到这样的动向,已知一种所谓的Fan-Out型的半导体装置。该半导体装置具备具有多个电极的半导体元件、与半导体元件相接的绝缘层、配置于绝缘层且与多个电极相连的多个配线、以及与绝缘层相接且覆盖上述半导体元件的一部分的密封树脂。沿厚度方向观察,多个配线包括位于比半导体元件靠外方的部分。由此,具有既实现半导体装置的小型化,又能够灵活对应安装有该半导体装置的配线基板的配线图案的形状的优点。

在专利文献1中公开了Fan-Out型的半导体装置的制造方法的一例。该制造方法包括:将具有多个电极的半导体元件埋入密封树脂(专利文献1中的固化体)的工序;形成与半导体元件及密封树脂双方相接的绝缘层(专利文献1为缓冲覆膜)的工序;以及形成与多个电极相连的多个配线的工序。在将半导体元件埋入密封树脂的工序中,使多个电极从密封树脂露出。在形成绝缘层的工序中,通过使用了掩模的光刻构图在绝缘层形成多个开口,以使多个电极露出。在形成多个配线的工序中,在绝缘层的多个开口和绝缘层上形成镀敷层。

在向密封树脂埋入半导体元件的工序时,由于密封树脂固化收缩,因此半导体元件产生位移。若在该状态下在绝缘层形成多个开口,则多个开口和多个电极的位置产生偏差。若在该情况下形成多个配线,则产生多个电极与多个配线的接合部处的错位。因此,为了进一步提高半导体装置的可靠性,期望抑制该偏差。

现有技术文献

专利文献

专利文献1:日本特开2016-89081号公报

发明内容

发明所要解决的课题

鉴于上述的情况,本公开的课题在于提供一种能够抑制半导体元件的多个电极和多个配线的接合部处的错位的半导体装置及其制造方法。

用于解决课题的方案

根据本公开的第一方面提供的半导体装置具备:第一绝缘层,其具有在厚度方向上彼此朝向相反侧的第一面及第二面;多个第一配线,其具有至少一部分埋入上述第一绝缘层的第一埋入部及配置于上述第二面且与上述第一埋入部相连的第一再配线部;半导体元件,其具有设于上述第一面的附近且与上述多个第一配线的上述第一埋入部的至少一部分相连的多个电极,并且与上述第一面相接;以及密封树脂,其与上述第一面相接,且覆盖上述半导体元件的一部分,沿上述厚度方向观察,上述多个第一配线的上述第一再配线部包括位于比上述半导体元件靠外方的部分,上述第一绝缘层具有从上述第二面朝向上述厚度方向凹陷的多个第一槽,上述多个第一配线的上述第一再配线部与上述多个第一槽相接。

根据本公开的第二方面提供的半导体装置的制造方法具备:将具有设于厚度方向的任一侧的多个电极的半导体元件以使上述多个电极露出的方式埋入密封树脂的工序;

形成层叠于上述密封树脂且覆盖上述多个电极的绝缘层的工序;以及形成多个配线的工序,该多个配线具有埋入上述绝缘层且与上述多个电极的任一个相连的埋入部及配置于上述绝缘层上且与上述埋入部相连的再配线部,上述绝缘层由包含热固化性的合成树脂及添加剂的材料构成,该添加剂含有组成上述多个配线的一部分的金属元素,形成上述多个配线的工序包括如下工序:一边对上述多个电极的位置进行图像识别,一边利用激光在上述绝缘层形成使上述多个电极露出的多个孔和从上述绝缘层的表面凹陷且与上述多个孔相连的多个槽,由此使覆盖规定上述多个孔的每一个的壁面和上述多个槽的基底层析出;以及形成覆盖上述基底层的镀敷层。

通过以下基于附图进行的详细的说明,本公开的其它特征及优点将更明了。

附图说明

图1是本公开的第一实施方式的半导体装置的俯视图,透过了密封树脂。

图2是相对于图1进一步透过了半导体元件的俯视图。

图3是图1所示的半导体装置的仰视图。

图4是对应于图3的仰视图,透过了保护层及多个端子。

图5是沿着图1的V-V线的剖视图。

图6是沿着图1的VI-VI线的剖视图。

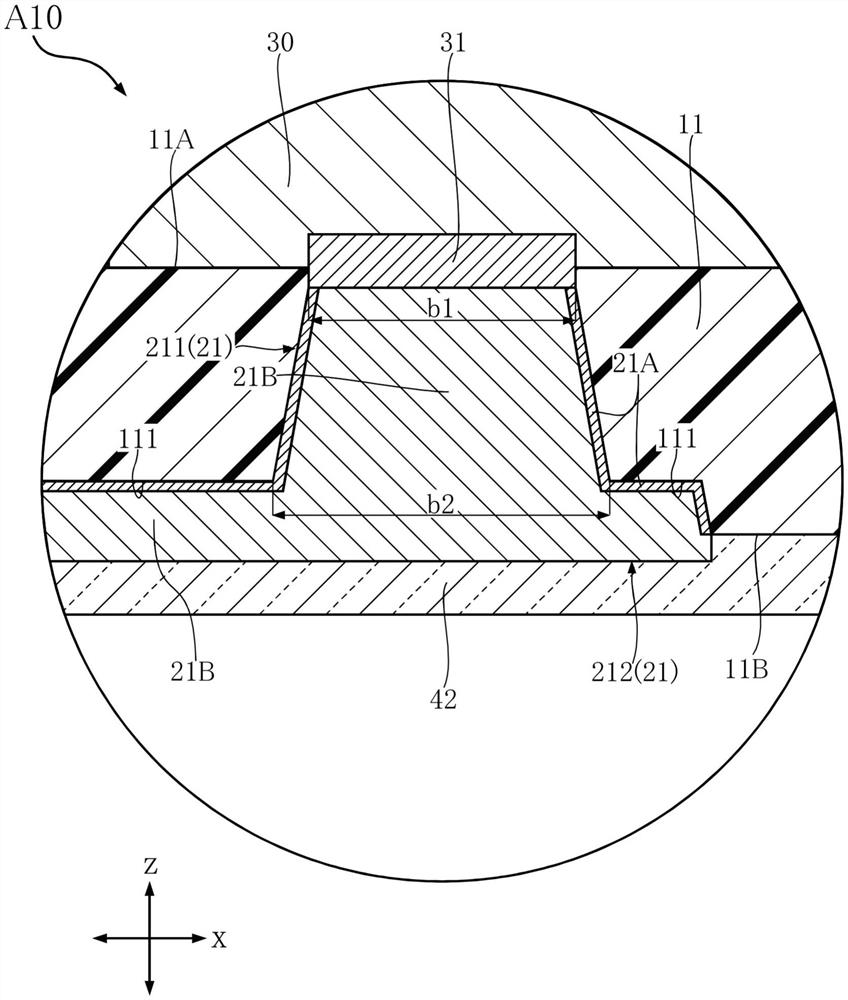

图7是图5的局部放大图。

图8是图5的局部放大图。

图9是沿着图1的IX-IX线的局部放大剖视图。

图10是对图1所示的半导体装置的制造工序进行说明的剖视图。

图11是对图1所示的半导体装置的制造工序进行说明的剖视图。

图12是对图1所示的半导体装置的制造工序进行说明的剖视图。

图13是图12的局部放大图。

图14是对图1所示的半导体装置的制造工序进行说明的剖视图。

图15是图14的局部放大图。

图16是对图1所示的半导体装置的制造工序进行说明的剖视图。

图17是对图1所示的半导体装置的制造工序进行说明的剖视图。

图18是对图1所示的半导体装置的制造工序进行说明的剖视图。

图19是本公开的第二实施方式的半导体装置的俯视图,透过了密封树脂。

图20是对应于图19的俯视图,进一步透过了第一绝缘层及半导体元件。

图21是图19所示的半导体装置的仰视图。

图22是对应于图21的仰视图,透过了保护层及多个端子。

图23是沿着图20的XXIII-XXIII线的剖视图。

图24是沿着图20的XXIV-XXIV线的剖视图。

图25是图23的局部放大图。

图26是沿着图20的XXVI-XXVI线的局部放大剖视图。

图27是本公开的第三实施方式的半导体装置的俯视图,透过了散热部件、接合层以及密封树脂。

图28是图27所示的半导体装置的仰视图。

图29是对应于图28的仰视图,是透过了第一绝缘层、保护层以及多个端子的仰视图。

图30是沿着图27的XXX-XXX线的剖视图。

图31是沿着图27的XXXI-XXXI线的剖视图。

图32是图30的局部放大图。

图33是本公开的第四实施方式的半导体装置的俯视图,透过了透光树脂。

图34是对应于图33的俯视图,进一步透过了第一绝缘层及多个第一配线。

图35是沿着图33的XXXV-XXXV线的剖视图。

具体实施方式

基于附图对用于实施本公开的方式进行说明。

〔第一实施方式〕

基于图1~图9,对本公开的第一实施方式的半导体装置A10进行说明。半导体装置A10具备第一绝缘层11、多个第一配线21、半导体元件30、密封树脂41、保护层42以及多个端子50。半导体装置A10是在配线基板进行表面装配的Fan-Out型的封装体。在此,为了便于理解,图1透过了密封树脂41。为了便于理解,图2相对于图1进一步透过了半导体元件30。为了便于理解,图4透过了保护层42及多个端子50。此外,在图2中用假想线(双点划线)示出了透过的半导体元件30的外形。

在半导体装置A10的说明中,将第一绝缘层11的厚度方向称为“厚度方向z”。将相对于厚度方向z正交的方向称为“第一方向x”。将相对于厚度方向z及第一方向x双方正交的方向称为“第二方向y”。如图1所示,沿厚度方向z观察,半导体装置A10的外形为矩形状。第一方向x对应于半导体装置A10的长边方向。第二方向y对应于半导体装置A10的短边方向。此外,厚度方向z、第一方向x以及第二方向y也应用于后述的半导体装置A20~半导体装置A40的说明。

如图5及图6所示,第一绝缘层11在厚度方向z上与半导体元件30对置。第一绝缘层11由包含热固化性的合成树脂及含有组成多个第一配线21的一部分的金属元素的添加剂的材料构成。该合成树脂例如是环氧树脂、聚酰亚胺树脂。第一绝缘层11具有第一面11A、第二面11B以及多个端面11C。第一面11A及第二面11B在厚度方向z上互相朝向相反侧。第一面11A与半导体元件30对置。在半导体装置A10中,在将半导体装置A10装配于配线基板时,第二面11B与该配线基板对置。多个端面11C与第一面11A及第二面11B双方相连。多个端面11C的每一个朝向第一方向x及第二方向y的任一个。

如图7~图9所示,第一绝缘层11具有多个第一槽111。多个第一槽111从第二面11B朝向厚度方向z凹陷。如图9所示,多个第一槽111的每一个的侧面在厚度方向z上从第一槽111的底面到第二面11B带有锥度。在多个第一槽111的每一个中,第一槽111的底面的第一方向x的尺寸c1小于在第一方向x上互相分离的第一槽111与第二面11B的两个边界之间的尺寸c2。

如图5及图6所示,多个第一配线21配置于第一绝缘层11。多个第一配线21构成用于向半导体元件30供给电力且用于输入输出信号的导电路径。多个第一配线21的每一个具有第一埋入部211及第一再配线部212。第一埋入部211至少一部分(在半导体装置A10中为全部)埋入第一绝缘层11。如图7所示,第一埋入部211的侧面在厚度方向z上从第一绝缘层11的第一面11A朝向第二面11B带有锥度。最靠近第一面11A的第一埋入部211的端面的与厚度方向z正交的方向的尺寸b1小于最靠近第二面11B的第一埋入部211的端面的与厚度方向z正交的方向的尺寸b2。第一再配线部212配置于第一绝缘层11的第二面11B。第一再配线部212与第一埋入部211相连。如图1~图4所示,沿厚度方向z观察,多个第一配线21的第一再配线部212包括位于比半导体元件30靠外方的部分。多个第一配线21的第一再配线部212与第一绝缘层11的多个第一槽111相接。因此,多个第一配线21的第一再配线部212为它们的一部分被埋入多个第一槽111的结构。

如图7及图8所示,多个第一配线21的第一埋入部211及多个第一配线21的第一再配线部212的每一个具有基底层21A及镀敷层21B。基底层21A由第一绝缘层11所含的添加剂含有的金属元素组成。镀敷层21B例如由包含铜(Cu)的材料构成。第一埋入部211的基底层21A与第一绝缘层11相接。第一埋入部211的镀敷层21B被第一埋入部211的基底层21A绕厚度方向z包围。第一再配线部212的基底层21A与第一绝缘层11的多个第一槽111的任一个相接。第一再配线部212的镀敷层21B覆盖第一再配线部212的基底层21A。如图9所示,第一再配线部212的镀敷层21B具有朝向厚度方向z凹陷的凹部212A。凹部212A沿多个第一配线21的第一再配线部212的任一个延伸的方向延伸。

如图5及图6所示,半导体元件30与多个第一配线21相连。半导体元件30与第一绝缘层11的第一面11A相接。在半导体装置A10中,半导体元件30例如是构成有LDO(Low DropOut)等电压控制电路、运算放大器等放大电路等的LSI(Large Scale Integration)。另外,在半导体装置A10中,半导体元件30是倒装芯片型的元件。如图1、图5以及图6所示,半导体元件30具有多个电极31。多个电极31设置于第一面11A的附近。多个电极31与构成于半导体元件30的电路导通。多个电极31包含例如铝(Al)。多个电极31与多个第一配线21的第一埋入部211的至少一部分(在半导体装置A10中为全部)直接相连。由此,半导体元件30与多个第一配线21导通。

如图5及图6所示,密封树脂41覆盖半导体元件30的一部分。密封树脂41与第一绝缘层11的第一面11A相接。密封树脂41由例如包含黑色的环氧树脂的材料构成。密封树脂41具有多个侧面411。多个侧面411的每一个朝向第一方向x及第二方向y的任一个。多个侧面411的每一个与第一绝缘层11的多个端面11C的任一个齐平。

如图5及图6所示,保护层42与第一绝缘层11的第二面11B相接。多个第一配线21的第一再配线部212被保护层42覆盖。保护层42具有电绝缘性。保护层42例如由包含聚酰亚胺的材料构成。如图3及图8所示,保护层42具有多个开口部421。多个开口部421沿厚度方向z贯通保护层42。多个第一配线21的第一再配线部212的一部分从多个开口部421露出。

如图3及图8所示,多个端子50与从保护层42的多个开口部421露出的多个第一配线21的第一再配线部212的一部分个别地接合。多个端子50用于将半导体装置A10装配于配线基板。多个端子50从保护层42朝向厚度方向z突出。如图8所示,在半导体装置A10表示的例子中,多个端子50的每一个具有基部51及凸出部52。基部51与多个第一配线21的第一再配线部212的任意一部分相接。基部51由在从第一绝缘层11的第二面11B沿厚度方向z离开的方向上依次层叠镍(Ni)层、钯层(Pd)、金(Au)层的多个金属层构成。此外,也可以不设置这些金属层中的钯层。凸出部52与基部51及保护层42双方相接。凸出部52包括从保护层42朝向厚度方向z突出的部分。凸出部52由包含锡(Sn)的材料构成。

接下来,基于图11~图18,对半导体装置A10的制造方法的一例进行说明。此外,图11~图18(除了图13及图15)的截面位置与图5的截面位置相同。

首先,如图10所示,将半导体元件30埋入密封树脂81。密封树脂81由包含黑色的环氧树脂的材料构成。半导体元件30具有设于厚度方向z的任意侧的多个电极31。在本工序中,在金属模具内配置密封树脂81的材料和半导体元件30后,进行压缩成形。由此,半导体元件30被埋入密封树脂81。此时,使多个电极31从密封树脂81露出。

接下来,如图11所示,形成层叠于密封树脂81且覆盖半导体元件30的多个电极31的绝缘层82。绝缘层82由包含热固化性的合成树脂及含有组成多个配线83(详情后述)的一部分的金属元素的添加剂的材料构成。该合成树脂例如是环氧树脂、聚酰亚胺树脂。绝缘层82通过压缩成形而形成。

接下来,如图12~图15所示,形成与半导体元件30的多个电极31相连的多个配线83。多个配线83相当于半导体装置A10的多个第一配线21。如图14所示,多个配线83的每一个具有埋入部831及再配线部832。埋入部831被埋入配线83,且与多个电极31的任一个相连。再配线部832配置于绝缘层82上,且与埋入部831相连。如图15所示,多个配线83的埋入部831及多个配线83的再配线部832的每一个具有基底层83A及镀敷层83B。形成多个配线83的工序包括使覆盖绝缘层82的表面的基底层83A析出的工序和形成覆盖基底层83A的镀敷层83B的工序。

首先,如图13所示,使覆盖绝缘层82的表面的基底层83A析出。在本工序中,如图12所示,利用激光在绝缘层82形成多个孔821及多个槽822。多个孔821沿厚度方向z贯通绝缘层82。半导体元件30的多个电极31从多个孔821个别地露出。多个孔821通过一边利用红外照相机等对多个电极31的位置进行图像识别,一般直至多个电极31露出对绝缘层82照射激光而形成。基于通过图像识别获得的多个电极31的位置信息对照射激光的位置进行逐一修正。多个槽822从绝缘层82的表面凹陷,且与多个孔821相连。多个槽822通过对绝缘层82的表面照射激光而形成。此外,该激光例如是波长为355nm且光束的直径为17μm的紫外线激光。通过在绝缘层82形成多个孔821及多个槽822,如图13所示地,覆盖规定多个孔821的每一个的壁面和多个槽822的基底层83A析出。基底层83A由绝缘层82所含的添加剂含有的金属元素组成。通过激光照射,该添加剂含有的金属元素被激发。由此,包含该金属元素的金属层作为基底层83A析出。

接下来,如图15所示,形成覆盖基底层83A的镀敷层83B。镀敷层83B由包含铜的材料构成。镀敷层83B通过无电镀形成。由此,如图14所示,在多个孔821的每一个形成有埋入部831。同时,在多个槽822的每一个形成有再配线部832。由此,进行多个配线83的形成。

接下来,如图16所示,形成层叠于绝缘层82且覆盖多个配线83的一部分的保护层84。保护层84具有沿厚度方向z贯通的多个开口部841。首先,使用旋涂机在绝缘层82的表面和多个配线83的表面涂布感光性聚酰亚胺。然后,通过光刻构图,在该感光性聚酰亚胺形成多个开口部841。此时,多个配线83的再配线部832的一部分从多个开口部841露出。由此,进行保护层84的形成。

接下来,如图17所示,形成与从保护层84的多个开口部841露出的多个配线83的再配线部832个别地接合的多个端子50。首先,形成图8所示的多个端子50的基部51。基部51通过无电镀形成。然后,形成图8所示的多个端子50的凸出部52。凸出部52通过在使焊料等含有锡的导电材料利用回流焊熔融后通过冷却固化而形成。由此,进行多个端子50的形成。

最后,如图18所示,将密封树脂81、绝缘层82以及保护层84沿着切割线CL利用切割刀等切割,由此分割成多个单片。使该单片包括一个半导体元件30和与其相连的多个配线83。通过本工序成为单片的密封树脂81、绝缘层82以及保护层84相当于半导体装置A10的密封树脂41、第一绝缘层11以及保护层42。通过经由以上的工序,制造半导体装置A10。

接下来,对半导体装置A10及半导体装置A10的制造方法的作用效果进行说明。

半导体装置A10具备具有第二面11B的第一绝缘层11和具有第一埋入部211及第一再配线部212的多个第一配线21。多个第一配线21的第一再配线部212配置于第二面11B,并且与相连于半导体元件30的多个电极31的多个第一配线21的第一埋入部211相连。第一绝缘层11具有从第二面11B朝向厚度方向z凹陷的多个第一槽111。多个第一配线21的第一再配线部212与多个第一槽111相接。多个第一槽111相当于在半导体装置A10的制造的用于形成多个配线83的工序中利用激光形成于绝缘层82的多个槽822。

半导体装置A10的制造方法的形成多个配线83的工序包括在绝缘层82的表面使基底层83A析出的工序和形成覆盖基底层83A的镀敷层83B的工序。多个配线83相当于半导体装置A10的多个第一配线21。绝缘层82由包含热固化性的合成树脂及含有组成多个配线83的一部分(基底层83A)的金属元素的添加剂的材料构成。使基底层83A析出的工序通过利用激光在绝缘层82形成多个孔821及多个槽822,使覆盖规定多个孔821的每一个的壁面和多个槽822的基底层83A析出。多个孔821通过一边对半导体元件30的多个电极31的位置进行图像识别,一边使多个电极31露出而形成。由此,即使在由于密封树脂81的固化收缩而半导体元件30产生了位移的情况下,也由于在激光照射时通过图像识别进行对应于多个电极31的位移的位置修正,因此能够高精度地形成使多个电极31露出的多个孔821。即,能够高精度地形成与多个电极31的位置一致的多个配线83。因此,根据半导体装置A10及半导体装置A10的制造,能够抑制半导体元件30的多个电极31与多个配线83(多个第一配线21)的接合部处的错位。

在半导体装置A10的制造方法的形成多个配线83的工序中,镀敷层83B通过无电镀形成。由此,相比电镀的情况,不需要使成为用于形成镀敷的导电路径的基底层83A析出,因此能够更高效地形成多个配线83。

多个第一配线21的第一再配线部212的每一个具有与多个第一槽111的任一个相接的基底层21A和覆盖基底层21A的镀敷层21B。镀敷层21B具有朝向厚度方向z凹陷的凹部212A。凹部212A是因在半导体装置A10的制造方法的形成多个配线83的工序中对覆盖多个槽822的基底层83A形成镀敷层83B而带来的痕跡。因此,凹部212A采用沿多个第一配线21的第一再配线部212的任一个延伸的方向延伸的结构。

半导体装置A10还具备与第一绝缘层11的第二面11B相接的保护层42和多个端子50。多个端子50与从保护层42的多个开口部421露出的多个第一配线21的第一再配线部212的一部分个别地接合。多个端子50从保护层42朝向厚度方向z突出。多个端子50由包含锡的材料构成。由此,在将半导体装置A10装配于配线基板时,更容易装配。

〔第二实施方式〕

基于图19~图26,对本公开的第二实施方式的半导体装置A20进行说明。在这些图中,对与上述的半导体装置A10相同或相似的要素标注相同的符号,并省略重复的说明。

在半导体装置A20中,还具备第二绝缘层12及多个第二配线22的情况和保护层42及多个端子50的结构与上述的半导体装置A10不同。在此,为了便于理解,图19透过了密封树脂41。为了便于理解,图20相对于图19进一步透过了第一绝缘层11及半导体元件30。为了便于理解,图22透过了保护层42及多个端子50。此外,在图20中用假想线示出了透过的半导体元件30的外形。

如图23及图24所示,第二绝缘层12与第一绝缘层11的第二面11B相接。因此,第一绝缘层11为被第二绝缘层12和密封树脂41夹着的结构。第二绝缘层12由包含热固化性的合成树脂及含有组成多个第二配线22的一部分的金属元素的添加剂的材料构成。该合成树脂例如是环氧树脂、聚酰亚胺树脂。第二绝缘层12具有第三面12A、第四面12B以及多个端面12C。第三面12A及第四面12B在厚度方向z上彼此朝向相反侧。第三面12A与第二面11B相接。第四面12B在将半导体装置A20装配于配线基板时与该配线基板对置。多个端面12C与第三面12A及第四面12B双方相连。多个端面12C的每一个朝向第一方向x及第二方向y的任一个。多个端面12C的每一个与第一绝缘层11的多个端面11C的任一个和密封树脂41的多个侧面411的任一个双方齐平。

如图25及图26所示,第二绝缘层12具有多个第二槽121。多个第二槽121从第四面12B朝向厚度方向z凹陷。如图26所示,多个第二槽121的每一个的侧面在厚度方向z上从第二槽121的底面到第四面12B带有锥度。在多个第二槽121的每一个中,第二槽121的底面的第一方向x的尺寸c3小于在第一方向x上互相分离的第二槽121与第四面12B的两个边界之间的尺寸c4。

如图23及图24所示,多个第二配线22配置于第二绝缘层12。多个第二配线22与多个第一配线21一起构成半导体元件30的导电路径。多个第二配线22的每一个具有第二埋入部221及第二再配线部222。第二埋入部221埋入第二绝缘层12。如图25所示,第二埋入部221的侧面在厚度方向z上从第二绝缘层12的第三面12A朝向第四面12B带有锥度。最靠近第三面12A的第二埋入部221的端面的与厚度方向z正交的方向的尺寸b3小于最靠近第四面12B的第二埋入部221的端面的与厚度方向z正交的方向的尺寸b4。第二再配线部222配置于第二绝缘层12的第四面12B。第二再配线部222与第一再配线部212相连。多个第二配线22的第二再配线部222与第二绝缘层12的第二槽121相接。因此,多个第二配线22的第二再配线部222为它们的一部分埋入多个第二槽121的结构。

如图23及图24所示,多个第二配线22的第二埋入部221与多个第一配线21的第一再配线部212相连。由此,半导体元件30经由多个第一配线21与多个第二配线22导通。多个第二配线22的第二埋入部221被第二绝缘层12覆盖。如图20及图22所示,沿厚度方向z观察,多个第二配线22的第二再配线部222包括与多个第一配线21的第一再配线部212重叠的部分。

如图25所示,多个第二配线22的第二埋入部221及多个第二配线22的第二再配线部222的每一个具有基底层22A及镀敷层22B。基底层22A由第二绝缘层12所含的添加剂含有的金属元素组成。镀敷层22B由例如包含铜的材料构成。第二埋入部221的基底层22A与第二绝缘层12相接。第二埋入部221的镀敷层22B被第二埋入部221的基底层22A绕厚度方向z包围。第二再配线部222的基底层22A与第二绝缘层12的多个第二槽121的任一个相接。第二再配线部222的镀敷层22B覆盖第二再配线部222的基底层22A。如图26所示,第二再配线部222的镀敷层22B具有朝向厚度方向z凹陷的凹部222A。凹部222A沿多个第二配线22的第二再配线部222的任一个延伸的方向延伸。

如图23及图24所示,保护层42与第二绝缘层12的第四面12B相接。多个第二配线22的第二再配线部222被保护层42覆盖。多个第二配线22的第二再配线部222的一部分从保护层42的多个开口部421露出。如图21及图25所示,多个端子50与从多个开口部421露出的多个第二配线22的第二再配线部222的一部分个别地接合。

接下来,对半导体装置A20的作用效果进行说明。

半导体装置A20具备具有第二面11B的第一绝缘层11和具有第一埋入部211及第一再配线部212的多个第一配线21。多个第一配线21的第一再配线部212配置于第二面11B,并且与相连于半导体元件30的多个电极31的多个第一配线21的第一埋入部211相连。第一绝缘层11具有从第二面11B朝向厚度方向z凹陷的多个第一槽111。多个第一配线21的第一再配线部212与多个第一槽111相接。因此,根据半导体装置A20,也可抑制半导体元件30的多个电极31与多个第一配线21的接合部处的错位。

半导体装置A20还具备具有第三面12A及第四面12B的第二绝缘层12和具有第二埋入部221及第二再配线部222的多个第二配线22。第三面12A与第一绝缘层11的第二面11B相接。多个第二配线22的第二再配线部222配置于第四面12B,并且与埋入到第二绝缘层12的多个第二配线22的第二埋入部221相连。多个第一配线21的第一再配线部212与多个第二配线22的第二埋入部221相连,且被第二绝缘层12覆盖。由此,在半导体装置A20中,能够使多个第一配线21和多个第二配线22在厚度方向z上进行多层配置。因此,沿厚度方向z观察,多个第二配线22的第二再配线部222能够采取与多个第一配线21的第一再配线部212重叠的配置方式。因此,根据半导体装置A20,能够采用比半导体装置A10复杂的配线图案。

〔第三实施方式〕

基于图27~图32,对本公开的第三实施方式的半导体装置A30进行说明。在这些图中,对与上述的半导体装置A10相同或相似的要素标注相同的符号,并省略重复的说明。

在半导体装置A30中,还具备散热部件23及接合层39的情况和多个第一配线21的第一埋入部211及半导体元件30的结构与上述的半导体装置A10不同。在此,为了便于理解,图27透过了散热部件23、接合层39以及密封树脂41。为了便于理解,图29透过了第一绝缘层11、保护层42以及多个端子50。此外,在图27中用假想线示出了透过的散热部件23及接合层39的每一个的外形。

在半导体装置A30中,半导体元件30是MOSFET(Metal-Oxide-SemiconductorField-Effect Transistor)等开关元件。因此,半导体装置A30用于DC/DC转换器及各种电器产品的逆变器等。

如图30及31所示,散热部件23在厚度方向z上相对于半导体元件30位于与第一绝缘层11相反的侧。散热部件23的至少一部分被密封树脂41覆盖。散热部件23例如是包含铜的金属板。散热部件23除了使半导体装置A30的使用时从半导体元件30产生的热散发到外部,还与多个第一配线21一起构成了半导体元件30的导电路径。

在半导体装置A30中,半导体元件30例如是由以碳化硅(SiC)为主的半导体材料构成的MOSFET。此外,半导体元件30不限于MOSFET,也可以是包含MISFET(Metal-Insulator-Semiconductor Field-Effect Transistor)的场效应晶体管、如IGBT(Insulated GateBipolar Transistor)的双极性晶体管。在半导体装置A30的说明中,将半导体元件30为n沟道型的MOSFET的情况作为对象。

如图27及图29~图32所示,半导体元件30的多个电极31包括主面电极311及栅极电极312。沿厚度方向z观察,主面电极311的面积大于栅极电极312的面积。源极电流从半导体元件30的内部向主面电极311流动。对栅极电极312施加用于驱动半导体元件30的栅极电压。

如图32所示,半导体元件30具有背面电极32及绝缘膜33。如图30~图32所示,背面电极32位于在厚度方向z上比主面电极311及栅极电极312相距第一绝缘层11的第一面11A更远的位置。背面电极32与散热部件23对置。背面电极32遍及与散热部件23对置的半导体元件30的整个表面设置。在背面电极32,漏极电流朝向半导体元件30的内部流动。

如图32所示,绝缘膜33与主面电极311及栅极电极312同样地设于第一绝缘层11的第一面11A的附近。如图29所示,沿厚度方向z观察,绝缘膜33将主面电极311及栅极电极312分别包围。绝缘膜33在厚度方向z上朝向靠近第一面11A的方向,例如依次层叠有二氧化硅(SiO

如图30~图32所示,接合层39介于半导体元件30的背面电极32与散热部件23之间。接合层39例如是以锡为主成分的无铅焊料或烧成银。由此,背面电极32与散热部件23接合。同时,散热部件23经由接合层39与背面电极32导通。

如图30所示,多个第一配线21的第一埋入部211包括埋入第一绝缘层11的部分和埋入第一绝缘层11及密封树脂41双方的部分。埋入第一绝缘层11的多个第一配线21的第一埋入部211与半导体元件30的多个电极31(主面电极311及栅极电极312)相连。埋入第一绝缘层11及密封树脂41双方的多个第一配线21的第一埋入部211与散热部件23接合。

接下来,对半导体装置A30的作用效果进行说明。

半导体装置A30具备具有第二面11B的第一绝缘层11和具有第一埋入部211及第一再配线部212的多个第一配线21。多个第一配线21的第一再配线部212配置于第二面11B,并且与相连于半导体元件30的多个电极31的多个第一配线21的第一埋入部211相连。第一绝缘层11具有从第二面11B朝向厚度方向z凹陷的多个第一槽111。多个第一配线21的第一再配线部212与多个第一槽111相接。因此,根据半导体装置A30,也可抑制半导体元件30的多个电极31与多个第一配线21的接合部处的错位。

半导体装置A30还具备相对于半导体元件30位于与第一绝缘层11相反的侧的散热部件23。半导体元件30的背面电极32和多个第一配线21的第一埋入部211的一部分与散热部件23接合。由此,在半导体元件30是n沟道型的MOSFET的情况下,散热部件23为漏极电流流通的半导体元件30的导电路径。同时,在使用半导体装置A30时,能够使从半导体元件30产生的热高效地散发到外部。

〔第四实施方式〕

基于图33~图35,对本公开的第四实施方式的半导体装置A40进行说明。在这些图中,对与上述的半导体装置A10相同或相似的要素标注相同的符号,并省略重复的说明。

在半导体装置A40中,还具备多个贯通配线24及透光树脂43的情况和第一绝缘层11、半导体元件30以及多个端子50的结构与上述的半导体装置A10不同。另外,半导体装置A40为不具备保护层42的结构。为了便于理解,图33透过了透光树脂43。为了便于理解,图34相对于图33进一步透过了第一绝缘层11及多个第一配线21。此外,在图34中用假想线示出了透过的第一绝缘层11的外形。

如图33~图35所示,第一绝缘层11包括在第一方向x上互相分离的部分。由此,半导体元件30包括未被第一绝缘层11覆盖的部分。在半导体装置A40中,半导体元件30是该部分发光的光学元件。在半导体装置A40表示的例子中,该光学元件是LED。当对半导体元件30的多个电极31施加电压时,从该部分朝向厚度方向z发光。

如图33及图34所示,沿厚度方向z观察,多个贯通配线24位于比半导体元件30靠外方。如图35所示,多个贯通配线24与多个第一配线21的第一再配线部212相连。多个贯通配线24从多个第一配线21的第一再配线部212沿厚度方向z延伸,且贯通密封树脂41。多个贯通配线24由例如包含铜的材料构成。

如图35所示,透光树脂43与密封树脂41相接。透光树脂43覆盖第一绝缘层11、半导体元件30以及多个第一配线21的第一再配线部212的每一个的各一部分。从半导体元件30发出的光透过透光树脂43。透光树脂43由例如包含透明的环氧树脂或含有硅的合成树脂的材料构成。

如图35所示,多个端子50与从密封树脂41露出的多个贯通配线24的一部分个别地接合。多个端子50从密封树脂41朝向厚度方向z突出。

接下来,对半导体装置A40的作用效果进行说明。

半导体装置A40具备具有第二面11B的第一绝缘层11和具有第一埋入部211及第一再配线部212的多个第一配线21。多个第一配线21的第一再配线部212配置于第二面11B,并且与相连于半导体元件30的多个电极31的多个第一配线21的第一埋入部211相连。第一绝缘层11具有从第二面11B朝向厚度方向z凹陷的多个第一槽111。多个第一配线21的第一再配线部212与多个第一槽111相接。因此,根据半导体装置A40,也可抑制半导体元件30的多个电极31与多个第一配线21的接合部处的错位。

在半导体装置A40中,半导体元件30是未被第一绝缘层11覆盖的部分发光的光学元件。半导体装置A40还具备多个贯通配线24,沿着厚度方向z观察,该多个贯通配线24位于比半导体元件30靠外方,且与多个第一配线21的第一再配线部212相连。多个贯通配线24从多个第一配线21的第一再配线部212沿厚度方向z延伸,且贯通密封树脂41。由此,能够以在厚度方向z上,在与光从半导体元件30发出的方向相反的方向上与配线基板对置的方式将半导体装置A40装配于该配线基板。

本公开不限于上述的实施方式。例如,在上述的实施方式中,半导体元件30均为单数,但也可以是半导体元件为多个的结构。另外,在上述的实施方式中,沿厚度方向z观察,外形均为矩形状,但这些外形不限于矩形状,例如也可以是圆形状或六边形状。本公开的各部的具体结构可自由地进行各种设计变更。

本公开的各种实施方式可以限定为以下的附记。

附记1.一种半导体装置,其特征在于,具备:

第一绝缘层,其具有在厚度方向上彼此朝向相反侧的第一面及第二面;

多个第一配线,其具有至少一部分埋入上述第一绝缘层的第一埋入部及配置于上述第二面且与上述第一埋入部相连的第一再配线部;

半导体元件,其具有设于上述第一面的附近且与上述多个第一配线的上述第一埋入部的至少一部分相连的多个电极,并且与上述第一面相接;以及

密封树脂,其与上述第一面相接,且覆盖上述半导体元件的一部分,

沿上述厚度方向观察,上述多个第一配线的上述第一再配线部包括位于比上述半导体元件靠外方的部分,

上述第一绝缘层具有从上述第二面朝向上述厚度方向凹陷的多个第一槽,

上述多个第一配线的上述第一再配线部与上述多个第一槽相接。

附记2.根据附记1所述的半导体装置,其特征在于,

上述第一绝缘层由包含热固化性的合成树脂及添加剂的材料构成,该添加剂含有组成上述多个第一配线的一部分的金属元素。

附记3.根据附记2所述的半导体装置,其特征在于,

上述多个第一配线的上述第一再配线部的每一个具有与上述多个第一槽中的任一个相接的基底层和覆盖上述基底层的镀敷层,

上述基底层由上述添加剂含有的上述金属元素组成,

上述镀敷层具有朝向上述厚度方向凹陷的凹部。

附记4.根据附记3所述的半导体装置,其特征在于,

上述凹部沿上述多个第一配线的上述第一再配线部的任一个延伸的方向延伸。

附记5.根据附记4所述的半导体装置,其特征在于,

还具备与上述第二面相接的保护层,

上述保护层具有沿上述厚度方向贯通的多个开口部,

上述多个第一配线的上述第一再配线部的一部分从上述多个开口部露出。

附记6.根据附记5所述的半导体装置,其特征在于,

还具备多个端子,

上述多个端子与从上述多个开口部露出的上述多个第一配线的上述第一再配线部的一部分个别地接合,

上述多个端子从上述保护层朝向上述厚度方向突出。

附记7.根据附记6所述的半导体装置,其特征在于,

上述多个端子由包含锡的材料构成。

附记8.根据附记1~4中任一项所述的半导体装置,其特征在于,

还具备:

第二绝缘层,其具有在厚度方向上彼此朝向相反侧的第三面及第四面,且上述第三面与上述第二面相接;以及

多个第二配线,其具有埋入上述第二绝缘层的第二埋入部及配置于上述第四面且与上述第二埋入部相连的第二再配线部,

上述多个第一配线的上述第一再配线部与上述多个第二配线的上述第二埋入部相连,且被上述第二绝缘层覆盖。

附记9.根据附记8所述的半导体装置,其特征在于,

沿上述厚度方向观察,上述多个第二配线的上述第二再配线部包括与上述多个第一配线的上述第一再配线部重叠的部分。

附记10.根据附记9所述的半导体装置,其特征在于,

上述第二绝缘层具有从上述第四面朝向上述厚度方向凹陷的多个第二槽,

上述多个第二配线的上述第二再配线部与上述多个第二槽相接。

附记11.根据附记10所述的半导体装置,其特征在于,

上述第二绝缘层由包含热固化性的合成树脂及添加剂的材料构成,该添加剂含有组成上述多个第二配线的一部分的金属元素。

附记12.根据附记1~11中任一项所述的半导体装置,其特征在于,

还具备散热部件,该散热部件相对于上述半导体元件位于与上述第一绝缘层相反的侧,

上述多个电极包括主面电极及栅极电极,

上述半导体元件具有背面电极,该背面电极位于在上述厚度方向上相距上述第一面比上述主面电极及上述栅极电极更远的位置,

上述背面电极和上述多个第一配线的上述第一埋入部的一部分与上述散热部件接合,

上述散热部件的至少一部分被上述密封树脂覆盖。

附记13.根据附记1~4中任一项所述的半导体装置,其特征在于,

上述半导体元件是未被上述第一绝缘层覆盖的部分发光的光学元件,

还具备多个贯通配线,该多个贯通配线沿上述厚度方向观察位于比上述半导体元件靠外方,且与上述多个第一配线的上述第一再配线部相连,

上述多个贯通配线从上述多个第一配线的上述第一再配线部向上述厚度方向延伸,且贯通上述密封树脂。

附记14.根据附记13所述的半导体装置,其特征在于,

还具备与上述密封树脂相接的透光树脂,

上述透光树脂覆盖上述第一绝缘层、上述半导体元件以及上述多个第一配线的上述第一再配线部的每一个的各一部分。

附记15.根据附记13或14所述的半导体装置,其特征在于,

还具备多个端子,

上述多个端子与从上述密封树脂露出的上述多个贯通配线的一部分个别地接合,

上述多个端子从上述密封树脂朝向上述厚度方向突出。

附记16.一种半导体装置的制造方法,其特征在于,具备:

将具有设于厚度方向的任一侧的多个电极的半导体元件以使上述多个电极露出的方式埋入密封树脂的工序;

形成层叠于上述密封树脂且覆盖上述多个电极的绝缘层的工序;以及

形成多个配线的工序,该多个配线具有埋入上述绝缘层且与上述多个电极的任一个相连的埋入部及配置于上述绝缘层上且与上述埋入部相连的再配线部,

上述绝缘层由包含热固化性的合成树脂及添加剂的材料构成,该添加剂含有组成上述多个配线的一部分的金属元素,

形成上述多个配线的工序包括如下工序:

一边对上述多个电极的位置进行图像识别,一边利用激光在上述绝缘层形成使上述多个电极露出的多个孔和从上述绝缘层的表面凹陷且与上述多个孔相连的多个槽,由此使覆盖规定上述多个孔的每一个的壁面和上述多个槽的基底层析出;以及

形成覆盖上述基底层的镀敷层。

附记17.根据附记16所述的半导体装置的制造方法,其特征在于,

在形成上述镀敷层的工序中,通过无电镀形成上述镀敷层。

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置

- 碳化硅半导体装置的制造方法、半导体基体的制造方法、碳化硅半导体装置以及碳化硅半导体装置的制造装置