一种电容-电压转换电路

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及陀螺仪应用领域,尤其涉及一种电容-电压转换电路。

背景技术

近年来,随着微机械系统(MEMS)的快速发展,电容型MEMS陀螺仪因其低功耗、低温漂、高精度以及与CMOS工艺兼容等优势,在卫星、车载、深海等惯性导航系统中得到了广泛应用。电容型MEMS陀螺仪作为一个传感换能单元,将角速度转换为差分电容变量。为了进行后续数据处理,需要在处理器和MEMS陀螺仪之间加入模拟前端电路(主要包括电容-电压转换电路、Sigma delta模数转换器两部分),将电容物理量转换为数字量。而作为模拟前端电路第一级的电容-电压转换电路,其噪声底板、动态范围、线性度、建立时间等参数更是系统成败的关键。

发明内容

本发明的目的是提供一种大信号带宽、优动态范围、低功耗、满足精度的电容-电压转换电路。

为实现上述目的,本发明提供了以下方案:

一种电容-电压转换电路,包括源差分输入端、源差分输出端、全差分放大器电路单元、第一时钟信号输入端和第二时钟信号输入端;所述第一时钟信号输入端、第二时钟信号输入端分别用于输入第一时钟信号clk1、第二时钟信号clk2;所述全差分放大器电路单元包括第一运放、开关S25、开关S26、开关S34、开关S35、补偿电容Cc1、补偿电容Cc2、保持电容CH1、保持电容CH2;所述第一运放为一差分放大器,包括一差分输入端和一差分输出端;所述第一运放的差分输入端的负信号端连接节点b5,所述第一运放的差分输入端的正信号端连接节点b6;所述补偿电容Cc1的两端分别连接节点b5和节点a1,所述节点a1连接所述源差分输入端的正信号端;所述补偿电容Cc2的两端分别连接节点b6和节点a2,所述节点a2连接所述源差分输入端的负信号端;所述保持电容CH1的两端分别连接节点b4和节点a4;所述开关S25的两端分别连接节点a4和参考电位Vref;所述开关S26的两端分别连接节点a4和节点b5;所述保持电容CH2的两端分别连接节点b7和节点a7;所述开关S34的两端分别连接节点a7和参考电位Vref;所述开关S35的两端分别连接节点a7和节点b6;所述开关S26、所述开关S35受所述第一时钟信号clk1控制;所述开关S25、所述开关S34受所述第二时钟信号clk2控制;所述第一时钟信号clk1、所述第二时钟信号clk2用于实现所述电容-电压转换电路的采样相与放大相的转换。

技术效果:补偿电容Cc1、Cc2在采样相时其一端接入参考电位Vref,保持电容CH1、CH2在放大相时其一端也接入参考电位Vref,因此在下一个采样相周期时在第一运放U1的输入端构成一个真实的“虚地点”,并且保持电容CH1、CH2在放大相时其一端连接至参考电位Vref,另一端保持了上一个放大相时第一运放U1的输出电压值,消除了传统结构中的归零操作,有利于本周期输出电压的快速建立。

进一步的,所述全差分放大器电路单元还包括第一增益电容阵列、第二增益电容阵列、开关S18、开关S27、开关S23、开关S24、开关S32、开关S33;

所述第一增益电容阵列和所述第二增益电容的电路配置相同;所述第一增益电容阵列的一端和所述节点a1连接,及通过开关S18和所述参考电位Vref连接;另一端通过所述开关S24和所述节点b4连接,及通过所述开关S23和所述参考电位Vref连接;所述第二增益电容阵列的一端和所述节点a2连接,及通过所述开关S27和所述参考电位Vref连接;另一端通过所述开关S33和所述节点b7连接,及通过所述开关S32和所述参考电位Vref连接;所述开关S18、开关S23、开关S27、开关S32受所述第一时钟信号clk1控制;所述开关S24、所述开关S33受所述第二时钟信号clk2控制。

进一步的,所述增益电容阵列包括一基础增益电容和多个扩展增益电容,各所述扩展增益电容分别和一开关串联后和所述基础增益电容并联,通过选通开关以调节所述增益电容阵列的容值。

进一步的,所述第一运放包括晶体管M0、晶体管M1、晶体管M2、晶体管M3、晶体管M4、晶体管M5、晶体管M6、晶体管M7、晶体管M8、晶体管M9、晶体管M10;所述第一运放包括一差分输入端、一差分输出端和多个控制输入端;所述第一运放的差分输入端用于输入信号Vin、信号Vip;所述第一运放的差分输出端用于输出信号Voutp、信号Voutn;所述第一运放的控制输入端用于输入控制信号,包括:信号Vbtail、信号Vcnfbout、信号Vb1、信号Vb2、信号Vb3和参考电位Vref;所述第一运放的内部电路的电路连接关系为:所述晶体管M0的栅极接信号Vbtail、源极接地电位、漏极接结点t6;所述晶体管M1的栅极接信号Vin、源极接结点t6、漏极接结点t5;所述晶体管M2的栅极接信号Vip、源极接结点t6、漏极接结点t7;所述晶体管M3的栅极接信号Vb1、源极接地电位、漏极接所述晶体管M5的源极;所述晶体管M4的栅极接信号Vb1、源极接地电位、漏极接所述晶体管M6的源极;所述晶体管M5的栅极接信号Vb2、源极接晶体管M3的漏极、漏极接结点t8,所述信号Voutp接结点t8;所述晶体管M6的栅极接信号Vb2、源极接晶体管M4的漏极、漏极接结点t9,所述信号Voutn接结点t9;所述晶体管M7的栅极接信号Vb3、源极接结点t5、漏极接结点t8;所述晶体管M8的栅极接信号Vb3、源极接结点t7、漏极接结点t9;所述晶体管M9的栅极接信号Vcmfout、源极接电源电位、漏极接结点t5;所述晶体管M10的栅极接信号Vcmfout、源极接电源电位、漏极接结点t7。

进一步的,所述第一运放还包括电容C1、电容C2、电容C3、电容C4、开关S36、开关S37、开关S38、开关S39、开关S40、开关S41、第三时钟信号输入端、第四时钟信号输入端;所述第一运放的内部电路的电路连接关系还包括:所述信号Voutn连接节点r1;所述信号Voutp连接节点r3;所述电容C1的两端分别连接结点r1和结点r2;所述电容C2的两端分别连接节点r2和节点r3;所述电容C3的两端分别连接节点r4和节点r5;所述电容C4的两端分别连接节点r5和节点r6;所述开关S36的两端分别连接节点r1和节点r4;所述开关S37的两端分别连接节点r4和信号Vcm;所述开关S38的两端分别连接节点r2和节点r5;所述开关S39的两端分别连接节点r5和参考电位Vref;所述开关S40的两端分别连接节点r3和节点r6;所述开关S41的两端分别连接节点r6和信号Vcm;所述第三时钟信号输入端、所述第四时钟信号输入端分别用于输入第三时钟信号clk1a、第四时钟信号clk2a,所述第三时钟信号clk1a是第一时钟信号clk1的提前关断信号,所述第四时钟信号clk2a是第二时钟信号clk2的提前关断信号,所述开关S36、开关S38、开关S40的开启受第三时钟信号clk1a控制,所述开关S37、开关S39、开关S41的开启受第四时钟信号clk2a控制。

技术效果:本发明的全差分运算放大器采用双端输入、双端输出的折叠共源共栅结构,可以提供大输出摆幅。并在全差分放大器中设置有clk1a和clk2a两个提前关断时钟信号,降低了在放大相时保持电容CH1、CH2上的电荷共享效应,提高输出信号精度。

进一步的,还包括输入共模反馈放大器电路单元,所述输入共模反馈放大器电路单元包括第二运放、开关S4、第一反馈电容和第二反馈电容,所述第二运放包括一差分输入端和一输出端;所述第二运放的差分输入端的两端分别和所述源差分输入端的两端连接;所述第二运放的输出端分别通过所述第一反馈电容、所述第二反馈电容和所述源差分输入端的两端连接,及通过所述开关S4和参考电位Vref连接;所述开关S4受所述第一时钟信号clk1控制。

技术效果:将第二运放U2的两个差分输入端的共模值与参考电位Vref的电压值进行比较,消除了该部分产生的误差电荷,从而保证第二运放U2的输入共模电压的稳定同时也有效抑制了共模电压漂移引起的热噪声。

进一步的,所述输入共模反馈放大器电路单元还包括开关S3和开关S5,所述源差分输入端的两端分别通过开关S3、开关S5和参考电位Vref连接,所述开关S3、开关S5受第一时钟信号clk1控制。

进一步的,所述第二运放的内部电路包括晶体管M0、晶体管M1a、晶体管M1b、晶体管M2、晶体管M3、晶体管M4、晶体管M5、晶体管M6、晶体管M7、晶体管M8、晶体管M9、晶体管M10;所述第二运放的差分输入端包括一差分输入端、一输出端和多个控制输入端;所述第二运放的差分输入端用于输入信号Vin2、信号Vip2;所述第二运放的输出端用于输出信号Voutp2;所述第二运放的控制输入端用于输入控制信号,包括:信号Vbp1、信号Vbp2、信号Vbn1、信号Vbn2和参考电位Vref;所述晶体管M0的栅极接信号Vbn2、源极接地电位、漏极接结点t2;所述晶体管M1a的栅极接信号Vin2、源极接结点t2、漏极接结点t1;所述晶体管M1b的栅极接信号Vip2、源极接结点t2、漏极接结点t1;所述晶体管M2的栅极接参考电位Vref、源极接结点t2、漏极接结点t3;所述晶体管M3的栅极接结点t4、源极接地电位、漏极接所述晶体管M5的源极;所述晶体管M4的栅极接结点t4、源极接地电位、漏极接所述晶体管M6的源极;所述晶体管M5的栅极接信号Vbn1、源极接所述晶体管M3的漏极、漏极接结点t5;所述信号Voutp2接结点t5;所述晶体管M6的栅极接信号Vbn1、源极接所述晶体管M4的漏极、漏极接结点t4;所述晶体管M7的栅极接信号Vbp2、源极接结点t1、漏极接结点t5;所述信号Voutp2接结点t5;所述晶体管M8的栅极接信号Vbp2、源极接结点t3、漏极接结点t4;所述晶体管M9的栅极接信号Vbp1、源极接电源电位、漏极接结点t1;所述晶体管M10的栅极接信号Vbp1、源极接电源电位、漏极接结点t3。

进一步的,还包括补偿电容阵列,所述补偿电容阵列包括第一子电容阵列、第二子电容阵列,所述第一子电容阵列和第二子电容阵列的电路配置相同;所述第一子电容阵列的一端和所述第二子电容阵列的一端连接于节点b2,所述节点b2通过开关S16和地电位连接,及通过开关S17和所述参考电位连接;所述第一子电容阵列的另一端、所述第二子电容阵列的另一端分别连接到所述源差分输入端的两端;所述开关S16受第二时钟信号clk2控制,所述开关S17受第一时钟信号clk1控制。

进一步的,所述子电容阵列包括一基础补偿电容和多个扩展补偿电容,各所述扩展补偿电容分别和一开关串联后和所述基础补偿电容并联,通过选通开关以调节所述子电容阵列的容值。

技术效果:补偿电容阵列通过控制开关可以选择补偿电容,形成不同的电容容值对寄生电容进行补偿、消除增益误差和直流失调。

本发明实现了如下技术效果:

本发明专利提出的电容-电压转换电路,其差分放大采用补偿电容和保持电容结合的两步逼近电路策略,可以有效降低1/A误差带来的影响、实现大信号带宽、优动态范围、低功耗、满足精度的电容-电压转换电路。

附图说明

图1是本发明的电容-电压转换电路的原理框图;

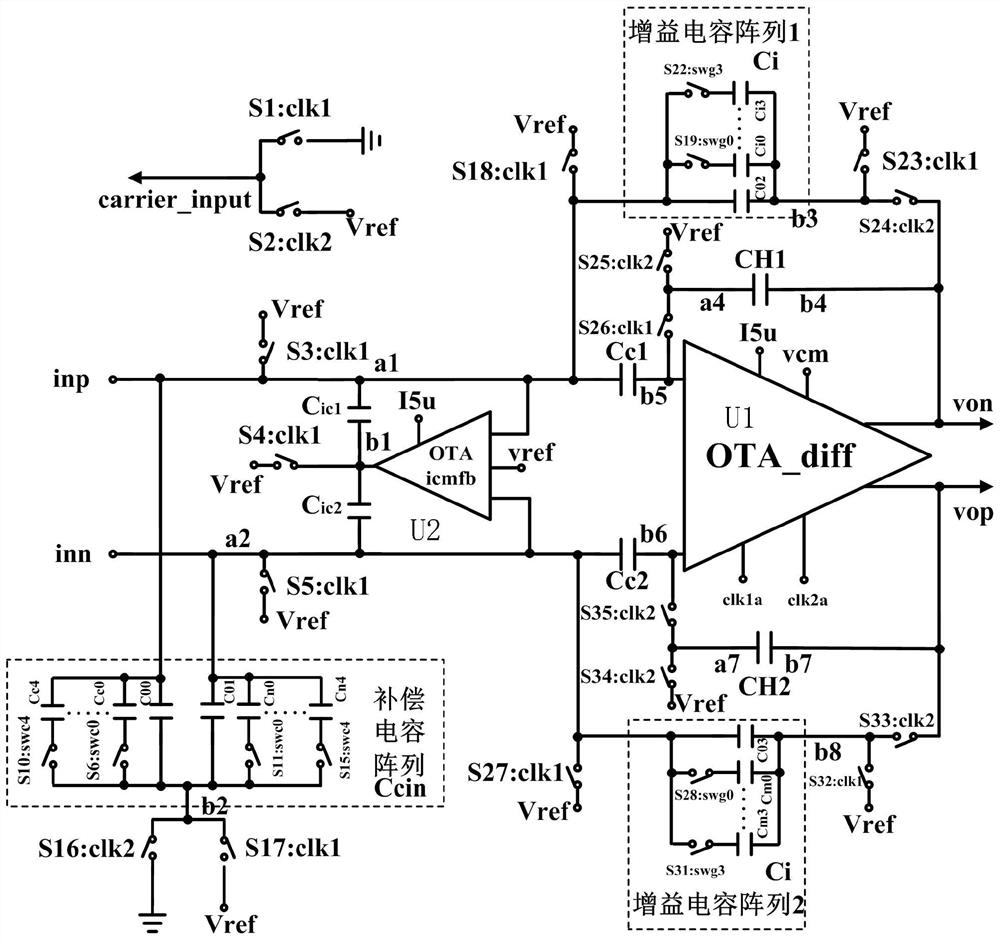

图2是本发明的电容-电压转换电路的电路图的一实施例;

图3是第一运放的内部电路图;

图4是第二运放的内部电路图。

具体实施方式

为进一步说明各实施例,本发明提供有附图。这些附图为本发明揭露内容的一部分,其主要用以说明实施例,并可配合说明书的相关描述来解释实施例的运作原理。配合参考这些内容,本领域普通技术人员应能理解其他可能的实施方式以及本发明的优点。图中的组件并未按比例绘制,而类似的组件符号通常用来表示类似的组件。

现结合附图和具体实施方式对本发明进一步说明。

如图1所示,本发明公开了一种电容-电压转换电路,包括源差分输入端、源差分输出端、补偿电容阵列Ccin、输入共模反馈放大器电路单元、全差分放大器电路单元、第一时钟信号输入端和第二时钟信号输入端;其中,源差分输入端的差分输入信号被标识为inp、inn,源差分输出端的差分输出信号被标识为:vop、von。所述补偿电容阵列的两端跨接于所述源差分输入端;所述输入共模反馈放大器电路单元包括一差分输入端、两反馈信号输入端、一个输出端和多个开关,所述差分输入端分别和所述源差分输入端的两端连接,两反馈信号输入端分别和所述源差分输入端的两端连接,其输出端和参考电位Vref连接;所述全差分放大器电路单元包括一差分输入端、一差分输出端和多个开关,所述全差分放大器电路单元的差分输入端和所述源差分输入端连接,所述全差分放大器电路单元的差分输出端的两端分别和所述源差分输出端的两端连接;第一时钟信号输入端、第二时钟信号输入端用于输入第一时钟信号clk1、第二时钟信号clk2,所述第一时钟信号clk1、所述第二时钟信号clk2用于控制所述输入共模反馈放大器电路单元、所述全差分放大器电路单元中的开关,以实现所述电容-电压转换电路的采样相与放大相的转换。

在如图2所示的实施例中,全差分放大器电路单元包括:第一运放U1、开关S26、开关S35、补偿电容Cc1、补偿电容Cc2、保持电容CH1、保持电容CH2;其中,所述第一运放U1为具有差分输出的差分放大器;

该部分电路单元的电路连接关系为:

第一运放U1的差分输入端的负信号端连接节点b5,差分输入端的正信号端连接节点b6;

第一运放U1的差分输出端为全差分放大器电路单元的差分输出端,第一运放U1的差分输出端的负信号端连接源差分输出端的负信号端von,差分输出端的正信号端连接源差分输出端的正信号端vop;

反馈电容Cc1的两端分别连接节点b5和节点a1,节点a1连接源差分输入端的正信号端inp;

反馈电容Cc2的两端分别连接节点b6和节点a2,节点a2连接源差分输入端的负信号端inn;

保持电容CH1的两端分别连接节点b4和节点a4;开关S25的两端分别连接节点a4和参考电位Vref;开关S26的两端分别连接节点a4和节点b5;其中节点b4和第一运放U1的差分输出端的负信号端连接;

保持电容CH2的两端分别连接节点b7和节点a7;开关S34的两端分别连接节点a7和参考电位Vref;开关S35的两端分别连接节点a7和节点b6;其中,节点b7和第一运放U1的差分输出端的正信号端连接;

开关S26、开关S35的开启受第一时钟信号clk1控制;

开关S25、开关S34的开启受第二时钟信号clk2控制。

在如图2所示的实施例中,输入共模反馈放大器电路单元包括:第二运放U2、开关S4、反馈电容Cic1和反馈电容Cic2,其中,所述第二运放U2为差分放大器。

该部分电路单元的电路连接关系为:

第二运放U2的差分输入端的两端分别连接到节点a1和节点a2;

第二运放U2的输出端连接到节点b1,节点b1通过反馈电容Cic1连接到节点a1,通过反馈电容Cic2连接到节点a2;通过开关S4连接到参考电位Vref;其中开关S4的开启受第一时钟信号clk1控制。

输入共模反馈放大器电路单元还包括开关S3和开关S5,所述源差分输入端的两端分别通过开关S3、开关S5和参考电位Vref连接,开关S3、开关S5的开启受第一时钟信号clk1控制。

carrier_input为载波调制信号,输出至片外陀螺仪。carrier_input通过开关S1接地点位,通过开关S2接参考电位Vref,其中,开关S1的开启受clk1控制,开关S2的开启受clk2控制。

工作原理:

开关S1-S5、S16-S18、S23-S27、S32-S35控制本电容-电压转换电路的采样相与放大相的转换,当clk1=1、clk2=0时,第一时钟信号clk1所控制的开关开启(闭合),本电容-电压转换电路进入采样相;当clk1=0、clk2=1时,第一时钟信号clk1所控制的开关断开,第二时钟信号clk2所控制的开关开启(闭合),本电容-电压转换电路进入放大相。

反馈电容Cic1、Cic2和第二运放U2构成的反馈回路构成三输入、单端输出的折叠共源共栅结构,可以将第二运放U2的两个差分输入端的共模值与参考电位Vref的电压值进行比较,并消除该部分产生的误差电荷,从而保证第二运放U2的输入共模电压的稳定同时也有效抑制了共模电压漂移引起的热噪声;补偿电容Cc1、Cc2和保持电容CH1、CH2结合的两步逼近电路策略,避免输出电压在两相时钟中的归零状态,实现了高速、高精度的信号输出。

其中补偿电容Cc1、Cc2在采样相时其左极板接入参考电位Vref,保持电容CH1、CH2在放大相时其左极板也接入参考电位Vref,因此在下一个采样相周期时在第一运放U1的输入端构成一个真实的“虚地点”,并且保持电容CH1、CH2在放大相时其左极板连接至参考电位Vref,右极板保持了上一个放大相时第一运放U1的输出电压值,消除了传统结构中的归零操作,有利于本周期输出电压的快速建立。

补偿电容阵列Ccin通过控制开关S6-S10、S11-S15可以选择补偿电容,形成不同的电容容值将陀螺仪以及键合产生的寄生电容进行补偿、消除增益误差和直流失调。

在采样相时,增益电容阵列Ci两个极板都连接至参考电位Vref,将消除上一个周期放大相的残余电荷,通过开关S19-S22、S28-S31控制选择不同的增益电容从而实现电路的连续增益可调。

在本发明中,给出了一第一运放U1的内部电路示例,如图3所示。第一运放U1是一种全差分运算放大器,在本示例中,包括电容C1-C4、开关S36-S41、晶体管M0-M10,第一运放U1的输入包括信号Vin、信号Vip、信号Vbtail、信号Vcnfbout、信号Vb1、信号Vb2、信号Vb3和参考电位Vref;第一运放U1的差分输出包括信号Voutp和信号Voutn其中,信号Vbtail为晶体管M0(尾电流源)的栅极偏置电压,使M0工作在饱和区,确定尾电流源的值;信号Vcmfbout为第一运放U1的共模反馈输出电压;信号Vb1为晶体管M3和M4的栅极偏置电压,使晶体管M3、M4工作在饱和区;信号Vb2为晶体管M5和M6的栅极偏置电压,使晶体管M5、M6工作在饱和区;信号Vb3为晶体管M7和M8的栅极偏置电压,使晶体管M7、M8工作在饱和区。

其具体电路连接如下:

信号Voutn连接节点r1;

信号Voutp连接节点r3;

电容C1的两端分别连接结点r1和结点r2;

电容C2的两端分别连接节点r2和节点r3;

电容C3的两端分别连接节点r4和节点r5;

电容C4的两端分别连接节点r5和节点r6;

开关S36的两端分别连接节点r1和节点r4;

开关S37的两端分别连接节点r4和信号Vcm;

开关S38的两端分别连接节点r2和节点r5;

开关S39的两端分别连接节点r5和参考电位Vref;

开关S40的两端分别连接节点r3和节点r6;

开关S41的两端分别连接节点r6和信号Vcm;

晶体管M0的栅极接信号Vbtail、源极接地电位、漏极接结点t6;

晶体管M1的栅极接信号Vin、源极接结点t6、漏极接结点t5;

晶体管M2的栅极接信号Vip、源极接结点t6、漏极接结点t7;

晶体管M3的栅极接信号Vb1、源极接地电位、漏极接晶体管M5的源极;

晶体管M4的栅极接信号Vb1、源极接地电位、漏极接晶体管M6的源极;

晶体管M5的栅极接信号Vb2、源极接晶体管M3的漏极、漏极接结点t8,信号outp接结点t8;

晶体管M6的栅极接信号Vb2、源极接晶体管M4的漏极、漏极接结点t9,信号outn接结点t9;

晶体管M7的栅极接信号Vb3、源极接结点t5、漏极接结点t8;

晶体管M8的栅极接信号Vb3、源极接结点t7、漏极接结点t9;

晶体管M9的栅极接信号Vcmfout、源极接电源电位、漏极接结点t5;

晶体管M10的栅极接信号Vcmfout、源极接电源电位、漏极接结点t7。

该全差分运算放大器采用双端输入、双端输出的折叠共源共栅结构,可以提供大输出摆幅。并在全差分放大器中设置有clk1a和clk2a两个提前关断时钟信号,降低了在放大相(clk1=0,clk2=1)时保持电容CH1、CH2上的电荷共享效应,提高输出信号精度。

两步逼近的工作原理:

在采样相(clk1=1,clk2=0)时,补偿电容Cc1、Cc2的左极板对参考电位Vref的电压值采样,右极板连接至第一运放U1的输入端和保持电容CH1、CH2的左极板连接。因为保持电容CH1、CH2的右极板分别连接至第一运放U1的输出端von、vop,而左极板在上一个周期放大相(clk1=0,clk2=1)时连接至参考电位Vref,在本周期采样相(clk1=1,clk2=0)时,CH1、CH2的左极板保持的参考电压就传输至Cc1、Cc2的右极板和第一运放U1的输入端。该机制使得第一运放U1输入端成为一个真实的“虚地点”(由于参考电位Vref的箝位作用,消除了第一运放U1输入端产生的失调)。同时增益电容阵列Ci的两个极板都连接至参考电位Vref,消除上一个周期放大相的残余电荷。

在放大相(clk1=0,clk2=1)时,增益电容阵列Ci的左极板连接至第一运放U1的输入端,右极板连接至第一运放U1的输出端,形成

在本发明中,给出了一个第二运放U2的内部电路示例,如图4所示。第二运放U2是一种输入共模反馈运放,包括晶体管M0、M1a、M1b、M2、M3、M4、M5、M6、M7、M8、M9、M10。该输入共模反馈运放包括一差分输入端、一输出端和多个控制输入端,其差分输入端输入信号Vin2、信号Vip2;输出端输出信号outp2;控制输入端输入信号Vbp1、信号Vbp2、信号Vbn1、信号Vbn2和参考电位Vref;其中,信号Vbp1为晶体管M9和M10的栅极偏置电压,使晶体管M9和M10工作在饱和区;信号Vbp2为晶体管M7和M8的栅极偏置电压,使晶体管M7和M8工作在饱和区;信号Vbn1为晶体管M5和M6的栅极偏置电压,使晶体管M5和M6工作在饱和区;信号Vbn2为晶体管M0的栅极偏置电压,使晶体管工作在饱和区

其具体电路连接如下:

晶体管M0的栅极接信号Vbn2、源极接地电位、漏极接结点t2;

晶体管M1a的栅极接信号Vin2、源极接结点t2、漏极接结点t1;

晶体管M1b的栅极接信号Vip2、源极接结点t2、漏极接结点t1;

晶体管M2的栅极接信号Vref、源极接结点t2、漏极接结点t3;

晶体管M3的栅极接结点t4、源极接地电位、漏极接晶体管M5的源极;

晶体管M4的栅极接结点t4、源极接地电位、漏极接晶体管M6的源极;

晶体管M5的栅极接信号Vbn1、源极接晶体管M3的漏极、漏极接结点t5;信号outp2接结点t5;

晶体管M6的栅极接信号Vbn1、源极接晶体管M4的漏极、漏极接结点t4;

晶体管M7的栅极接信号Vbp2、源极接结点t1、漏极接结点t5;信号outp2接结点t5;

晶体管M8的栅极接信号Vbp2、源极接结点t3、漏极接结点t4;

晶体管M9的栅极接信号Vbp1、源极接电源电位、漏极接晶体管M1a漏极结点t1;

所述晶体管M10的栅极接信号Vbp1、源极接电源电位、漏极接结点t3。

本发明提出的输入共模反馈运放电路采用三输入、单端输出的折叠共源共栅结构,可以将主运放两个差分输入端的共模值与参考电压进行比较,并消除该部分产生的误差电荷从而保证主运放输入共模电压的稳定同时也有效抑制了共模电压漂移引起的热噪声。

本发明专利提出的电容-电压转换电路,其差分放大采用补偿电容和保持电容结合的两步逼近电路策略,可以有效降低1/A误差带来的影响、实现大信号带宽、优动态范围、低功耗、满足精度的电容-电压转换电路。

尽管结合优选实施方案具体展示和介绍了本发明,但所属领域的技术人员应该明白,在不脱离所附权利要求书所限定的本发明的精神和范围内,在形式上和细节上可以对本发明做出各种变化,均为本发明的保护范围。

- 电容电压转换电路、使用此电容电压转换电路的输入装置、电子设备以及电容电压转换方法

- 电容型MEMS惯性传感器闭环检测的电容电压转换电路