PIP电容的制作方法

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及半导体技术领域,尤其是涉及一种PIP电容的制作方法。

背景技术

截至目前,半导体集成电路设计会有多种电容器可供选择,包括MOS(金属-氧化物-半导体)电容,PIP(多晶硅-绝缘体-多晶硅)电容,MIM(金属-绝缘体-金属)电容,MOM(金属-氧化物-金属)电容等。为了满足客户对电容特性,低成本的要求,PIP电容已被广泛的运用。

请参照图1,现有技术形成PIP电容的方法为,在衬底110内形成浅沟槽隔离结构120,在浅沟槽隔离结构120上形成字线多晶硅130作为PIP电容的下级板、在字线多晶硅130上形成氧化物层140作为电容绝缘层、在氧化物层140上形成栅极多晶硅150,栅极多晶硅150作为电容的上极板。但是随着电子产品的尺寸的减小,电容的尺寸也在减小,导致上极板和下级板的面积也再减小,最后使得制成的电容的值减小。影响了有些器件对高电容值的需求。

发明内容

本发明的目的在于提供一种PIP电容的制作方法,可以提高PIP电容的电容值。

为了达到上述目的,本发明提供了一种PIP电容的制作方法,包括:

提供衬底,所述衬底包括CELL区和PIP区;

在所述PIP区的衬底内形成第一浅沟槽隔离结构;

在刻蚀CELL区的衬底形成有源区的同时,刻蚀所述第一浅沟槽隔离结构形成第二浅沟槽隔离结构,第二浅沟槽隔离结构呈正弦波的形状;

在所述第二浅沟槽隔离结构上依次形成字线多晶硅、绝缘层和栅极多晶硅,所述字线多晶硅、绝缘层和栅极多晶硅均呈正弦波的形状。

可选的,在所述的PIP电容的制作方法中,形成第一浅沟槽隔离结构的方法包括:

在所述衬底上形成牺牲层;

刻蚀所述牺牲层和所述衬底形成浅沟槽;

向所述浅沟槽内填充氧化物,以形成第一浅沟槽隔离结构;

去除所述牺牲层。

可选的,在所述的PIP电容的制作方法中,刻蚀所述第一浅沟槽隔离结构的厚度为680埃~780埃。

可选的,在所述的PIP电容的制作方法中,正弦波的所述第二浅沟槽隔离结构的峰谷和峰顶的高度差为680埃~780埃。

可选的,在所述的PIP电容的制作方法中,所述第一部分至少为一个,所述第二部分至少为一个,所述第一部分和所述第二部分相邻并接触。

可选的,在所述的PIP电容的制作方法中,所述绝缘层的材料包括氧化物。

可选的,在所述的PIP电容的制作方法中,所述氧化物包括二氧化硅。

可选的,在所述的PIP电容的制作方法中,所述字线多晶硅的厚度为1710埃~2090埃。

可选的,在所述的PIP电容的制作方法中,所述绝缘层的厚度为140埃~160埃。

可选的,在所述的PIP电容的制作方法中,所述栅极多晶硅的厚度为1800埃~2200埃。

在本发明提供的PIP电容的制作方法中,包括:提供衬底,所述衬底包括CELL区和PIP区;在所述PIP区内形成第一浅沟槽隔离结构,刻蚀所述CELL区形成有源区的同时,刻蚀所述第一浅沟槽隔离结构形成第二浅沟槽隔离结构,所述第二浅沟槽隔离结构呈高低起伏的形状;在所述第二浅沟槽隔离结构上依次形成字线多晶硅、绝缘层和栅极多晶硅,所述字线多晶硅、绝缘层和栅极多晶硅均呈高低起伏的形状。本发明首先形成的第二浅沟槽隔离结构呈高低起伏的形状,导致后续在第二浅沟槽隔离结构上形成的字线多晶硅和栅极多晶硅均呈高低起伏的形状,增加了字线多晶硅和栅极多晶硅的相对面积,从而增加了电容值。并且,因为是和CELL区形成有源区的同时,在PIP区形成的第二浅沟槽隔离结构,不用采用额外的光罩和工艺步骤,节约成本。

附图说明

图1是现有技术的PIP电容的结构示意图;

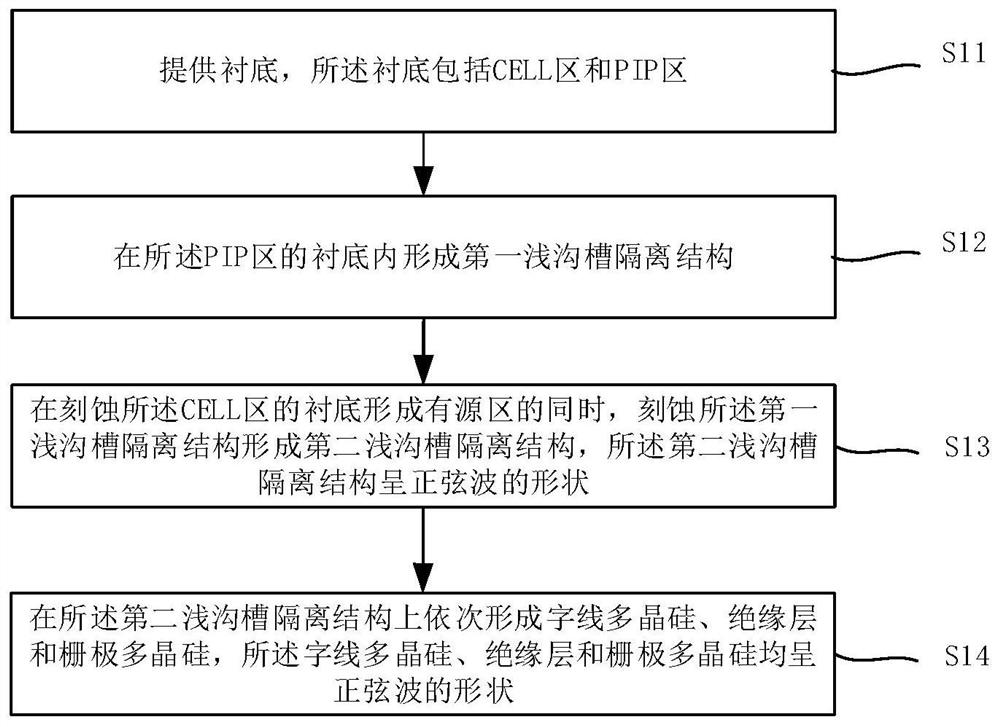

图2是本发明实施例的PIP电容的制作方法的流程图;

图3是本发明实施例的CELL区和PIP区划分的示意图

图4是本发明实施例的CELL区的有源区的示意图;

图5至图6是本发明实施例的PIP电容的制作方法的示意图;

图中:110-衬底、120-浅沟槽隔离结构、130-字线多晶硅、140-氧化物层、150-栅极多晶硅、210-衬底、220A-CELL区、220B-PIP区、220-第一浅沟槽隔离结构、230-第二浅沟槽隔离结构、240-字线多晶硅、250-绝缘层、260-栅极多晶硅、310-有源区。

具体实施方式

下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

请参照图2,本发明提供了一种PIP电容的制作方法,包括:

S11:提供衬底,所述衬底包括CELL区和PIP区;

S12:在所述PIP区的衬底内形成第一浅沟槽隔离结构;

S13:在刻蚀CELL区的衬底形成有源区的同时,刻蚀所述第一浅沟槽隔离结构形成第二浅沟槽隔离结构,第二浅沟槽隔离结构呈正弦波的形状;

S14:在所述第二浅沟槽隔离结构上依次形成字线多晶硅、绝缘层和栅极多晶硅,所述字线多晶硅、绝缘层和栅极多晶硅均呈正弦波的形状。

请参照图3,首先提供一衬底210,衬底210是P型衬底,将衬底210分为CELL区210A和PIP区210B,CELL区210A为器件区域,PIP区210B为电容区域,CELL区210A和PIP区210B不相邻,CELL区210A和PIP区210B可依据晶圆或芯片的版图设计来划分,其具体的位置关系及连接关系以产品的实际需求为准。

请参照图4,在PIP区210B的衬底210内以及衬底210上形成第一浅沟槽隔离结构220,第一浅沟槽隔离结构220的表面高于衬底210的表面,具体的形成方法可以是,先在衬底表面形成一牺牲层,牺牲层的材料为氧化物,刻蚀牺牲层和衬底210形成第一浅沟槽隔离结构220,最后去除牺牲层,这样第一浅沟槽隔离结构220的表面就高于衬底210的表面了。

请参照图5,由于会在CELL区210A的衬底210上形成器件,因此,CELL区210A的衬底210也在进行多个步骤以形成器件,例如,刻蚀衬底210形成有源区310和浅沟槽隔离结构,接着形成浮栅和控制栅等等,这里形成器件的步骤和方法为常规技术,在此不再赘述。

发明人发现,现有技术形成PIP电容的方法为,在衬底内形成浅沟槽隔离结构,在浅沟槽隔离结构上形成字线多晶硅作为电容的下级板、在字线多晶硅上形成氧化物层作为电容绝缘层、在氧化物层上形成栅极多晶硅,栅极多晶硅作为电容的上极板。但是随着电子产品的尺寸的减小,电容的尺寸也在减小,导致上极板和下级板的面积也再减小,最后使得制成的电容的值减小。影响了有些器件对高电容值的需求。PIP电容的字线多晶硅和栅极多晶硅之间的电容的计算方法为:C=E*S/d,其中:C为电容值,E为介电常数,S为字线多晶硅和栅极多晶硅相对的面积,d为字线多晶硅和栅极多晶硅之间的距离。因此,如果要增加电容值,要么增加字线多晶硅和栅极多晶硅的相对面积,要么减少字线多晶硅和栅极多晶硅之间的距离,而字线多晶硅和栅极多晶硅之间的距离也即是绝缘层的厚度,由于工艺的需求,存在无法继续减少厚度的可能,此时,可以从增加字线多晶硅和栅极多晶硅的相对面积来增加电容值。

因此,接下来,请参照图4至图6,发明人发现在CELL区210A形成有源区310的时候,可以改变第一浅沟槽隔离结构的形状从而改变字线多晶硅和栅极多晶硅的形状以增加电容值,并且不增加额外的掩膜板和工艺。具体的,在刻蚀所述CELL区210A形成有源区310的同时,刻蚀所述第一浅沟槽隔离结构220形成第二浅沟槽隔离结构230,第二浅沟槽隔离结构230呈正弦波的形状(高低起伏的形状);正弦波的所述第二浅沟槽隔离结构的峰谷和峰顶的高度差为680埃~780埃。由于CELL区210A会形成有源区310,同时在PIP区230B刻蚀第一浅沟槽隔离结构220形成第二浅沟槽隔离结构230,就不用额外增加掩膜板和刻蚀工艺,不会造成额外的工艺成本和时间。刻蚀所述第一浅沟槽隔离结构220形成第二浅沟槽隔离结构230的具体方法可以是,刻蚀第一浅沟槽隔离结构220的地方至少为一处,刻蚀停止在第一浅沟槽隔离结构220内,使得刻蚀后形成第二浅沟槽隔离结构230为正弦波的形状(高低起伏的形状)。如果将第二浅沟槽隔离结构高的部分作为第一部分,低的部分作为第二部分,则第一部分和第二部分均为至少一处,且第一部分位于衬底表面的高度高于第二部分位于衬底表面的高度,高的部分和低的部分相间设置,第一部分与第二部分相邻并接触,第二部分再与第一部分相邻并接触。也就是说在前面刻蚀第一浅沟槽隔离结构220时,如果刻蚀的大于或等于两处,则刻蚀地方两两不接触,且之间间隔一段距离。而刻蚀第一浅沟槽隔离结构的厚度可以为680埃~780埃。因此,第一部分位于衬底表面的高度高于第二部分位于衬底表面的高度,具体的高度高680埃~780埃。

接着,请继续参照图6,在所述第二浅沟槽隔离结构230上形成字线多晶硅240,字线多晶硅240的走势由于受到第二浅沟槽隔离结构230的形状的影响,所以字线多晶硅240也呈正弦波的形状(高低起伏的形状),增加了表面的面积。具体的,字线多晶硅240的上表面呈高低起伏的形状,下表面也呈高低起伏的形状,上表面和下表面的起伏的形状一致,因此,上表面和下表面在任何地方的距离都是相同的。所以字线多晶硅的厚度也是唯一的,具体的,字线多晶硅230的厚度为:1710埃~2090埃,例如,可以是1900埃。

接着,请继续参照图6,在字线多晶硅240上形成绝缘层250,绝缘层250的走势由于受到字线多晶硅240的形状的影响,所以绝缘层250也呈高低起伏的形状,具体的,绝缘层250的上表面呈正弦波的形状(高低起伏的形状),下表面也呈高低起伏的形状,上表面和下表面的起伏的形状一致,因此,上表面和下表面在任何地方的距离都是相同的。所以绝缘层250的厚度也是唯一的,具体的,绝缘层250的厚度为:140埃~160埃,例如,可以是780埃。进一步的,绝缘层250的材料包括氧化物,具体的可以为二氧化硅。

接着,请继续参照图6,在绝缘层250上形成栅极多晶硅260,栅极多晶硅260的走势由于受到绝缘层250的形状的影响,所以栅极多晶硅260也呈高低起伏的形状,增加了表面的面积。具体的,栅极多晶硅260的上表面呈高低起伏的形状,下表面也正弦波的形状(高低起伏的形状),上表面和下表面的起伏的形状一致,因此,上表面和下表面在任何地方的距离都是相同的。所以栅极多晶硅260的厚度也是唯一的,具体的,栅极多晶硅260的厚度为:1800埃~2200埃,例如,可以是2000埃。这样,字线多晶硅240的上表面的面积增加,栅极多晶硅260的下表面的面积增加,字线多晶硅240和栅极多晶硅260之间的相对面积增加,绝缘层250的厚度不变,根据C=E*S/d可以得知本发明实施例的PIP电容的制作方法可以提高电容值。在C=E*S/d中:C为电容值,E为介电常数,S为字线多晶硅240和栅极多晶硅260相对的面积,d为字线多晶硅240和栅极多晶硅260之间的距离即绝缘层250的厚度。

综上,在本发明实施例提供的PIP电容的制作方法中,包括:提供衬底,所述衬底包括CELL区和PIP区;在所述PIP区内形成第一浅沟槽隔离结构,刻蚀所述CELL区形成有源区的同时,刻蚀所述第一浅沟槽隔离结构形成第二浅沟槽隔离结构,所述第二浅沟槽隔离结构呈高低起伏的形状;在所述第二浅沟槽隔离结构上依次形成字线多晶硅、绝缘层和栅极多晶硅,所述字线多晶硅、绝缘层和栅极多晶硅均呈高低起伏的形状。本发明首先形成的第二浅沟槽隔离结构呈高低起伏的形状,导致后续在第二浅沟槽隔离结构上形成的字线多晶硅和栅极多晶硅均呈高低起伏的形状,增加了字线多晶硅和栅极多晶硅的相对面积,从而增加了电容值。并且,因为是和CELL区形成有源区的同时,在PIP区形成的第二浅沟槽隔离结构,不用采用额外的光罩和工艺步骤,节约成本。

上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍属于本发明的保护范围之内。

- PIP电容器的制作方法、PIP电容器及EEPROM存储单元

- PIP电容的制作方法