半导体组件

文献发布时间:2023-06-19 12:07:15

技术领域

本发明是关于半导体组件,尤其是关于半导体组件的绕线结构。

背景技术

图1为半导体结构,在垂直方向(z方向)上由下往上依序包含基板110、氧化层120、金属层130、氧化层135,以及金属层140。金属层130可以是超厚金属(ultra-thick metal,UTM)层,而金属层140可以是重布线层(re-distribution layer,RDL)。氧化层120可以包含其他的金属层(图未示)。一般来说,超厚金属层的阻值小于重布线层的阻值,而氧化层120中的金属层的阻值约为超厚金属层的阻值的数十倍。

半导体组件常包含交叉的走线(trace),而交叉的走线势必制作于复数个金属层上。图2显示习知的半导体组件的局部绕线。走线210、走线220及走线230互相交叉。走线210位于上层的金属层(例如图1的金属层140),走线220位于中间的金属层(例如图1的金属层130),而走线230位于下层的金属层(例如图1的氧化层120中的金属层)。由于氧化层120中的金属层的阻值较高,所以走线230必须做得比较宽才能承受高电流。然而较宽的走线会增加寄生电容,造成半导体组件的特性变差。

发明内容

鉴于先前技术的不足,本发明之一目的在于提供一种半导体组件,以减少导体层的使用。

本发明揭露一种半导体组件,包含一第一走线、一第二走线以及一第三走线。第一走线包含依序连接的一第一线段、一第二线段及一第三线段。第二走线包含依序连接的一第四线段、一第五线段、一第六线段、一第七线段及一第八线段。第三走线包含依序连接的一第九线段、一第十线段及一第十一线段。该第一线段、该第四线段及该第九线段实质上平行,该第三线段、该第八线段及该第十一线段实质上平行。该第二线段与该第十线段及该第七线段交叉,该第五线段与该第十线段交叉。该第一走线、该第二走线及该第三走线各为连续且等电位的走线。

本发明另揭露一种半导体组件,包含一第一走线、一第二走线以及一第三走线。该第一走线、该第二走线及该第三走线各为连续且等电位的走线。该第一走线、该第二走线及该第三走线仅使用一半导体结构的二导体层。于该第一走线、该第二走线及该第三走线的一交叉区间内,该第一走线与该第二走线交叉一次,该第一走线与该第三走线交叉一次,且该第二走线与该第三走线交叉一次。

本发明另揭露一种半导体组件,该半导体组件具有包含一第一层、一第二层及一第三层的一层状结构。半导体组件包含一第一走线、一第二走线及一第三走线。第一走线由该第一层延伸至该第三层,且包含位于该第一层及该第三层之间但不属于该第一层及该第三层的一第一连续线段。第二走线由该第二层经该第三层延伸至该第二层,且包含不属于该第一层及该第二层的一第二连续线段。第三走线由该第三层延伸至该第一层,且包含位于该第一层及该第三层之间但不属于该第一层及该第三层的一第三连续线段。该第一走线、该第二走线及该第三走线各为连续且等电位的走线。该第一走线、该第二走线及该第三走线仅使用一半导体结构的二导体层。该第一连续线段与该第二连续线段及该第三连续线段交叉,且该第二连续线段与该第三连续线段交叉。

本发明另揭露一种半导体组件,包含一第一走线、一第二走线、一第三走线以及一第四走线。该第一走线、该第二走线、该第三走线及该第四走线各为连续且等电位的走线。该第一走线、该第二走线、该第三走线及该第四走线仅使用一半导体结构的二导体层。于该第一走线、该第二走线、该第三走线及该第四走线的一交叉区间内,该第一走线与该第二走线交叉一次,该第一走线与该第三走线交叉一次,该第一走线与该第四走线交叉一次,该第二走线与该第四走线交叉一次,且该第三走线与该第四走线交叉一次。

本发明的半导体组件能够使用少量的导体层来完成绕线。相较于传统技术,本发明的半导体组件可以避免使用阻值较高的导体层,以提高半导体组件的特性。

有关本发明的特征、实作与功效,兹配合图式作实施例详细说明如下。

附图说明

图1为半导体结构;

图2为习知的半导体组件的局部绕线;

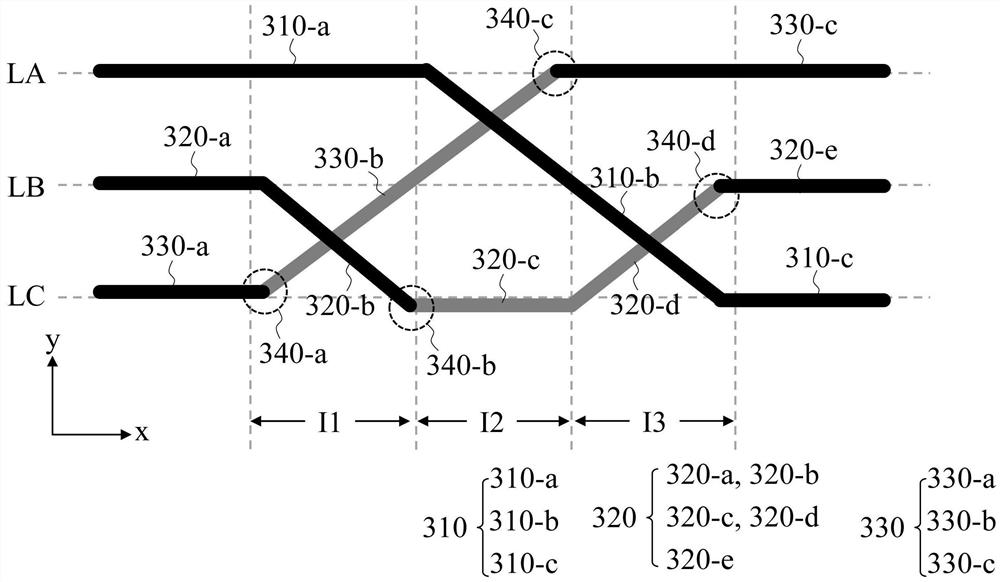

图3为本发明一实施例的半导体组件的局部绕线;

图4为本发明一实施例的半导体组件的结构图;

图5为本发明另一实施例的半导体组件的结构图;

图6为本发明另一实施例的半导体组件的局部绕线;

图7为本发明另一实施例的半导体组件的结构图;以及

图8为图3的半导体组件的局部绕线的等效结构。

具体实施方式

以下说明内容的技术用语是参照本技术领域的习惯用语,如本说明书对部分用语有加以说明或定义,该部分用语的解释是以本说明书的说明或定义为准。

本发明的揭露内容包含半导体组件。由于本发明的半导体组件所包含的部分组件单独而言可能为已知组件,因此在不影响该装置发明的充分揭露及可实施性的前提下,以下说明对于已知组件的细节将予以节略。

图3显示本发明一实施例的半导体组件的局部绕线。图3为半导体组件的俯视图。半导体组件的局部绕线包含走线310(包含依序连接的线段310-a、线段310-b及线段310-c)、走线320(包含依序连接的线段320-a、线段320-b、线段320-c、线段320-d及线段320-e),以及走线330(包含依序连接的线段330-a、线段330-b及线段330-c)。图中黑色线段制做于半导体结构的第一导体层,而灰色线段制做于半导体结构的第二导体层。第一导体层可以是超厚金属层及重布线层的其中一者,而第二导体层是另一者。不同导体层的线段藉由贯穿位置340-a、340-b、340-c及340-d上的贯穿结构(例如导孔(via)或导孔数组)连接。因此,虽然每一条走线(走线310、320或330)可能包含位于不同导体层的线段,但每一条走线为连续且等电位的走线。

本发明的半导体组件在图1所示的x-y平面上为层状结构,包含图3所示的LA层、LB层及LC层。线段310-a及线段330-c位于LA层,且线段310-a的延伸通过线段330-c,反之亦然;线段320-a及线段320-e位于LB层,且线段320-a的延伸通过线段320-e,反之亦然;线段330-a及线段310-c位于LC层,且线段330-a的延伸通过线段310-c,反之亦然。

线段310-b为连接线段310-a及线段310-c的连续线段,线段310-b位于LA层及LC层之间,但不属于LA层及LC层。线段320-b、线段320-c及线段320-d共同构成连接线段320-a及线段320-e的连续线段,该连续线段(即线段320-b、线段320-c及线段320-d)不属于LA层及LB层。线段330-b为连接线段330-a及线段330-c的连续线段,线段330-b位于LA层及LC层之间,但不属于LA层及LC层。

图3标示区间I1、区间I2及区间I3等三个区间(三者共同构成交叉区间),走线310、走线320及走线330在交叉区间以外的部分实质上互相平行。更明确地说,线段310-a、线段320-a及线段330-a实质上互相平行,而线段330-c、线段320-e及线段310-c实质上互相平行。在交叉区间中,走线310与走线320交叉一次、走线310与走线330交叉一次,且走线320与走线330交叉一次。更明确地说,走线320进入交叉区间后先在区间I1内经由线段320-b走(trace)至位于区间I2且属于LB层的线段320-c,再在区间I3中经由线段320-d走至属于LB层的线段320-e。走线330进入交叉区间后经由线段330-b走至线段330-c。在区间I1中线段320-b与线段330-b交叉(即走线320与走线330交叉)。走线310进入交叉区间后先延伸一段距离(即区间I1的长度),再经由线段310-b走至线段310-c。在区间I2中线段310-b与线段330-b交叉(即走线310与走线330交叉),且在区间I3中线段310-b与线段320-d交叉(即走线310与走线320交叉)。

如图3所示,本发明的半导体组件仅使用半导体结构中的两层导体层即实现三条走线的互相交叉,这样的结构可以避免半导体组件制作于阻值较高的导体层,因此可以提升半导体组件的特性。

图4为本发明一实施例的半导体组件的结构图。半导体组件400为一个三圈的电感(即半导体组件400为层状结构),包含端点401及端点402。介于框选范围410及框选范围420中间的线段属于电感的第一圈,介于框选范围420及框选范围430中间的线段属于电感的第二圈,而位于框选范围430内的线段属于电感的第三圈。第二圈位于第一圈及第三圈的间。同时参阅图3及图4,当图3的结构应用于半导体组件400时,走线310连接半导体组件400的第一圈及第三圈,走线330连接半导体组件400的第三圈及第一圈,且走线320连接半导体组件400的第二圈。换言之,LA层对应半导体组件400的第一圈,LB层对应半导体组件400的第二圈,以及LC层对应半导体组件400的第三圈。

图5为本发明另一实施例的半导体组件的结构图。半导体组件500为一个变压器,包含第一电感及第二电感。第一电感以端点501及端点502为端点,第二电感以端点503及端点504为端点。半导体组件500包含从外到内依序排列的第一圈、第二圈、第三圈及第四圈,换言之,半导体组件500是一个层状结构。第一圈及第三圈属于第一电感,而第二圈及第四圈属于第二电感。图中黑色线段制做于半导体结构的第一导体层,深灰色线段制做于半导体结构的第二导体层,而与端点504直接连接的浅灰色线段则制作于半导体结构的第三导体层,第三导体层不同于第一导体层及第二导体层。

同时参阅图3及图5,当图3的结构应用于半导体组件500时,走线310连接半导体组件500的第一圈及第三圈(也就是连接第一电感的外圈与内圈)、走线320连接半导体组件500的第二圈(也就是连接第二电感的外圈);走线330连接半导体组件500的第一圈及第三圈(也就是连接第一电感的外圈与内圈)。换言之,LA层对应半导体组件500的第一圈,LB层对应半导体组件500的第二圈,以及LC层对应半导体组件500的第三圈。

图6显示本发明另一实施例的半导体组件的局部绕线。图6为半导体组件的俯视图。半导体组件的局部绕线包含走线610(包含依序连接的线段610-a、线段610-b及线段610-c)、走线620(包含依序连接的线段620-a、线段620-b、线段620-c、线段620-d及线段620-e)、走线630(包含依序连接的线段630-a、线段630-b、线段630-c、线段630-d及线段630-e),以及走线640(包含依序连接的线段640-a、线段640-b及线段640-c)。虽然每一条走线(走线610、620、630或640)可能包含位于不同导体层的线段,但每一条走线为连续且等电位的走线。

本发明的半导体组件在图1所示的x-y平面上为层状结构,包含图中所示的LA层、LB层、LC层及LD层。线段610-a及线段640-c位于LA层,且线段610-a的延伸通过线段640-c,反之亦然;线段620-a及线段620-e位于LB层,且线段620-a的延伸通过线段620-e,反之亦然;线段630-a及线段630-e位于LC层,且线段630-a的延伸通过线段630-e,反之亦然;线段640-a及线段610-c位于LD层,且线段640-a的延伸通过线段610-c,反之亦然。

线段610-b为连接线段610-a及线段610-c的连续线段,线段610-b位于LA层及LD层之间,但不属于LA层及LD层。线段620-b、线段620-c及线段620-d共同构成连接线段620-a及线段620-e的连续线段,该连续线段(即线段620-b、线段620-c及线段620-d)不属于LB层、LC层及LD层。线段630-b、线段630-c及线段630-d共同构成连接线段630-a及线段630-e的连续线段,该连续线段(即线段630-b、线段630-c及线段630-d)不属于LA层、LB层及LC层。线段640-b为连接线段640-a及线段640-c的连续线段,线段640-b位于LA层及LD层之间,但不属于LA层及LD层。

图6标示区间I1、区间I2及区间I3等三个区间(三者共同构成交叉区间),走线610、走线620、走线630及走线640在交叉区间以外的部分实质上互相平行。更明确地说,线段610-a、线段620-a、线段630-a及线段640-a实质上互相平行,而线段640-c、线段620-e、线段630-e及线段610-c实质上互相平行。在交叉区间中,走线610与走线620、走线630及走线640分别交叉一次,且走线640与走线620及走线630分别交叉一次。更明确地说,走线610进入交叉区间后经由线段610-b走至线段610-c。走线620进入交叉区间后先在区间I1内经由线段620-b走至位于区间I2且属于LA层的线段620-c,再在区间I3中经由线段620-d走至属于LB层的线段620-e。走线630进入交叉区间后先在区间I1内经由线段630-b走至位于区间I2且属于LD层的线段630-c,再在区间I3中经由线段630-d走至属于LC层的线段630-e。走线640进入交叉区间后经由线段640-b走至线段640-c。在区间I1中线段610-b与线段620-b交叉(即走线610与走线620交叉)且线段630-b与线段640-b交叉(即走线630与走线640交叉)。在区间I2中线段610-b与线段640-b交叉(即走线610与走线640交叉)。在区间I3中线段620-d与线段640-b交叉(即走线620与走线640交叉)且线段630-d与线段610-b交叉(即走线630与走线610交叉)。

图6的绕线仅使用半导体结构中的两层导体层,这样的结构可以避免半导体组件制作于阻值较高的导体层,因此可以提升半导体组件的特性。

图7为本发明另一实施例的半导体组件的结构图。半导体组件700为一个变压器,包含第一电感及第二电感。第一电感以端点701及端点702为端点,第二电感以端点703及端点704为端点。半导体组件700包含从外到内依序排列的第一圈、第二圈、第三圈及第四圈,换言之,半导体组件700是一个层状结构。第一圈及第四圈属于第一电感,而第二圈及第三圈属于第二电感。

同时参阅图6及图7,当图6的结构应用于半导体组件700时,走线610连接半导体组件700的第一圈及第四圈(也就是连接第一电感的外圈与内圈),走线620连接半导体组件700的第二圈(也就是连接第二电感的外圈),走线630连接半导体组件700的第三圈(也就是连接第二电感的内圈),且走线640连接半导体组件700的第一圈及第四圈(也就是连接第一电感的外圈与内圈)。换言之,LA层对应半导体组件700的第一圈,LB层对应半导体组件700的第二圈,LC层对应半导体组件700的第三圈,以及LD层对应半导体组件700的第四圈。

图8为图3的半导体组件的局部绕线的等效结构。在本实施例中,线段320-f(上层的黑色线段)对应线段320-b及线段320-c所组成的连续线段,而线段320-g(下层的灰色线段)对应线段320-d及线段320-e所组成的连续线段。

由于本技术领域具有通常知识者可藉由本案的装置发明的揭露内容来了解本案的方法发明的实施细节与变化,因此,为避免赘文,在不影响该方法发明的揭露要求及可实施性的前提下,重复的说明在此予以节略。请注意,前揭图标中,组件的形状、尺寸、比例、层数以及圈数等仅为示意,是供本技术领域具有通常知识者了解本发明之用,非用以限制本发明。

虽然本发明的实施例如上所述,然而该些实施例并非用来限定本发明,本技术领域具有通常知识者可依据本发明的明示或隐含的内容对本发明的技术特征施以变化,凡此种种变化均可能属于本发明所寻求的专利保护范畴,换言之,本发明的专利保护范围须视本说明书的申请专利范围所界定者为准。

【符号说明】

110 基板

120、135 氧化层

130、140 金属层

210、220、230、310、320、330、610、620、630、640 走线

310-a、310-b、310-c、320-a、320-b、320-c、320-d、320-e、330-a、330-b、330-c、610-a、610-b、610-c、620-a、620-b、620-c、620-d、620-e、630-a、630-b、630-c、630-d、630-e、640-a、640-b、640-c、320-f、320-g 线段

340-a、340-b、340-c、340-d 贯穿位置

LA、LB、LC、LD 层

I1、I2、I3 区间

400、500、700 半导体组件

401、402、501、502、503、504、701、702、703、704端点410、420、420、430 框选范围。

- 半导体组件用冷却器的制造方法、半导体组件用冷却器、半导体组件和电驱动车辆

- 半导体组件制造方法、半导体组件及半导体组件制造设备