集成电路芯片引脚的性能分析方法、装置、设备及介质

文献发布时间:2023-06-19 12:10:19

技术领域

本发明涉及计算机辅助工程技术领域,特别是涉及一种集成电路芯片引脚的性能分析方法、装置、设备及介质。

背景技术

集成电路芯片引脚是从集成电路芯片内部电路引出与外围电路的接线,所有的引脚就构成了这块芯片的接口。引线末端的一段,通过软钎焊使这一段与印制板上的焊盘共同形成焊点。此种引脚结构设计当前在集成电路芯片领域有着非常广泛的应用,因此此种设计的结构力学可靠性成为了相应芯片性能可靠度的重要组成部分。目前,在电子产品的结构设计环节,评估集成电路芯片引脚结构在跌落、冲击等不当使用工况下的结构力学可靠性就成为了研发过程中必不可少的步骤。

在现有技术中,一般是采用产品整体可靠性测试试验来分析评估集成电路芯片引脚结构在多种使用工况下的结构力学可靠性问题。这样做费时费力,显著增加了企业的研发成本和研发周期。

因此,如何高效率、低成本地评估集成电路芯片引脚在不同工况下是否存在结构失效的问题,是本领域技术人员亟待解决的技术问题。

发明内容

有鉴于此,本发明的目的在于提供一种集成电路芯片引脚的性能分析方法、装置、设备及介质,无需多次测试,可以有效地提高研发效率,降低研发成本,缩短研发周期。其具体方案如下:

一种集成电路芯片引脚的性能分析方法,包括:

将印制电路板和集成电路芯片的几何数据导入有限元建模软件中,建立有限元模型;

对印制电路板和集成电路芯片的主体部分进行有限元网格划分,使集成电路芯片的每个引脚处均有网格节点;

在每个引脚位置建立梁单元并设置相关接触关系失效参数;

完成所述有限元模型中包含赋予材料和属性、设置部件间连接关系和接触关系的建模内容,并根据分析工况设置约束参数及载荷参数;

对所述有限元模型进行运算分析,并根据运算分析结果判断集成电路芯片引脚是否满足结构力学相关性能要求。

优选地,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,在建立有限元模型之前,还包括:

根据预先存储的简化规则对所述几何数据进行简化。

优选地,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,所述网格划分包括占据部件轴线位置的一维梁单元网格划分、占据部件中面位置的二维壳单元网格划分和占据部件空间位置的三维体单元网格划分。

优选地,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,所述接触关系失效参数包括法向受力失效参数和切向受力失效参数。

优选地,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,赋予材料和属性、设置部件间连接关系和接触关系,具体包括:

赋予各个部件弹塑性材料参数或刚性材料参数;

赋予各个部件厚度信息和网格单元数学本构属性;

设置部件间无相对运动的刚性连接关系和有相对运动自由度的接头连接关系;

设置部件间无相对穿透的部件接触关系和无相对运动的约束接触关系。

优选地,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,所述约束参数包括约束所述有限元模型整体运动自由度的参数;

所述载荷参数包括施加非自身激励产生的外来作用的参数。

优选地,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,在对所述有限元模型进行运算分析之前,还包括:

设置所述有限元模型计算公式控制参数、时间步长参数和结果输出参数。

本发明实施例还提供了一种集成电路芯片引脚的性能分析装置,包括:

数据导入模块,用于将印制电路板和集成电路芯片的几何数据导入有限元建模软件中,建立有限元模型;

网格划分模块,用于对印制电路板和集成电路芯片的主体部分进行有限元网格划分,使集成电路芯片的每个引脚处均有网格节点;

参数设置模块,用于在每个引脚位置建立梁单元并设置相关接触关系失效参数,还用于完成所述有限元模型中包含赋予材料和属性、设置部件间连接关系和接触关系的建模内容,并根据分析工况设置约束参数及载荷参数;

性能分析模块,用于对所述有限元模型进行运算分析,并根据运算分析结果判断集成电路芯片引脚是否满足结构力学相关性能要求。

本发明实施例还提供了一种集成电路芯片引脚的性能分析设备,包括处理器和存储器,其中,所述处理器执行所述存储器中保存的计算机程序时实现如本发明实施例提供的上述集成电路芯片引脚的性能分析方法。

本发明实施例还提供了一种计算机可读存储介质,用于存储计算机程序,其中,所述计算机程序被处理器执行时实现如本发明实施例提供的上述集成电路芯片引脚的性能分析方法。

从上述技术方案可以看出,本发明所提供的一种集成电路芯片引脚的性能分析方法,包括:将印制电路板和集成电路芯片的几何数据导入有限元建模软件中,建立有限元模型;对印制电路板和集成电路芯片的主体部分进行有限元网格划分,使集成电路芯片的每个引脚处均有网格节点;在每个引脚位置建立梁单元并设置相关接触关系失效参数;完成有限元模型中包含赋予材料和属性、设置部件间连接关系和接触关系的建模内容,并根据分析工况设置约束参数及载荷参数;对有限元模型进行运算分析,并根据运算分析结果判断集成电路芯片引脚是否满足结构力学相关性能要求。

本发明通过方便快速地建立用于集成电路芯片引脚分析的有限元模型,可以快速得到集成电路芯片引脚结构力学性能的数值分析结果,高效率、低成本地评估当前版本整体设计方案是否会导致集成电路芯片引脚结构在各个工况下产生结构可靠性问题,免去了生产试验试制件和进行试验测试的环节,无需进行多轮测试,有效地提高了研发效率,降低了研发成本,缩短了研发周期。另外,本发明采用的梁单元建模方式,相比于体单元建模,在保留合理精度的基础上,更快捷方便,节约时间。此外,本发明还针对集成电路芯片引脚的性能分析方法提供了相应的装置、设备及计算机可读存储介质,进一步使得上述方法更具有实用性,该装置、设备及计算机可读存储介质具有相应的优点。

附图说明

为了更清楚地说明本发明实施例或相关技术中的技术方案,下面将对实施例或相关技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

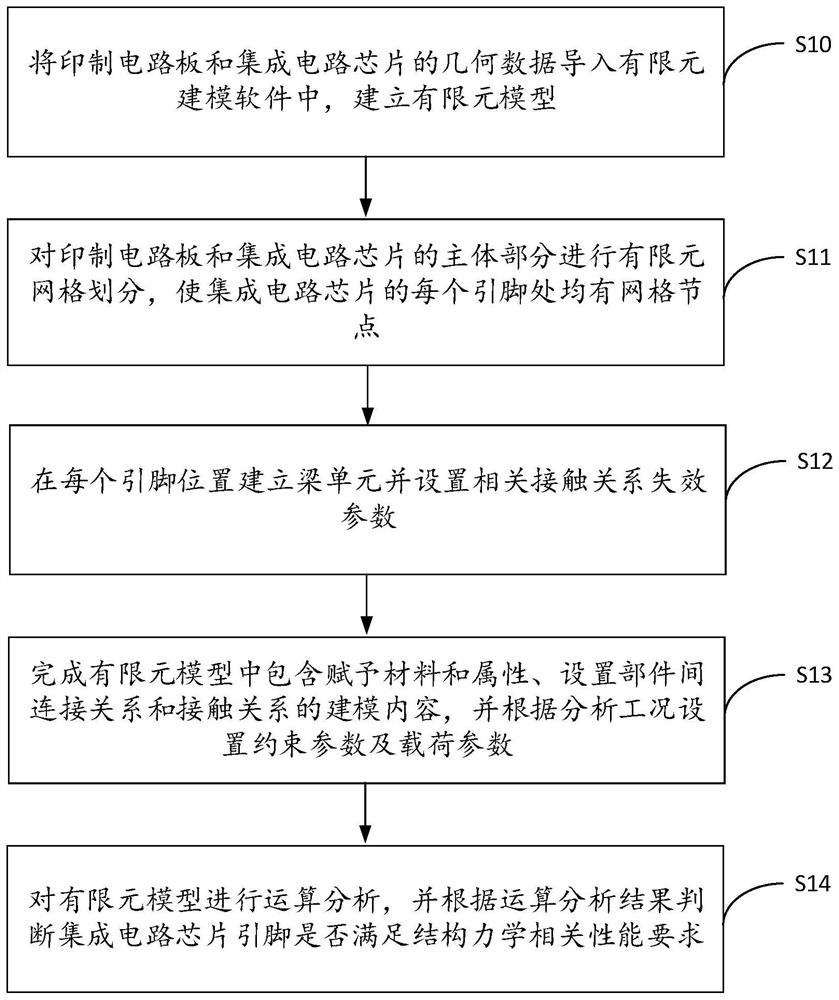

图1为本发明实施例提供的集成电路芯片引脚的性能分析方法的流程图;

图2为本发明实施例提供的集成电路芯片引脚的性能分析装置的结构示意图;

图3为本发明实施例提供的集成电路芯片引脚的性能分析设备的结构示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明提供一种集成电路芯片引脚的性能分析方法,如图1所示,包括以下步骤:

S10、将印制电路板和集成电路芯片的几何数据导入有限元建模软件中,建立有限元模型;

在实际应用中,印制电路板是电子元器件电气连接的提供者,而集成电路芯片包括一硅基板、至少一电路、一固定封环、一接地环及至少一防护环的电子元件。两者间通过引脚连接。几何数据为按照一定比例或与实物大小一致的三维模型,可采用任何一种制图软件来绘制,例如CATIA。有限元建模软件可以是Altair HyperMesh,其为新一代3D高效率建模软件,在国际工业领域得到了广泛的应用;

S11、对印制电路板和集成电路芯片的主体部分进行有限元网格划分,使集成电路芯片的每个引脚处均有网格节点;

在实际应用中,网格划分是把有限元模型分成很多小的单元,其生成的网格质量好坏,将决定后续分析结果的质量。引脚是从集成电路芯片内部电路引出与外围电路的接线,所有的引脚就构成了这块芯片的接口。引线末端的一段,通过软钎焊使这一段与印制板上的焊盘共同形成焊点。具体地,网格划分可以包括占据部件轴线位置的一维梁单元网格划分、占据部件中面位置的二维壳单元网格划分和占据部件空间位置的三维体单元网格划分,即网格节点是占据部件轴线位置的一维梁单元、占据部件中面位置的二维壳单元和占据部件空间位置的三维体单元的其中一个端点;其中,壳单元以正四边形为佳,体单元以正六面体为佳。最终生成的网格单元需要恰当地表达了原几何模型的空间位置,并且网格单元质量满足一定的检查条件;

S12、在每个引脚位置建立梁单元并设置相关接触关系失效参数;

需要说明的是,接触关系是在两个或多个有限元部件之间互相接触时定义力和位移的传递关系;接触关系失效参数是定义在两个或多个有限元部件之间作用力达到某个预设条件时,接触关系如何变化的参数;

在实际应用中,梁单元的一端与引脚引出位置共节点,另一端与印制电路板表面共平面。梁单元共平面的端点和印制电路板单元的接触关系可以采用LS-DYNA求解器格式中CONTACT_TIEBREAK_NODES_TO_SURFACE命令定义。接触关系失效参数包括法向受力失效参数和切向受力失效参数,可以采用相应命令下NFLF、SFLF、NEN及MES选项来定义法向失效力、切向失效力、法向失效力指数和切向失效力指数。当

S13、完成有限元模型中包含赋予材料和属性、设置部件间连接关系和接触关系的建模内容,并根据分析工况设置约束参数及载荷参数;

需要说明的是,材料是与部件尺寸或约束无关的力学性能参数的集合;属性是定义部件维度、尺寸、数学本构公式参数的集合;部件间的连接关系和接触关系都定义了相关网格单元之间力和位移的传递关系,其中连接关系包括无相对运动的刚性连接和有相对运动自由度的接头连接,接触关系包括无相对穿透的部件接触关系和无相对运动的约束接触关系。分析工况是对真实使用环境或测试试验条件的定义,包括正常情况和严苛情况。约束参数及载荷参数,即边界条件,是指在模型求解区域边界上所求解的变量或其导数随时间和地点变化规律的参数;

S14、对有限元模型进行运算分析,并根据运算分析结果判断集成电路芯片引脚是否满足结构力学相关性能要求;

需要说明的是,运算分析是求解器对已经完成的有限元模型文件进行计算并求得数值解作为计算结果的过程,可以采用ANSYS LS-DYNA求解器进行求解。上述步骤可以先依据各求解参数对有限元模型求解得到目标集成电路芯片引脚的结构力学性能数值计算结果,然后将目标数值计算结果与部件设计要求的结构力学性能要求进行比较以确定部件的结构力学性能是否符合要求。

在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,通过方便快速地建立用于集成电路芯片引脚分析的有限元模型,可以快速得到集成电路芯片引脚结构力学性能的数值分析结果,高效率、低成本地评估当前版本整体设计方案是否会导致集成电路芯片引脚结构在各个工况下产生结构可靠性问题,免去了生产试验试制件和进行试验测试的环节,无需进行多轮测试,有效地提高了研发效率,降低了研发成本,缩短了研发周期。另外,本发明采用的梁单元建模方式,相比于体单元建模,在保留合理精度的基础上,更快捷方便,节约时间。

由于一般在研发过程中,设计师会根据开发需求生成或导入包含全部细节特征的几何数据,然后交给分析工程师进行性能评估分析,整体计算过程家较为复杂。为了简化后续的计算过程,在具体实施时,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,步骤S10中,在建立有限元模型之前,还可以包括:根据预先存储的简化规则对几何数据进行简化。其中,简化规则是将对分析结果影响较小的细节特征和部件简化,但是保留对分析结果有显著影响的重要特征。得到初步简化几何数据后,对简化几何数据进行适当地修正以使其便于生成网格单元,可得到简化几何模型,即简化后的有限元模型。

在具体实施时,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,步骤S13中赋予材料和属性、设置部件间连接关系和接触关系,具体可以包括:赋予各个部件弹塑性材料参数或刚性材料参数;赋予各个部件厚度信息和网格单元数学本构属性;设置部件间无相对运动的刚性连接关系和有相对运动自由度的接头连接关系;设置部件间无相对穿透的部件接触关系和无相对运动的约束接触关系。

具体地,在LS-DYNA求解器格式中,弹塑性部件可以选择MAT_024材料卡,焊点部件可以选择MAT_100材料卡,刚性部件可以选择MAT_020材料卡。部件属性卡可以选择线性本构类型来节约计算资源。刚性连接关系可通过CONSTRAINED_NODAL_RIGID_BODY及SET_NODE_LIST关键字实现,或者通过建立刚性部件及CONSTRAINED_RIGID_BODIES关键字实现。接头连接关系可以通过CONSTRAINED_JOINT_XXX关键字实现。部件接触关系可以通过CONTACT_AUTOMATIC_SINGLE_SURFACE_ID及SET_PART_LIST关键字实现。约束接触关系可以通过CONTACT_TIED_NODES_TO_SURFACE、SET_NODE_LIST及SET_PART_LIST关键字实现。

在具体实施时,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,步骤S13中设置的约束参数可以包括约束有限元模型整体运动自由度的参数;载荷参数可以包括施加非自身激励产生的外来作用的参数。具体地,约束参数可以通过BOUNDARY_SPC关键字实现。载荷参数可以通过BOUNDARY_PRESCRIBED_MOTION关键字实现。

在具体实施时,在本发明实施例提供的上述集成电路芯片引脚的性能分析方法中,为了保证得到正确的计算结果,在执行步骤S14对有限元模型进行运算分析之前,还可以包括:设置公式控制参数、时间步长参数和结果输出参数等求解参数。公式控制参数用于设定计算所使用的公式及相关变量,时间步长参数用于设定计算时间,结果输出参数用于设定需要输出的变量值,如位移形变、速度加速度、应力应变等。结构力学相关性能要求是结构安全性、适用性和耐久性的综合体现,包括在各种设计工况下集成电路芯片引脚不应产生弯折变形,开裂脱落等情况;

具体地,在LS-DYNA求解器格式中,公式控制参数和时间步长参数可以通过CONTROL_XXX关键字实现,结果输出参数可以通过DATABASE_XXX关键字实现。如果运算分析结果显示在某个设计工况下,引脚的应力应变未超过相应的预设值,或者连接位置各方向受力未超过相应的预设值,则判断在此工况下集成电路芯片引脚满足结构力学相关性能要求,反之则为不满足。还需要说明的是,S10-S40中涉及到的有限元模型格式要与S50中的求解器所需求的格式相匹配,举例来说,若采用LS-DYNA求解器来计算有限元模型,则模型文件的格式应为LS-DYNA求解器所要求的.k格式。

基于同一发明构思,本发明实施例还提供了一种集成电路芯片引脚的性能分析装置,由于该装置解决问题的原理与前述一种集成电路芯片引脚的性能分析方法相似,因此该装置的实施可以参见集成电路芯片引脚的性能分析方法的实施,重复之处不再赘述。

在具体实施时,本发明实施例提供的集成电路芯片引脚的性能分析装置,如图2所示,具体包括:

数据导入模块20,用于将印制电路板和集成电路芯片的几何数据导入有限元建模软件中,建立有限元模型;该数据导入模块20具体可以用于将印制电路板和集成电路芯片(即目标部件)的几何数据导入预先构建的建模程序中以预制的简化规则建立简化后的有限元模型;

网格划分模块21,用于对印制电路板和集成电路芯片的主体部分进行有限元网格划分,使集成电路芯片的每个引脚处均有网格节点;该网格划分模块21具体可以用于对简化后的有限元模型进行一维、二维和三维单元的网格划分;

参数设置模块22,用于在每个引脚位置建立梁单元并设置相关接触关系失效参数,还用于完成有限元模型中包含赋予材料和属性、设置部件间连接关系和接触关系的建模内容,并根据分析工况设置约束参数及载荷参数;该参数设置模块22具体可以用于设置材料参数、属性参数、连接参数、接触参数、失效参数、约束参数和载荷参数等各个相关必要参数;

性能分析模块23,用于对有限元模型进行运算分析,并根据运算分析结果判断集成电路芯片引脚是否满足结构力学相关性能要求;该性能分析模块23具体可以用于依据所述求解参数对有限元模型求解得到集成电路芯片引脚的结构力学性能数值计算结果,将目标数值计算结果与部件设计要求的结构力学性能要求进行比较以确定部件的结构力学性能是否符合要求。

在本发明实施例提供的上述集成电路芯片引脚的性能分析装置中,可以通过上述四个模块的相互作用,可方便快速地建立集成电路芯片引脚分析模型,高效率低成本地评估了当前版本整体设计方案是否会导致集成电路芯片引脚结构在各个工况下产生结构可靠性问题,免去了生产试验试制件和进行试验测试的环节,有效地提高研发效率,降低研发成本,缩短研发周期。

关于上述各个模块更加具体的工作过程可以参考前述实施例公开的相应内容,在此不再进行赘述。

相应的,本发明实施例还公开了一种集成电路芯片引脚的性能分析设备,如图3所示,包括存储器30和处理器31;其中,处理器31执行存储器30中保存的计算机程序时实现前述实施例公开的集成电路芯片引脚的性能分析方法。

其中,存储器30可以包括一个或多个计算机可读存储介质,该计算机可读存储介质可以是非暂态的。存储器30还可包括高速随机存取存储器,以及非易失性存储器,比如一个或多个磁盘存储设备、闪存存储设备。本实施例中,存储器30至少用于存储以下计算机程序301,其中,该计算机程序被处理器31加载并执行之后,能够实现前述任一实施例公开的集成电路芯片引脚的性能分析方法的相关步骤。另外,存储器30所存储的资源还可以包括操作系统302和数据303等,存储方式可以是短暂存储或者永久存储。其中,操作系统302可以包括Windows、Unix、Linux等。数据303可以包括但不限于测试结果对应的数据等。

处理器31可以包括一个或多个处理核心,比如4核心处理器、8核心处理器等。处理器31可以采用DSP(Digital Signal Processing,数字信号处理)、FPGA(Field-Programmable Gate Array,现场可编程门阵列)、PLA(Programmable Logic Array,可编程逻辑阵列)中的至少一种硬件形式来实现。处理器31也可以包括主处理器和协处理器,主处理器是用于对在唤醒状态下的数据进行处理的处理器,也称CPU(Central ProcessingUnit,中央处理器);协处理器是用于对在待机状态下的数据进行处理的低功耗处理器。在一些实施例中,处理器31可以在集成有GPU(Graphics Processing Unit,图像处理器),GPU用于负责显示屏所需要显示的内容的渲染和绘制。一些实施例中,处理器31还可以包括AI(Artificial Intelligence,人工智能)处理器,该AI处理器用于处理有关机器学习的计算操作。

在一些实施例中,集成电路芯片引脚的有限元快速建模及结构力学性能分析装置还可包括有显示屏32、输入输出接口33、通信接口34、电源35以及通信总线36。本领域技术人员可以理解,图3中示出的结构并不构成对集成电路芯片引脚的有限元快速建模及结构力学性能分析装置的限定,可以包括比图示更多或更少的组件,例如传感器37。

关于上述方法更加具体的过程可以参考前述实施例中公开的相应内容,在此不再进行赘述。

进一步的,本发明还公开了一种计算机可读存储介质,用于存储计算机程序;计算机程序被处理器执行时实现前述公开的集成电路芯片引脚的性能分析方法。

关于上述方法更加具体的过程可以参考前述实施例中公开的相应内容,在此不再进行赘述。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似部分互相参见即可。对于实施例公开的装置、设备、存储介质而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

专业人员还可以进一步意识到,结合本文中所公开的实施例描述的各示例的单元及算法步骤,能够以电子硬件、计算机软件或者二者的结合来实现,为了清楚地说明硬件和软件的可互换性,在上述说明中已经按照功能一般性地描述了各示例的组成及步骤。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本申请的范围。

可以理解的是,如果上述实施例中的集成电路芯片引脚的性能分析方法以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本申请的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,执行本申请各个实施例方法的全部或部分步骤。而前述的存储介质包括:U盘、移动硬盘、只读存储器(Read-Only Memory,ROM)、随机存取存储器(Random AccessMemory,RAM)、电可擦除可编程ROM、寄存器、硬盘、可移动磁盘、CD-ROM、磁碟或者光盘等各种可以存储程序代码的介质。

本发明实施例提供的一种集成电路芯片引脚的性能分析方法,包括:将印制电路板和集成电路芯片的几何数据导入有限元建模软件中,建立有限元模型;对印制电路板和集成电路芯片的主体部分进行有限元网格划分,使集成电路芯片的每个引脚处均有网格节点;在每个引脚位置建立梁单元并设置相关接触关系失效参数;完成有限元模型中包含赋予材料和属性、设置部件间连接关系和接触关系的建模内容,并根据分析工况设置约束参数及载荷参数;对有限元模型进行运算分析,并根据运算分析结果判断集成电路芯片引脚是否满足结构力学相关性能要求。这样通过方便快速地建立用于集成电路芯片引脚分析的有限元模型,可以快速得到集成电路芯片引脚结构力学性能的数值分析结果,高效率、低成本地评估当前版本整体设计方案是否会导致集成电路芯片引脚结构在各个工况下产生结构可靠性问题,免去了生产试验试制件和进行试验测试的环节,无需进行多轮测试,有效地提高了研发效率,降低了研发成本,缩短了研发周期。另外,本发明采用的梁单元建模方式,相比于体单元建模,在保留合理精度的基础上,更快捷方便,节约时间。此外,本发明还针对集成电路芯片引脚的性能分析方法提供了相应的装置、设备及计算机可读存储介质,进一步使得上述方法更具有实用性,该装置、设备及计算机可读存储介质具有相应的优点。

最后,还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

以上对本发明所提供的集成电路芯片引脚的性能分析方法、装置、设备及介质进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

- 集成电路芯片引脚的性能分析方法、装置、设备及介质

- 集成电路性能分析方法、装置、仿真设备及存储介质