使用压缩的信道输出信息来解码数据的方法和系统

文献发布时间:2023-06-19 12:14:58

技术领域

本申请总体涉及使用压缩信道信息在通信系统中对数据进行解码,更具体地涉及在采用线性分组码(例如,极化码)的通信系统中对数据进行解码。

背景技术

为了在简单的上下文中引入由本发明原理解决的问题,考虑离散无记忆信道(Discrete Memoryless Channel,DMC),该信道在时刻i接收来自二进制输入字母表

在这种通信系统中的解码器接收信道输出y,并生成所发送消息m的估计

在高速数据通信中,信道输出y从信道到解码器的递送可能在必要的数据总线带宽、数据接口的成本和功耗方面呈现严重瓶颈。本发明原理通过引入方法来解决该问题,这些方法压缩信道输出y,以便在不劣化系统FER性能的情况下降低接收器处的通信复杂度。本发明原理主要针对通信系统,在这些通信系统中,从数据源到数据目的地的以每秒位数(B/S)为单位的用户数据速率相对于接收器电路中使用的时钟频率是高的。

为了更精确地陈述本发明原理在何处最有用,令λ表示从源到目的地的以每秒位数(B/S)为单位的期望用户数据速率,令R=log

w=(qλ/R)/f

本发明原理针对宽度w由于成本或可行性而对接收器电路的实现呈现瓶颈的应用。目前,有两个因素在工作时倾向于产生这种瓶颈。一个是对更高用户数据速率λ的一直存在的需求;另一个是硅技术进步的减慢,限制了时钟频率f

通过查看最近的标准化活动,可以看到对更高数据速率λ的需求。对于有线连接,IEEE802.3ba以太网标准指定了光介质上的数据速率λ=100千兆位每秒(Gb/s)[LAW]。在无线域中,2017年批准的IEEE 802.15.3d标准定义了使用在252-322千兆赫(GHz)范围内的频率的100Gb/s系统[HDRW]。当前IEEE 802.11ay标准化活动旨在在60GHz频带中给予100Gb/s无线速度[GHASE]。2018以太网路线图[ETHER]预测了2020和以上对每秒兆兆位(Tb/s)数据速率的需求。如这些示例所示,在不久的将来,将需要以接近Tb/s的数据速率λ操作的纠错编码系统。而由于增加的因特网流量,对更高数据速率的需求继续而不减弱,硅技术的进步没有跟上这种需求,这产生了如本发明原理所解决的类型的通信瓶颈。

传统上,可以通过半导体和超大规模集成(Very Large Scale Integration,VLSI)技术的改进来满足通信系统中对增加的数据速率λ的需求。直到最近,VLSI技术非常接近地遵循被称为摩尔(Moore)定律和登纳德(Dennard)缩放比例的预测[NIKOL],摩尔定律和登纳德缩放比例一起假定,当半导体技术大致每十八个月从一个技术世代移动到下一个时,每单位功率的VLSI性能随时间呈指数增长。然而,随着晶体管大小开始接近基本物理极限,这些预测变得无效,并且VLSI技术的性能和能量效率开始饱和。尽管晶体管尺寸仍然根据摩尔定律继续缩小,但是由于功率密度约束,晶体管开关速度(时钟频率)无法保持增加[ESMAE]。随着时钟频率的稳定,采用多个处理器的并行计算方法已经成为提高计算性能的主要手段[BETZE]。另一方面,当任务在多个处理器之间被分割时,互连网络必须存在于处理器之间以支持处理器间通信和同步。如阿姆达尔(Amdahl)定律[AMDAH]所陈述的,即使多处理器系统中的互连网络中的少量等待时间也可能急剧地降低并行计算的益处。作为上述技术发展的结果,在时延和功耗方面的通信开销的减少已经作为高性能计算中的关键设计目标出现[BETZE]。本发明原理在用于信道码的高性能解码器的上下文中解决了该挑战。

对于示出了由本发明原理解决的计算问题的规模的数值示例,考虑具有λ=1Tb/s的期望用户数据速率、具有速率R=2/3的信道码、大小为2

在本发明原理的一个实施例中,通过应用校正子解码方法和/或使用源编码方法压缩信道输出,降低了将信道输出从信道传送到解码器的复杂度。在本发明原理的优选实施例中,使用用于极化码的校正子解码器。本发明原理可与用于极化码的任何类型的解码算法组合应用,包括具有或不具有CRC的连续消除解码和连续消除列表解码。本发明原理可应用于具有穿孔和/或缩短的极化码。

本公开预测,除了上述常规解码应用之外,本发明原理可以应用于客户端-服务器类型架构,其中,被指定为解码服务器的专用处理单元服务于多个解码客户端。在客户端-服务器架构中的本发明原理的一个实施例中,解码服务器位于云中,并且多个解码客户端通过例如因特网、4G或5G蜂窝网络或Wi-Fi网络的通信网络连接到解码服务器。在另一客户端-服务器类型实施例中,解码服务器和解码客户端位于同一芯片上,并且通信通过片上网络进行。后一种类型的实施例在片上系统(System-on-Chip,SoC)类型设计中是有用的,在该设计中,需要通过位于移动手机内部的单个芯片来支持多个信道码,例如支持LTE和Wi-Fi标准。

本发明原理可应用于减少从解码客户端到解码服务器的数据量。本发明原理的附加优点在于,解码服务器未获得对用户数据的访问;如果云不可信,则这种类型的隐私是重要的。

参考文献:

[AMDAH]Amdahl,G.M.(1967年)‘Validity of the Single Processor Approachto Ac hieving Large Scale Computing Capabilities’,in Proceedings of the April18-20,1967,Spri ng Joint Computer Conference.New York,NY,USA:ACM(AFIPS’67(Spring)),第483–485页.doi:10.1145/1465482.1465560.

[BETZE]Betzel,F.等人.(2018年)‘Approximate Communication:Techniquesfor Reduc ing Communication Bottlenecks in Large-Scale Parallel Systems’,ACMComput.Surv.,51(1),第1:1–1:32页.doi:10.1145/3145812.

[DAMBR]D’Ambrosia,J.(2010年)‘100gigabit Ethernet and beyond’,IEEECommun ications Magazine,48(3),第S6–S13页.doi:10.1109/MCOM.2010.5434372.

[ESMAE]Esmaeilzadeh,H.等人(2011年)‘Dark silicon and the end ofmulticore scali ng’,in 2011 38th Annual International Symposium on ComputerArchitecture(ISCA),第365–376页.

[ETHER]‘The 2018Ethernet Roadmap’.可在https://ethernetalliance.org/the-2018-ethern et-roadmap/找到(2018年6月8日访问).

[GHASE]Ghasempour,Y.等人.(2017年)‘IEEE 802.11ay:Next-Generation 60GHzC ommunication for 100Gb/s Wi-Fi’,IEEE Communications Magazine,55(12),第186–192页.

doi:10.1109/MCOM.2017.1700393.

[HDRW]IEEE 802.15.3d-2017-IEEE Standard for High Data Rate WirelessMulti-Me dia Networks Amendment 2:100Gb/s Wireless Switched Point-to-PointPhysical Layer.可在https://standards.ieee.org/findstds/standard/802.15.3d-2017.html找到(2018年6月8日访问).

[LAW]Law,D.等人.(2013年)‘Evolution of Ethernet standards in the IEEE802.3wor king group’,IEEE Communications Magazine,51(8),第88–96页.doi:10.1109/MCOM.2013.6576344.

[NIKOL]Nikolic,B.(2008)‘Design in the Power-Limited Scaling Regime’,IEEE Tran sactions on Electron Devices,55(1),第71–83页.doi:10.1109/TED.2007.911350.

[ZABIN]Zabinski,P.J.,Gilbert,B.K.以及Daniel,E.S.(2013年)‘ComingChallenge s with Terabit-per-Second Data Communication’,IEEE Circuits andSystems Magazine,13(3),第10–20页.doi:10.1109/MCAS.2013.2271441.

此处以引用的方式将上述出版物并入。

发明内容

在一个实施例中,一种用于通信系统中的分体式解码器设备提供所发送消息从源到目的地的可靠转移。信道编码器将发送消息(transmitted message)从信道码编码为发送码字(transmitted codeword),并通过信道发送该发送码字。信道响应于所发送的码字而产生信道输出。分体式解码器设备包括:解码客户端,该解码客户端被配置为接收信道输出并生成经压缩的错误信息;以及解码服务器,该解码服务器被配置为接收经压缩的错误信息并生成经压缩的错误估计。解码客户端接收经压缩的错误估计并生成消息估计。降低了解码客户端与解码服务器之间的通信复杂度。分体式解码器设备可选地从信道输出生成无错误信号,其中,如果无错误信号指示硬判决对应于有效发送码字,则不启动解码服务器。信道码优选是系统或非系统线性分组码中的一个,并且优选是系统或非系统极化码中的一个。解码服务器包括错误估计器。错误估计器可以是用于极化码的连续消除解码器或连续消除列表解码器中的一个。额外的奇偶校验位,例如循环冗余校验(CyclicRedundancy Check,CRC)位,可以在信道编码之前被添加到发送消息中,使得如果硬判决对应于有效的发送码字,则解码客户端可以更可靠地进行校验,并且错误估计器可以更可靠地估计发送码字。解码客户端优选地包括硬判决和错误辅助信息(Hard Decision andError Side Information,HD/ESI)发生器、错误校正子发生器、错误辅助信息压缩器、错误估计解压缩器和错误纠正器,并且解码服务器优选地包括错误辅助信息解压缩器、错误估计器和错误估计压缩器,其中HD/ESI发生器优选地接收信道输出并生成硬判决和错误辅助信息,并且当硬判决向量对应于信道码中的有效码字时,解码客户端优选地避免调用解码服务器。在一些实现方式中,错误辅助信息可以是空的。HD/ESI发生器可以在生成硬判决和错误辅助信息之前可选地对信道输出应用量化。错误校正子发生器可以被配置为接收硬判决并生成错误校正子,而错误辅助信息压缩器可以被配置为接收错误辅助信息并通过使用无损源编码算法来生成经压缩的错误辅助信息。在一些实施例中,错误校正子和经压缩的错误辅助信息共同地构成经压缩的错误信息,错误辅助信息解压缩器接收经压缩的错误辅助信息并且解压缩经压缩的错误辅助信息以恢复错误辅助信息,并且错误估计器接收错误校正子和由错误辅助信息解压缩器恢复的错误辅助信息的副本并且生成错误估计,错误估计压缩器在生成经压缩的错误估计时压缩该错误估计,并且错误估计解压缩器接收和解压缩经压缩的错误估计以恢复错误估计,以用于错误纠正器在生成消息估计时与硬判决一起使用。错误辅助信息压缩器可以采用算术编码算法来进行无损源压缩。HD/ESI发生器可以采用最大互信息量化器来量化信道输出。

在另一实施例中,一种用于通信系统中的分体式解码器方法提供所发送消息从源到目的地的可靠转移。将发送消息从信道码编码为发送码字,并且通过信道发送该发送码字,信道响应于所发送的码字产生信道输出。分体式解码器方法包括:在解码客户端处接收信道输出,并且生成经压缩的错误信息;在解码服务器处接收经压缩的错误信息并生成经压缩的错误估计;以及在解码客户端处接收经压缩的错误估计并生成消息估计。降低了解码客户端与解码服务器之间的通信复杂度。可以在解码客户端中从信道输出生成无错误信号,其中,如果无错误信号指示硬判决对应于有效发送码字,则不启动解码服务器。信道码优选是系统或非系统线性分组码中的一个,并且优选是系统或非系统极化码中的一个。错误估计器可以是用于极化码的连续消除解码器或连续消除列表解码器中的一个。额外的奇偶校验位,例如循环冗余校验(Cyclic Redundancy Check,CRC)位,可以在信道编码之前被添加到发送消息中,由此,如果硬判决对应于有效的发送码字,则解码客户端可以更可靠地进行校验,并且错误估计器可以更可靠地估计发送码字。解码客户端可以包括硬判决和错误辅助信息(HD/ESI)发生器、错误校正子发生器、错误辅助信息压缩器、错误估计解压缩器和错误纠正器,而解码服务器可以包括错误辅助信息解压缩器、错误估计器和错误估计压缩器,其中HD/ESI发生器被配置为接收信道输出并生成硬判决和错误辅助信息。方法优选地包括:当硬判决向量对应于信道码中的有效码字时,由解码客户端避免调用解码服务器,其中,在一些实现方式中,错误辅助信息可以是空的。HD/ESI发生器可以在生成硬判决和错误辅助信息之前可选地对信道输出应用量化。方法优选地包括:在错误校正子发生器中接收硬判决并生成错误校正子;在错误辅助信息压缩器中接收错误辅助信息,并通过使用无损源编码算法生成经压缩的错误辅助信息,其中,错误校正子和经压缩的错误辅助信息共同地构成经压缩的错误信息;在错误辅助信息解压缩器中接收经压缩的错误辅助信息,并解压缩经压缩的错误辅助信息以恢复错误辅助信息;在错误估计器中接收错误校正子和由错误辅助信息解压缩器恢复的错误辅助信息的副本,并且生成错误估计;在错误估计压缩器中压缩错误估计,并产生经压缩的错误估计;在错误估计解压缩器中接收和解压缩经压缩的错误估计以恢复错误估计;以及在错误纠正器中接收错误估计和硬判决,并生成消息估计。错误辅助信息压缩器可以采用算术编码算法来进行无损源压缩。HD/ESI发生器可以采用最大互信息量化器来量化信道输出。

在又一个实施例中,用于在受到隐私约束的客户端-服务器架构中执行信道解码的多客户端分体式解码器系统包括解码服务器和多个解码客户端,其中,多个解码客户端中的第i个解码客户端被配置为从第i个信道接收第i个信道输出,第i个信道输出是来自第i个信道码的第i个发送码字的损坏版本,并且第i个解码客户端从第i个信道输出生成第i个经压缩的错误信息,并且通过通信网络将第i个经压缩的错误信息发送到解码服务器。解码服务器从通信网络接收第i个经压缩的错误信息,生成第i个经压缩的错误估计,并将第i个经压缩的错误估计发送到第i个解码客户端,该解码客户端从通信网络接收第i个经压缩的错误估计并生成第i个消息估计,由此,防止解码服务器得知第i个消息。在多客户端分体式解码器系统中,第i个信道码是极化码。

在进行下面的详细描述之前,阐明贯穿本专利文献使用的某些词语和短语的定义可以是有利的。术语“耦合”及其派生词指代两个或更多个元件之间的任何直接或间接通信,而不管这些元件是否彼此物理接触。术语“发送”、“接收”和“通信”及其派生词涵盖直接和间接通信。术语“包括”和“包含”以及其派生词意指包括而没有限制。术语“或”是包括性的,意指和/或。短语“与……关联”及其派生词意指包括、被包括在内、与……互连、包含、被包含在内、连接到或与……连接、耦合到或与……耦合、可与……通信、与……协作、交错、并置、接近、绑定到或与……绑定、具有……的特性、与……具有关系等。术语“控制器”意指控制至少一个操作的任何装置、系统或其一部分。这种控制器可以以硬件或硬件与软件和/或固件中的任一个或两者的组合来实现。与任何特定控制器相关联的功能可以是集中式的或分布式的,无论是本地的还是远程的。当与项目列表一起使用时,短语“至少一个”意指可以使用所列项目中的一个或多个的不同组合,并且可能仅需要列表中的一个项目。例如,“A、B和C中的至少一个”包括以下组合中的任何一种:A;B;C;A和B;A和C;B和C;以及A、B和C。

而且,下面描述的各种函数可以由一个或多个计算机程序实现或支持,各个计算机程序由计算机可读程序代码形成并且在计算机可读介质中具体实施。术语“应用”和“程序”指代一个或多个计算机程序、软件组件、指令集、规程、函数、对象、类、实例、相关数据或其适于以合适的计算机可读程序代码实现的部分。短语“计算机可读程序代码”包括任何类型的计算机代码,包括源代码、目标代码和可执行代码。短语“计算机可读介质”包括能够由计算机访问的任何类型的介质,例如只读存储器(ROM)、随机存取存储器(RAM)、硬盘驱动器、压缩盘(CD)、数字视频盘(DVD)或任何其他类型的存储器。“非瞬态”计算机可读介质排除传输暂时性电信号或其它信号的有线、无线、光学或其它通信链路。非瞬态计算机可读介质包括其中数据可以被永久存储的介质和其中数据可以被存储并且之后被重写的介质,例如可重写光盘或可擦除存储装置。

贯穿本公开提供了其它某些词语和短语的定义。本领域的普通技术人员应当理解,在许多(如果不是大多数)情况下,这样的定义适用于这样定义的词语和短语的先前以及将来的使用。

附图说明

为了更完整地理解本公开及其优点,现在结合附图参考以下描述,附图中,同样的附图标记表示同样的零件:

图1是可以采用本发明原理的用于数据传输的通信系统的功能框图;

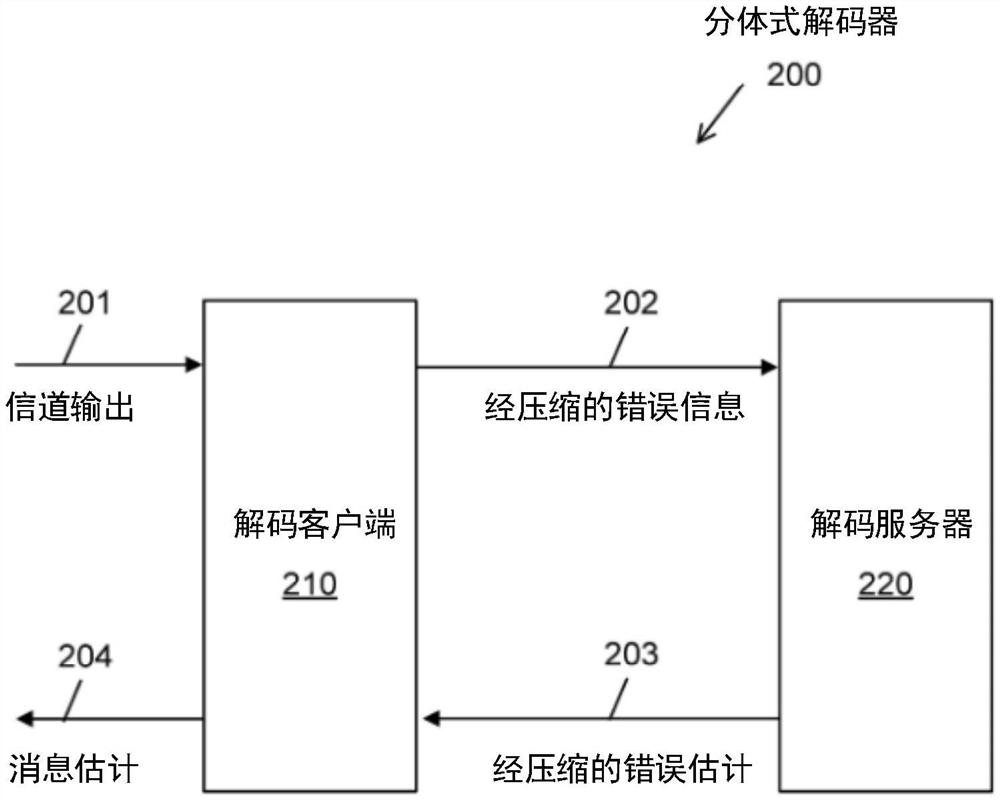

图2是信道解码器的功能框图,在该信道解码器中,解码器功能被分成两个功能块,称为解码客户端和解码服务器,以便降低两个块之间的通信复杂度;

图3是客户端-服务器配置的图片,在该配置中,解码服务器在多个解码客户端之间共享;

图4是根据图2的架构的信道解码器的优选实施例的功能框图;

图5是示出了本发明原理的优选实施例中的算术编码的有效性的曲线图;

图6示出了SC解码器和SC校正子解码器;

图7示出了根据本公开的其中可以实现信道解码的示例无线网络;

图8A示出了根据本公开的其中可以实现信道解码的示例用户设备网络;以及

图8B示出了根据本公开的其中可以实现信道解码的示例增强节点B(EnhancedNodeB,eNB)网络。

具体实施方式

下面讨论的图1至图8B以及在本专利文献中用于描述本公开的原理的各种实施例仅仅是作为例示,而不应以任何方式被解释为限制本公开的范围。本领域技术人员应当理解,本公开的原理可以在任何适当布置的通信系统中实现。

在以下描述中,由例如

根据编码理论中已建立的惯例,系统中的数据字和码字被表示为有限域

给定向量x=(x

香农(Shannon)的熵和互信息概念是本公开中的关键概念。具有概率质量函数(Probability Mass Function,PMF)p(x)的离散随机变量X的熵被定义为H(X)=-∑

在以下描述中,出于说明的目的阐述了例如特定实施例、过程、技术等的具体细节,以便提供对本发明原理的透彻理解,而非限制。然而,对于本领域技术人员来说显而易见的是,可以在脱离本文的具体细节的其它实施例中实践本发明原理。例如,可以在任何数据发送器与数据接收器之间的任何数据通信系统中实现本发明原理,例如,参见图1。本发明原理的一个特定的、非限制性的应用是在无线通信系统中,例如,参见图7和图8A至图8B。

一些附图包含单独的功能块,而没有详细说明用于实现它们的硬件电路的构造和操作。无论何时省略这些细节,都将是以下情况:本领域技术人员将能够理解:功能至少在某种程度上由硬件电路实现,并且可以使用单独的硬件电路、使用与适当编程的数字微处理器或通用计算机结合起作用的软件、使用专用集成电路(ASIC)和/或使用一个或多个数字信号处理器(Digital Signal Processor,DSP)来实现。

考虑到上述内容,首先参考图1,示出了通信系统100,在该通信系统中,可以使用根据本公开的实施例的用于使用压缩的信道输出信息来解码数据的系统的实施例。如图所示,通信系统100包括信道编码器110、信道120和信道解码器130。信道120包括发送器121、传输介质122和接收器123。信道编码器110接收发送的消息101,并将发送的消息101从信道码编码为发送的码字。发送器121接收发送的码字,将发送的码字调制成发送信号,并将发送信号发送到传输介质122。传输介质122响应于所发送的信号在其输出处产生接收信号。接收器123接收所接收的信号,对其进行解调,并产生信道输出。解码器130接收信道输出并产生消息估计102。

将容易地理解,接收器123和信道解码器130分别执行与发送器121和信道编码器110所执行的操作相反的操作,受到系统中噪声效应和其它非理想性所施加的限制。在任何情况下,如果通信系统100被适当地设计并在其设计参数内操作,则消息估计102应当以高可靠性匹配发送消息101。实际上,通信系统100的主要目标是将发送消息101再现为消息估计102而没有任何错误。如果消息估计102不等于发送的消息101,则认为出现帧错误。通信系统100的关键性能度量是误帧率(FER),该FER被定义为帧错误事件的概率。

应当理解,本发明原理适用于各种传输系统和介质。例如,在无线通信系统中,传输介质122通常是空间或大气,在这种情况下,通信系统100是无线通信系统。在这样的实施例中,发送器121和接收器123各自包括分别耦合到发送器121和接收器123的一个或多个天线。然而,本公开的其他实施例可以在有线通信系统中实现,在这种情况下,传输介质122可以是将发送器121连接到接收器123的电缆或电线。本公开的实施例还可以被实现用于存储系统,在这种情况下,传输介质122可以是磁带、硬盘驱动器、光盘驱动器、固态存储器或另一存储介质。

在以上描述中,调制操作被认为是发送器121的一部分,而解调操作被认为是接收器123的一部分。为了不使描述被不必要的细节混乱,省略了调制和解调操作的细节。调制是将符号(离散时间离散幅度)序列(例如码字的元素)映射到能够通过传输介质122传输的物理波形的操作。解调是对传输介质122的输出进行处理以生成(离散时间、离散或连续幅度)信道输出的逆操作。理想地,信道输出包含关于在接收信号中可用的发送码字的所有相关信息。本领域技术人员在实现本发明原理以及各种调制方案(例如相移键控(PSK)、脉冲幅度调制(PAM)或正交幅度调制(QAM))方面没有困难。

从实现的角度来看,通信系统100的部件可以被分组为发送子系统140和接收子系统150。发送子系统包括信道编码器110和发送器121。接收子系统包括接收器123和信道解码器130。根据本发明原理,发送子系统140的各个部件110和121以及接收子系统150的各个部件123和130包括电路,并且可以在其相应的半导体芯片上实现,其中各个芯片根据图1的系统彼此通信。可替代地,一个半导体芯片可以承载发送系统的所有或多个部件,并且第二半导体芯片可以承载接收系统的所有或多个部件。这样的芯片可以实现例如本文所述的逻辑门电路。此外,包括电路和以硬件(可选地由软件或固件编程)实现的访问逻辑的处理器(例如数字信号处理器(DSP))可以执行发送系统140和(在单独的处理器上)接收系统150中的每一个的一个或多个部件的功能。如果软件形成一个或多个处理器的实现的一部分(除了数字逻辑和模拟信号处理电路形式的硬件之外),则软件被存储在例如但不限于基于盘的或固态存储的计算机可读存储介质上,使得例如DSP的机器根据逻辑执行方法步骤。在任何情况下,当信道解码器130在半导体芯片上实现时,芯片的电路根据本文描述建立解码电路。类似地,当信道解码器130由访问以硬件实施的逻辑(或者可选地,硬件逻辑的以软件实施的逻辑编程)的处理器实现时,具有逻辑的处理器根据本文描述建立定义信道解码器的电路。可以使用上述实现的组合。

本发明原理解决的技术问题是信道120上期望的数据传输速率λ与通信系统100中的数字电路所使用的时钟频率f

用于在实现接收子系统150时降低通信复杂度的重要设计考虑是决定在哪里以及如何应用数据压缩来降低接收子系统150内的数据流量。可以采用压缩作为接收器123的一部分,以便降低从接收器123到信道解码器130的通信复杂度。在信道解码器130内部可以采用进一步的压缩,以降低信道解码器130的实现中的通信复杂度。本公开引入了分体式解码器架构,该架构在实现接收器123与信道解码器130之间的接口时提供了更大的灵活性。分体式解码器架构提倡对接收器和解码器功能进行联合优化,以便在解码器性能没有显著劣化的情况下降低通信复杂度。

转到图2,示出了分体式解码器200,该分体式解码器用作用来将压缩方法引入到信道解码器130的实现中的架构模板。分体式解码器200包括解码客户端210和解码服务器220。解码客户端210接收信道输出201,并且生成经压缩的错误信息202。解码客户端的操作可以包括在生成经压缩的错误信息220之前的量化功能。解码服务器220接收经压缩的错误信息202,并生成经压缩的错误估计203。解码客户端210接收经压缩的错误估计203,并且生成消息估计204。

分体式解码器200具有被设计成减少功能块210和220之间的数据流量的架构。该目标通过使用校正子解码方法来实现,这些方法估计由信道引入的错误而不是直接估计发送消息。一些公知的可获得校正子解码方法的信道码包括博斯-查德胡里-霍昆格姆(Bose-Chaudhuri-Hocquenghem)(BCH)码、里德-穆勒(Reed-Muller)(RM)码、里德-所罗门(Reed-Solomon)(RS)码和低密度奇偶校验(LDPC)码。对于BCH码和RS码,存在公知的校正子解码方法,例如伯利坎普-梅西(Berlekamp-Massey)算法。对于LDPC码,置信传播(BP)解码可以用作校正子解码方法。

较新类型的信道码是极化码。极化码是如以下参考文献中描述的线性分组码:“Arikan,E.(2009年)‘Channel Polarization:A Method for Constructing Capacity-Achieving Codes for Symmetric Binary-Input Memoryless Channels’,IEEETransactions on Information Theory,55(7),第3051–3073页”。本发明原理可以与极化码一起使用。极化码具有编码和解码算法复杂度低的优点。本说明书公开了一种用于极化码的校正子解码算法,该算法源自参考文献“Arikan,E.(2010年)‘Source polarization’,in 2010IEEE International Symposium on Information Theory Proceedings(ISIT),IEEE,第899–903页”。

本发明的原理可以应用于系统和非系统信道码。如果发送消息作为发送码字的一部分出现,则信道编码器110被称为系统的。如果信道编码器110不是系统的,则它被称为非系统的。分体式解码器200的实现取决于信道编码器是否是系统的。通常,系统编码在分体式解码器200处提供了计算和通信复杂度的更大降低。下面给出的本发明原理的特定实施例将说明校正子解码与系统和非系统编码的一起使用。

分体式解码器200架构的另外优点是,它可以用于确保解码服务器220不得知(learn)关于发送消息的任何信息。在以下讨论的本发明原理的优选实施例中,仅向解码服务器220呈现关于信道错误的信息,并且关于信道错误的信息不携带关于所发送消息的信息。

为了从本发明原理得到最大可能的益处,解码客户端210的一些功能应当被实现为非常接近接收器123或者作为其组成部分。这些功能中的主要功能是解码客户端210的量化功能,该量化功能在很大程度上与位于接收器123内部的解调功能重叠。如果为了控制通信复杂度,解码客户端210必须将精细分辨率输出量化到较粗的水平,则解调器不需要产生这种输出。将解码客户端的量化功能与解调器的量化功能合并可以消除不必要的复杂度。尽管这是优选的方法,但是下面的描述为在接收器123和解码客户端210处的单独的量化功能留出了空间。在接收器123从外部不可访问的情况(如在单独的芯片上实现接收器时将是这种情况)下,具有两个单独的量化器可能是不可避免的。

转到图3,示出了多客户端分体式解码器300,该解码器示出了图2的分体式解码器架构的优点。多客户端分体式解码器300包括解码服务器310和多个解码客户端320、330、340。多个解码客户端和解码服务器通过通信网络350彼此通信。通信网络可以是例如因特网的广域网、局域网、或卡上网络、或片上网络。该网络化的架构允许在多个解码客户端之间共享单个解码服务器,以便提供成本降低。在共享公共解码服务器时,发送消息101的隐私可能是一个问题。例如,如果解码客户端位于公共云中,则隐私的维护是关键问题。本发明原理通过向解码服务器呈现经压缩的错误信息202来确保这种隐私。在下面讨论的本发明原理的优选实施例中,经压缩的错误信息202独立于发送消息101,因此确保在基本意义上保护隐私。

转到图4,示出了根据图2的一般架构构造的分体式解码器400的细节。分体式解码器400包括解码客户端410和解码服务器420作为主要功能块。解码客户端410包括硬判决和错误辅助信息(HD/ESI)发生器411、错误校正子发生器412、错误辅助信息压缩器413、错误估计解压缩器414和错误纠正器415。

HD/ESI发生器411接收信道输出并生成硬判决和错误辅助信息。根据本发明原理,硬判决旨在用作对所发送码字的初始估计。硬判决是有限字母表上的一串符号,典型地,该有限字母表与用于所发送码字的字母表相同。错误辅助信息旨在用作关于硬判决的准确性的置信度的度量。理想地,各个单独硬判决的置信度的度量是该硬判决出错的概率、或者与该概率等效的某个度量。为了控制通信复杂度,本发明原理将用于错误辅助信息的字母表(此后表示为

错误校正子发生器412接收硬判决,并且校验硬判决是否对应于通信系统100所使用的信道码中的有效码字。错误校正子发生器412根据硬判决是否对应于有效码字而分别将无错误信号设置为1或0。如果无错误信号是1,则错误校正子发生器412不向解码服务器420发送任何信息。如果无错误信号是0,则错误校正子发生器412向解码客户端420发送错误校正子。错误校正子发生器412可以计算错误校正子作为校验硬判决是否对应于有效码字的第一步骤。在一些情况下,错误校正子发生器412可以利用被内置到所发送码字中的附加冗余来判定硬判决是否对应于有效码字。附加冗余可以采取循环冗余校验(CRC)的形式,该CRC根据所发送数据来计算并且被插入到码字中。

错误辅助信息压缩器413等待来自错误校正子发生器412的无错误信号。如果无错误信号是1,则错误辅助信息压缩器413不向解码客户端420发送任何信息。如果无错误信号是0,则错误辅助信息压缩器413从HD/ESI发生器411接收错误辅助信息,压缩错误辅助信息以生成经压缩的错误辅助信息,并将经压缩的错误辅助信息发送到解码服务器420。错误校正子和经压缩的错误辅助信息包括图2中的经压缩的错误信息202。

解码服务器420包括错误辅助信息解压缩器421、错误估计器422和错误估计压缩器423。解码服务器在开始新的解码操作之前等待错误校正子和经压缩的错误辅助信息。(如果无错误信号是1,则解码客户端在该解码循环中不变为有效。)一旦错误校正子和经压缩的错误信息到达,解码服务器就被激活。(解码服务器的激活由控制器电路执行,该控制器电路在图2中未示出,因为根据本公开的这种控制器的构造是本领域技术人员的常规设计任务)。错误辅助信息解压缩器421接收经压缩的错误辅助信息,并重新生成错误辅助信息。错误估计器422接收来自错误辅助信息解压缩器421的错误辅助信息和来自错误校正子发生器412的错误校正子,并生成错误估计。错误估计压缩器423接收错误估计并将其压缩以生成经压缩的错误估计。错误估计解压缩器414接收经压缩的错误估计,并对其进行解压缩以重新生成错误估计。

错误纠正器415取决于无错误信号是1还是0而具有两种操作模式。如果无错误信号是1,则错误纠正器415通过假设硬判决形成所发送码字的正确估计来进行设置以生成消息估计。如果无错误信号是0,则错误纠正器115等待错误估计从错误估计解压缩器414到达,并且在接收到错误估计之后,继续生成消息估计。

在本发明原理的优选实施例中,错误辅助信息压缩器413和错误估计压缩器423执行无损数据压缩。无损压缩是可逆的;压缩数据可以由适当的解压缩器精确地恢复。对于无损压缩,合适的算法是算术编码,如在例如以下参考文献中描述的:“Howard,P.G.andVitter,J.S.(1994年)‘Arithmetic coding for data compression’,Proceedings ofthe IEEE,82(6),第857–865页”。

在本发明原理的优选实施例中,HD/ESI发生器411可以可选地应用量化(有损数据压缩)作为错误辅助信息的生成的一部分。量化是不可逆的;一些信息在量化之后永久丢失。使用量化以便将通信复杂度降低到可用解码器电路能够支持的水平。如上结合图2中的解码客户端210的一般描述提及的,如果解码客户端包括量化功能,则优选地将这样的功能与接收器123中的量化功能集成。在这种情况下,HD/ESI发生器411可以被实现为接收器123的一部分。如果量化功能的这种集成是不可能的,那么HD/ESI发生器411的量化功能应当被实现为尽可能靠近接收器123,以便使两个模块之间的数据总线的长度最小化。

本发明的原理通过避免在信道解码器130的各种功能性构建块之间不必要地转移大量数据而在降低通信复杂度方面提供了显著的优点(如将在下文中示出的)。分体式解码器400架构被设计成通过保持数据尽可能本地并且仅在必要时转移数据以及使用压缩进一步减少数据流量,来实现通信复杂度的节省。

如本发明原理所规定的,为降低通信复杂度所付出的代价是需要使用数据压缩和解压缩,这增加了整个系统的计算复杂度。错误估计器422具有与普通解码器相当的计算复杂度,并且不会实质上增加或减少整个系统的计算复杂度。作为由于使用数据压缩和解压缩而增加的计算复杂度的回报,本发明原理需要显著更少数量的通信资源,如通过片上数据总线中的通道数量或芯片到芯片接口处的输入/输出(I/O)引脚的数量所测量的。将通过本发明原理的特定实施例和示例来示出本发明原理的应用中的计算复杂度与通信复杂度之间的该折衷。

本发明原理的第一优选实施例。首先看图1,当信道120是二进制输入无记忆信道(Binary-Input Memoryless Channel,简称BMC),即具有二进制输入字母表

在第一优选实施例中,通信系统100所采用的信道码是二进制域

通过信道120发送所发送的码字x,并且在信道120的输出处接收信道输出y=(y

为了在第一优选实施例中指定信道解码器130的另外细节,现在转到图4。在本上下文中,HD/ESI发生器411接收信道输出y=(y

从LLR向量,HD/ESI发生器411通过在l

错误向量e=(e

错误校正子发生器412使用硬判决向量z通过计算s=zH来生成错误校正子向量s=(s

如果无错误信号是1,则错误纠正器415通过求解方程

如果无错误信号是0,则解码服务器420变为有效的。错误估计器422产生错误估计向量

本发明原理的第二优选实施例。除了第二优选实施例中的信道编码器411是系统的之外,本发明原理的第二优选实施例与第一优选实施例相同。换言之,存在具有大小K的信息集

系统编码对于本发明原理的应用是有利的,因为错误纠正器415可以简单地通过计算

此外,当信道编码是系统的时,错误估计压缩器423仅需要压缩错误估计

示例1。该示例在简单的上下文中示出了本发明原理的第一优选实施例。在该示例中,信道编码器110是非系统的。信道120是二进制对称信道(Binary Symmetric Channel,BSC),该信道是BMC的特殊情况,其中,

对于BSC,LLR具有两个可能的值:如果y

由于错误辅助信息m是恒定的,m=(a,a,…,a),因此在该示例中,错误辅助信息压缩器413和错误辅助信息解压缩器421是冗余的;它们不需要被实现。错误估计器422可以被配置为接收恒定错误辅助信息的本地生成的副本以执行其任务。

示例1中的系统的其余部分根据以上作为本发明原理的第一优选实施例的一部分所描述的一般规则来操作。

为了示出本发明原理的优点,首先在从解码客户端410到解码服务器420的方向上,然后在相反方向上,分析示例1的通信复杂度。

从解码客户端到解码服务器的通信复杂度。在该示例中,经压缩的错误辅助信息是空字符串。因此,必须从解码客户端410传送到解码服务器420的位数等于错误校正子s的长度,即(N-K)=N(1-R)位,其中,R=K/N是码率。在类似的情况下,接收子系统150将从接收器123向信道解码器130发送N位(信道输出y的长度)。因此,与基准接收子系统150相比,本发明原理将通信复杂度改善了(1-R)倍。对于具有接近1的码率R的系统,该改进变得尤其显著。

通信复杂度的(1-R)倍降低直接转化为在总线宽度和芯片接口方面的硬件复杂度的类似节省。基准接收子系统150(其中接收器123和信道解码器130是分开的实体)需要总线宽度w=(λ/R)/f

在具有λ=1Tb/s、f

有许多R接近于1的通信系统的示例。例如,在光通信中,G.709标准使用具有码率R≈0.94的里德-所罗门码,而较新的标准G.975.1规定了具有0.82到0.94范围内的码率的各种码,例如BCH和LDPC码。另一个示例是用于高数据速率无线多媒体网络的最近IEEE802.15.3d标准,该网络使用具有码率11/15和14/15的LDPC码。当应用于这样的系统时,本发明原理将从接收器123到信道解码器130的数据流量减少了82%到94%。

从解码服务器到解码客户端的通信复杂度。在相反方向,错误估计压缩器423发送错误估计向量

示例2。该示例旨在示出如在本发明原理的第二优选实施例中那样使用系统编码的另外优点。除了这里信道编码器110是系统的之外,该示例在每个方面与示例1相同。从解码客户端410到解码服务器420的通信复杂度与示例1中相同。在相反方向上,示例2中的通信复杂度小于示例1中的通信复杂度,因为错误估计压缩器423在这里只发送错误估计

系统编码的另外优点是错误纠正器415可以简单地通过计算

示例3。在示例1和2中,错误服务信息为空的。该示例示出了错误辅助信息不为空的情况。在该示例中,BMCW具有输出字母表

LLR在字母表

各个错误辅助信息变量m

为了示出本上下文中的数据压缩的有效性,将报告两个简单的仿真研究。仿真采用算术编码算法,该算法是用于错误辅助信息压缩器413的无损数据压缩的优选方法。

在第一仿真研究中,参数是N=1000和α=0.7。通过算术编码来压缩m=(m

第二仿真研究与第一研究相同,除了在此使用α=0.9。压缩序列的平均长度是476位,实际长度在388至568之间变化。通信复杂度的平均节省是52%。压缩比在熵极限h(0.9)=0.479的1.5%内。

通常,本发明原理具有由N(1-R)(针对错误校正子)和NH(m

示例4。本示例示出了在信道输出字母表是连续的情况(非常精细量化的理想化)下的本发明原理,这使得必须使用量化器作为HD/ESI发生器411的一部分。在先前的示例中,解码客户端从信道接收已经量化的样本。在该示例中描述的方法也可以应用于接收器123不可访问并且需要信道输出的更粗略量化以便将从解码客户端410到解码服务器420的通信复杂度降低到可接受水平的情况。

具体而言,这里假设信道120是具有二进制相移键控(Binary Phase ShiftKeying,BSPK)调制的加性高斯噪声信道(Additive Gaussian Noise Channel,AGNC)。将所发送的码字x=(x

和

比率A

HD/ESI发生器411在此遵循第一优选实施例中的一般方法。LLR值的形式计算(使用自然对数)给出:

LLR值l

其中,Q是量化器(从实线(-∞,∞)到表示点的

在计算出量化LLR值

在该示例的其余部分中,幅度参数被固定为A=1。

可用作HD/ESI发生器的一部分的量化器Q通常可由一对集合

量化器

示例4继续使用具有

最大互信息设计规则将在特定信道SNR 1/σ

对于上述量化器,从量化LLR值导出的硬判决在每个SNR处同样可能是0或1。因此,在每个SNR处,H(z

示例继续以算术编码作为自适应源编码的方法。这里省略了算术编码的细节以及如何将其应用于压缩问题,因为这些对于本领域技术人员来说是公知的主题。这里将仅报告仿真研究以提供在本上下文中的算术编码的有效性的经验证据。在仿真研究中,算术编码用于在从-10dB到12dB的SNR范围上以1dB为步长压缩错误辅助信息变量m

在示例4中,最大互信息量化器已经被用作示出性示例。可以更简单地实现的替代量化器是均匀量化器,对于该均匀量化器,边界点之间的间隔是固定的。本领域技术人员将从上述示例认识到,本发明原理可以用其它类型的量化器和源编码算法来实践。

本发明原理的最优选实施例。本发明原理的最优选实施例是第一和第二优选实施例的特殊情况,进一步的说明是在最优选实施例中使用的信道码是极化码,该极化码是在以下参考文献中介绍的线性分组码的类型:“Arikan,E.(2009年)‘Channel Polarization:A Method for Constructing Capacity-Achieving Codes for Symmetric Binary-InputMemoryless Channels’,IEEE Transactions on Information Theory,55(7),第3051–3073页”。

可以以系统或非系统的方式来编码极化码;并且存在用于这两种情况的校正子解码算法。因此,在本发明原理的第一和第二优选实施例中,极化码都可以用作信道码。极化码(系统或非系统形式)与校正子解码器一起使用构成了本发明的最优选实施例。下面简要讨论极化编码,以便描述极化码的校正子解码过程。

极化码是针对每个块长度N=2

并且

在非系统极化编码中,设置

本发明原理的最优选实施例采用系统极化编码。在极化码的系统编码中,通过设置

本发明原理的第一优选实施例需要用于非系统极化码的校正子解码器。存在许多可能的构造用于极化码的校正子解码器的方式。一种可能是从用于极化码的连续消除(SC)解码器开始,并通过修改其输入变量将其变成校正子解码器。接着描述该方法。

转到图6,示出了SC解码器610和SC校正子解码器660。SC解码器610包括第一输入601、第二输入602和输出603。在第一输入601处,SC解码器610接收冻结集

图6中的SC校正子解码器660包括第一输入661、第二输入602和输出663。SC校正子解码器660就它们的内部操作而言是SC解码器610的相同副本;两个解码器的区别仅在于它们相应的输入被准备以及它们相应的输出被解释。使l=(l

总之,不是使用在输入601和602处分别具有输入

图7示出了根据本公开的其中可以实现信道解码的示例无线网络。图7所示的无线网络700的实施例仅用于示出。在不脱离本公开的范围的情况下,可以使用无线网络700的其它实施例。无线网络700包括eNodeB(eNB)701、eNB 702和eNB 703。eNB 701与eNB 702和eNB 703通信。eNB 701还与至少一个互联网协议(IP)网络730通信,例如互联网、专有IP网络或其他数据网络。.

根据网络类型,可以使用其他公知的术语来代替“eNodeB”或“eNB”,例如“基站”或“接入点”。为了方便起见,在本专利文献中使用术语“eNodeB”和“eNB”来指代向远程终端提供无线接入的网络基础设施部件。而且,根据网络类型,可以使用其他公知术语来代替“用户设备”或“UE”,例如“移动站”(或“MS”)、“用户站”(或“SS”)、“远程终端”、“无线终端”或“用户装置”。为了方便起见,术语“用户设备”和“UE”在本专利文献中用来指代无线地接入eNB的远程无线设备,而不管UE是移动装置(例如移动电话或智能电话)还是通常被认为是固定装置(例如台式计算机或自动售货机)。

eNB 702为eNB 702的覆盖区域720内的多个第一用户设备(UE)提供对网络730的无线宽带接入。多个第一UE包括:UE 711,该UE可以位于小型企业(SB)中;UE 712,该UE可以位于企业(E)中;UE 713,该UE可以位于WiFi热点(HS)中;UE 714,该UE可以位于第一住宅(R)中;UE 715,该UE可以位于第二住宅(R)中;以及UE 716,该UE可以是移动装置(M),如蜂窝电话、无线膝上型电脑、无线个人数字助理(PDA)、平板电脑等。eNB 703为eNB 703的覆盖区域725内的多个第二UE提供对网络730的无线宽带接入。多个第二UE包括UE 715和UE716。在一些实施例中,eNB 701-703中的一个或多个可以使用3G、4G或5G、长期演进(LTE)、LTE-A、WiMAX或其它高级无线通信技术来彼此通信以及与UE 711-716通信。

虚线示出了覆盖区域720和725的大致范围,它们仅出于示出和说明的目的而被示出为大致圆形。应当清楚地理解,与eNB相关联的覆盖区域,例如覆盖区域720和725,可以具有其他形状,包括不规则形状,这取决于eNB的配置以及与自然和人为障碍相关联的无线电环境的变化。

如下面更详细地描述的,BS 701、BS 702和BS 703中的一个或多个包括如本公开的实施例中描述的2D天线阵列。在一些实施例中,BS 701、BS 702和BS 703中的一个或多个支持用于具有2D天线阵列的系统的码本设计和结构。

尽管图7示出了无线网络700的一个示例,但是可以对图7进行各种改变。例如,无线网络700可以包括任何合适的布置中的任何数量的eNB和任何数量的UE。而且,eNB 701可以直接与任意数量的UE进行通信,并且向这些UE提供对网络730的无线宽带接入。类似地,各个eNB 702和703可以直接与网络730通信,并且向UE提供对网络730的直接无线宽带接入。进一步地,eNB 701、702和/或703可以提供对其他或附加外部网络的接入,例如外部电话网络或其他类型的数据网络。

如下面进一步详细描述的,图中描绘的以及上文描述的示例信道解码系统可以在eNB(例如eNB 702)和/或UE(例如UE 716)中实现。

图8A示出了根据本公开的其中可以实现使用系统极化编码的HARQ的示例用户设备网络。图8A所示出的UE 716的实施例仅用于示出,并且图7的UE711-715可具有相同或类似的配置。然而,UE以各种各样的配置出现,并且图8A不将本公开的范围限制于UE的任何特定实现。

UE 716包括天线805、射频(RF)收发器810、发送(TX)处理电路815(其可以是图1中的发送子系统140的一部分)、麦克风820和接收(RX)处理电路825(其可以是图1中的接收子系统150的一部分)。UE 716还包括扬声器830、主处理器840、输入/输出(I/O)接口(IF)845、小键盘850、显示器855和存储器860。存储器860包括基本操作系统(OS)程序861和一个或多个应用862。OS程序861、应用862中的一个、或其某种组合可以实现如图1至图4和图6的各个实施例中描述的用于信道解码的编程。

RF收发器810从天线805接收由网络800的eNB发送的输入RF信号。RF收发器810可对输入RF信号进行下变频转换以生成将发送到接收器(Rx)处理电路825的中频(IF)信号或基带信号。Rx处理电路825将经处理的信号发送到扬声器830(例如用于语音数据)或发送到主处理器840以用于进一步处理(例如用于网络浏览数据)。

发送(Tx)处理电路815从麦克风820接收模拟或数字语音数据或从主处理器840接收其它输出基带数据(例如网络数据、电子邮件或交互式视频游戏数据),作为发送消息101的至少一些输入数据。Tx处理电路815实现信道编码。RF收发器810从Tx处理电路815接收输出的处理后的基带信号或IF信号,并将基带信号或IF信号上变频转换为经由天线805发送的RF信号。

主处理器840可以包括一个或多个处理器或其他处理装置,并且执行存储在存储器860中的基本OS程序861,以便控制UE 716的整体操作。例如,主处理器840可以根据公知的原理控制由RF收发器810、Rx处理电路825和Tx处理电路815进行的前向信道信号的接收和反向信道信号的发送。在一些实施例中,主处理器840包括至少一个可编程微处理器或微控制器,而在其他实施例中,主处理器包括专用电路(例如,用于系统和/或非系统编码或解码过程、穿孔过程、数据映射等)以及(可选地)可编程逻辑或处理电路。

主处理器840还能够执行驻留在存储器860中的其它进程和程序,例如用于如本公开的实施例中描述的具有2D天线阵列的系统的信道质量测量和报告的操作。主处理器840可以根据执行过程的需要将数据和/或指令移入或移出存储器860。在一些实施例中,主处理器840被配置为基于OS程序861或者响应于从eNB或运营商接收的信号来执行应用862。主处理器840还耦合到I/O接口845,该接口向UE 716提供连接到例如膝上型计算机和手持式计算机的其它装置的能力。I/O接口845是这些附件与主控制器840之间的通信路径。

主处理器840还耦合到小键盘(keypad)850(该小键盘可以简单地是单个按钮或者可以是按钮阵列或其它按钮组)和显示单元855。UE 716的操作者可以使用小键盘850来将数据录入到UE 716中。显示器855可以是触摸屏显示器或能够呈现文本和/或至少有限的图形(例如来自网站)并且根据已知实践接收用户的触摸输入的其他显示器。存储器860耦合到主处理器840,并且存储器860的至少一部分可以包括随机存取存储器(RAM),并且存储器860的另一部分可以包括闪存或其它只读存储器(ROM)。

尽管图12A示出了UE 1116的一个示例,但是可以对图12A进行各种改变。例如,图12A中的各种部件可以被组合、进一步细分或省略,并且可以根据特定需要添加附加部件。作为特定示例,主处理器1240可以被分成多个处理器,例如一个或多个中央处理单元(CPU)和一个或多个图形处理单元(GPU)。而且,虽然图12A示出了UE 1116被配置为移动电话或智能电话,但是UE可以被配置为作为其他类型的移动或固定装置来操作。

图8B示出了根据本公开的其中可以实现使用系统极化编码的HARQ的示例增强节点B(eNB)网络。图8B所示的eNB 702的实施例仅用于示出,并且图7的其他eNB可具有相同或类似的配置。然而,eNB以各种各样的配置出现,并且图8B不将本公开的范围限制于eNB的任何特定实现。注意,eNB 701和eNB 703可以包括与eNB 802相同或类似的结构。

如图8B所示,eNB 702包括多个天线870a-870n、多个RF收发器872a-872n、发送(Tx)处理电路874和接收(Rx)处理电路876。在某些实施例中,多个天线870a-870n中的一个或多个包括2D天线阵列。eNB 702还包括控制器/处理器878、存储器880以及回程或网络接口882。

RF收发器872a-872n从天线870a-870n接收输入RF信号,例如由UE或其它eNB发送的信号。RF收发器872a-872n对输入的RF信号进行下变频转换以生成IF信号或基带信号。IF信号或基带信号被发送到Rx处理电路876,该电路通过滤波、解码和/或数字化基带信号或IF信号来生成经处理的信号。Rx处理电路876将经处理的信号发送到控制器/处理器878以供进一步处理。

Tx处理电路874从控制器/处理器878接收模拟或数字数据(例如语音数据、网络数据、电子邮件或交互式视频游戏数据)作为输入数据分组11的至少一些输入数据。Tx处理电路874实施源编码器和信道编码器以编码、复用和/或数字化输出的基带数据以生成经处理的信号。RF收发器872a-872n从Tx处理电路874接收输出的经处理的信号,并且将基带信号或IF信号上变频转换为经由天线870a-870n发送的RF信号。

控制器/处理器878可以包括控制eNB 702的整体操作的一个或多个处理器或其他处理装置。例如,控制器/处理器878可以根据公知的原理控制由RF收发器872a-872n、Rx处理电路876和Tx处理电路874进行的前向信道信号的接收和反向信道信号的发送。控制器/处理器878也可支持附加功能,例如更高级的无线通信功能。控制器/处理器878可以在eNB702中支持多种其他功能中的任何功能。在一些实施例中,控制器/处理器878包括至少一个微处理器或微控制器,而在其他实施例中,主处理器包括专用电路(例如,用于系统和/或非系统编码过程、穿孔过程、数据映射等)以及(可选地)可编程逻辑或处理电路。

控制器/处理器878还能够执行驻留在存储器880中的程序和其它进程,例如基本OS。控制器/处理器878还能够支持如本公开的实施例中描述的具有2D天线阵列的系统的信道质量测量和报告。在一些实施例中,控制器/处理器878支持实体之间的通信。控制器/处理器878可以根据执行过程的需要将数据和/或指令移入或移出存储器880。

控制器/处理器878还耦合到回程或网络接口882。回程或网络接口882允许eNB702通过回程连接或通过网络与其他装置或系统通信。接口882可支持通过任何合适的有线或无线连接的通信。例如,当eNB 702被实现为蜂窝通信系统(例如支持3G、4G、5G、LTE或LTE-A的蜂窝通信系统)的一部分时,接口882可允许eNB 702通过有线或无线回程连接与其它eNB通信。当eNB 702被实现为接入点时,接口882可允许eNB 702通过有线或无线局域网或通过到更大网络(例如因特网)的有线或无线连接进行通信。接口882包括支持通过有线或无线连接的通信的任何合适的结构,例如以太网或RF收发器。

存储器880耦合到控制器/处理器878。存储器880的一部分可以包括RAM,并且存储器880的另一部分可以包括闪存或其他ROM。在某些实施例中,多个指令存储在存储器中。该多个指令被配置为使控制器/处理器878执行系统和/或非系统编码或解码过程、穿孔过程、数据映射等。

尽管图8B示出了eNB 702的一个示例,但是可以对图8B进行各种改变。例如,eNB702可以包括任意数量的所示的各个部件。作为特定示例,接入点可以包括多个接口882,并且控制器/处理器878可以支持路由功能以在不同网络地址之间路由数据。作为另一特定示例,虽然被示出为包括Tx处理电路874的单个实例和Rx处理电路876的单个实例,但是eNB702可以包括每个的多个实例(例如每个RF收发器有一个)。

虽然本文详细描述且在附图中描绘了用于使用经压缩的信道输出信息来解码数据的特定方法和系统,但应理解,本公开所涵盖的主题仅由权利要求书限制。尽管已经用示例性实施例描述了本公开,但是本领域技术人员可以提出各种改变和修改。旨在本公开涵盖落入所附权利要求的范围内的这样的改变和修改。本申请中的描述不应被理解为暗示任何特定的元件、步骤或功能是必须包括在权利要求范围中的必要或关键元件:专利主题的范围仅由允许的权利要求限定。而且,这些权利要求都不旨在关于所附权利要求或权利要求要素中的任一个来援引35USC§112(f),除非确切的词语“用于……的装置”或“用于……的步骤”被明确地用在特定权利要求中,随后是标识功能的分词短语。术语,例如(但不限于)“机构”、“模块”、“装置”、“单元”、“部件”、“元件”、“构件”、“设备”、“机器”、“系统”、“处理器”或“控制器”在权利要求内的使用被理解为并旨在指代相关领域的技术人员已知的结构,如由权利要求本身的特征进一步修改或增强的,并且不旨在援引35U.S.C.§112(f)。

- 使用压缩的信道输出信息来解码数据的方法和系统

- 图像处理装置、图像处理方法、动图像文件的数据结构、数据压缩装置、数据解码装置、数据压缩方法、数据解码方法及压缩动图像文件的数据结构