一种倒装LED芯片及其制作方法

文献发布时间:2023-06-19 12:14:58

技术领域

本发明涉及LED芯片技术领域,特别是涉及一种倒装LED芯片及其制作方法。

背景技术

蓝光LED的电压一般在2.5V~3.5V之间,而市电电压是220V,因此,高压芯片通过把LED芯片串并联之后,芯片电压提高,降低电压转换带来的损耗,同时在芯片端进行芯片的集成提高可靠性,芯片排布更密集,光强更集中。

现有的倒装高压芯片一般需要有三层电极结构,如图1所示,一层是接触层a,作用是跟外延层形成良好的欧姆接触;一层是连接层b,作用就是进行芯片间的串并连接;最后一层是用作焊接和散热的焊接层c。三层电极结构会造成电极之间存在高低差,在焊接以及散热的时候造成接触不良影响效果,此外,三层电极结构的生产成本高;此外,现有的电极结构通常采用锡合金,但倒装高压芯片焊接于镀有金或银的基板上,其主要是利用锡膏焊接,当基板被加热至适合的共晶温度时,基板上的金或银元素渗透到倒装高压芯片的电极结构,共晶固化并将倒装高压芯片焊于基板上,但锡膏具有很强的渗透性,在焊接过程中往往出现渗锡现象,严重影响芯片的性能。

发明内容

本发明要解决的技术问题是提供一种减少电极层数,且提高电极层抗锡渗透性的倒装LED芯片及其制作方法。

为了解决上述技术问题,本发明提供了一种倒装LED芯片,包括衬底和设于所述衬底上的多个串联连接的GaN基外延层单元,所述 GaN基外延层单元包括设于所述衬底上的N型GaN层和设于所述N 型GaN层上的P型GaN层,所述P型GaN层镀设有P型电极层,所述N型GaN层镀设有N型电极层,相邻的两个所述GaN基外延层单元中,上一个所述GaN基外延层单元的所述N型电极层通过连接电极层与下一个所述GaN基外延层单元的所述P型电极层连接;所述P型电极层、所述连接电极层和所述N型电极层均包括从上至下依次设置的Ti金属层、Ni金属层或Ni合金层、Au金属层、以及SnAu基合金层,所述SnAu基合金层由n层Sn金属层和n层Au金属层周期性交错设置形成,其中,n≥6。

作为本发明的优选方案,所述P型电极层、所述N型电极层和所述连接电极层均成型于同一蒸镀工序中。

作为本发明的优选方案,相邻的所述GaN基外延层单元之间设有隔离沟槽,所述隔离沟槽内沉积有第一保护层;所述连接电极层覆盖于所述第一保护层的顶面,所述连接电极层的两端分别与所述P型电极层和所述N型电极层连接。

作为本发明的优选方案,所述P型GaN层的顶面镀设有ITO层,所述ITO层上镀设有Ag层。

作为本发明的优选方案,还包括包覆所述GaN基外延层单元的第二保护层,所述第二保护层分别设有使所述P型电极层外露的P型导电孔和使串联下的最后一个所述N型电极层外露的N型导电孔。

作为本发明的优选方案,所述Ti金属层的厚度为2000埃~3000 埃;所述Ni金属层或Ni合金层的厚度为1000埃~3000埃;所述Au 金属层的厚度为2000埃~3000埃;所述SnAu基合金层的厚度大于或等于3微米,所述SnAu基合金层中的每层Sn金属层的厚度为2000 埃~5000埃,所述SnAu基合金层中的每层Au金属层的厚度为2000 埃~5000埃。

同时,本发明还提供了该倒装LED芯片的制作方法,包括以下步骤:

(1)、制作外延层,利用MOCVD设备在衬底上依次生长N型GaN层、发光量子阱和P型GaN层,完成GaN基外延层的制作;

(2)、在所述GaN基外延层上镀设ITO层,然后对所述ITO层和所述GaN基外延层进行刻蚀,使所述N型GaN层外露出来且使所述 GaN基外延层形成多个相互隔离的GaN基外延层单元;

(3)、在所述ITO层的表面镀上Ag层;

(4)、在相邻的所述GaN基外延层单元的间隙内沉积第一保护层;

(5)、蒸镀电极层,分别在所述ITO层上蒸镀P型电极层,在所述N型GaN层上蒸镀N型电极层,在所述第一保护层上蒸镀连接电极层,其中所述连接电极层的两端分别与所述P型电极层和所述N型电极层连接;

(6)、在所述GaN基外延层上沉积第二保护层,在所述第二保护层上刻蚀出使所述P型电极层外露的P型导电孔和使串联下最后一个所述N型电极层外露的N型导电孔。

作为本发明的优选方案,在步骤(2)中,先在所述GaN基外延层上刻蚀N型台阶使所述N型GaN层外露出来,再在所述GaN基外延层上刻蚀隔离沟槽,将整个所述GaN基外延层划分为多个隔离的所述GaN基外延层单元。

作为本发明的优选方案,在步骤(4)中,所述第一保护层沉积于所述隔离沟槽内。

作为本发明的优选方案,所述第一保护层和所述第二保护层的材质为SiO

实施本发明提供的一种倒装LED芯片及其制作方法,与现有技术相比较,其有益效果在于:P型电极层、连接电极层和N型电极层上的Ti金属层形成良好的欧姆接触并粘附在GaN基外延层单元上;Ni 金属层或Ni合金层能够作为抗锡渗透的阻挡层;Au金属层用于连接 Ni金属层或Ni合金层与SnAu基合金层;SnAu基合金层作为焊接层,其为多周期结构能够避免锡膏向下渗透至芯片;通过Ti金属层、Ni金属层或Ni合金层、Au金属层、以及SnAu基合金层的复合设计,能够提高电极层的抗锡渗透性,且电极层的内部结构牢固;该电极层结构使P型电极层、连接型电极层和N型电极层有效地同时充当接触层以及焊接层电极,整个倒装LED芯片只需分别镀上一层P型电极层、连接电极层和N型电极层即可实现GaN基外延层单元的串联连接,从而减少电极层的设置,由于电极层数减少,因此生产的工步减少,成本减少,制程加快,同时正负电极之间的高低差减少,有利于后续的焊接以及芯片的散热。

附图说明

图1现在大功率倒装芯片的结构示意图;

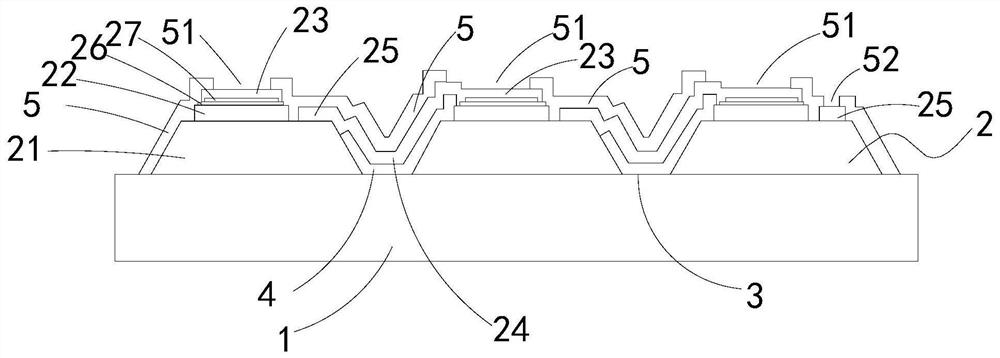

图2是本发明的结构示意图;

图3是P型电极层、连接电极层和N型电极层的结构示意图;

图4为采用本发明实施例的渗锡测试图;

图5为现有的大功率倒装芯片的渗锡测试图;

图6为采用本发明实施例的推力测试图;

图7为现有的大功率倒装芯片的推力测试图;

图中,1、衬底;2、GaN基外延层单元;21、N型GaN层;22、P型GaN层;23、P型电极层;231为Ti金属层;232为Ni金属层或 Ni合金层;233为Au金属层;234为SnAu基合金层;24、连接电极层;25、N型电极层;26、ITO层;27、Ag层;3、隔离沟槽;4、第一保护层;5、第二保护层;51、P型导电孔;52、N型导电孔;a、接触层;b、连接层;c、焊接层。

具体实施方式

下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。以下实施例用于说明本发明,但不用来限制本发明的范围。

在本发明的描述中,应当理解的是,本发明中采用术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

在本发明的描述中,应当理解的是,除非另有明确的规定和限定,本发明中采用术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

如图2-3所示,本发明实施例优选实施例的一种倒装LED芯片,包括衬底1和设于衬底1上的多个串联连接的GaN基外延层单元2, GaN基外延层单元2包括设于衬底1上的N型GaN层21和设于N型 GaN层21上的P型GaN层22,P型GaN层22镀设有P型电极层23, N型GaN层21镀设有N型电极层25,相邻的两个GaN基外延层单元 2中,上一个GaN基外延层单元2的N型电极层25通过连接电极层 24与下一个GaN基外延层单元2的P型电极层23连接,P型电极层23、连接电极层24和N型电极层25均包括从上至下依次设置的Ti金属层231、Ni金属层或Ni合金层232、Au金属层233、以及SnAu基合金层234,SnAu基合金层234由n层Sn金属层和n层Au金属层周期性交错设置形成,其中,n≥6。

本发明的工作原理为:相邻的两个GaN基外延层单元2中,上一个GaN基外延层单元2的N型电极层25通过连接电极层24与下一个 GaN基外延层单元2的P型电极层23连接,实现GaN基外延层单元2 的串联连接,P型电极层23、连接电极层24和N型电极层25均包括从上至下依次设置的Ti金属层231、Ni金属层或Ni合金层232、Au 金属层233、以及SnAu基合金层234,Ti金属层231形成良好的欧姆接触并粘附在GaN基外延层单元2上;Ni金属层或Ni合金层232能够作为抗锡渗透的阻挡层;Au金属层233用于连接Ni金属层或Ni合金层232与SnAu基合金层234;SnAu基合金层234作为焊接层,其为多周期结构能够避免锡膏向下渗透至芯片;通过的复合设计,能够提高电极层的抗锡渗透性,且电极层的内部结构牢固;该电极层结构使P型电极层23、连接型电极层和N型电极层25有效地同时充当接触层以及焊接层电极,整个倒装LED芯片只需分别镀上一层P型电极层23、连接电极层24和N型电极层25即可实现GaN基外延层单元2 的串联连接,从而减少电极层的设置,由于电极层数减少,因此生产的工步减少,成本减少,制程加快,同时正负电极之间的高低差减少,有利于后续的焊接以及芯片的散热。

示例性的,P型电极层23、N型电极层25和连接电极层24均成型于同一蒸镀工序中,由于P型电极层23、N型电极层25和连接电极层24的结构相同,因此在同一蒸镀工序中成型有助于提高生产效率。

示例性的,相邻的GaN基外延层单元2之间设有隔离沟槽3,隔离沟槽3内沉积有第一保护层4,连接电极层24覆盖于第一保护层4 的顶面,连接电极层24的两端分别与P型电极层23和N型电极层25 连接,便于连接电极层24的镀设,第一保护层4起到绝缘作用,避免连接电极层24将相邻的GaN基外延层单元2的N型GaN层21导通。

示例性的,P型GaN层22的顶面镀设有ITO层26,ITO层26上镀设有Ag层27,由于倒装高压芯片是背面出光,因此增加连接高反射率的Ag层27能提高亮度,同时还能提升连接的可靠性。

示例性的,所述Ti金属层的厚度为2000埃~3000埃;所述Ni金属层或Ni合金层的厚度为1000埃~3000埃;所述Au金属层的厚度为2000埃~3000埃;所述SnAu基合金层的厚度大于或等于3微米,所述SnAu基合金层中的每层Sn金属层的厚度为2000埃~5000埃,所述SnAu基合金层中的每层Au金属层的厚度为2000埃~5000埃。经多次实验证明,如图4所示,芯片焊接后在250℃环境下加热12小时后无渗锡现象,电极层抗锡渗透性效果好;而采用现有芯片,如图5所示,芯片焊接后在250℃环境下加热12小时后出现渗锡现象。而且本发明实施例提供的芯片焊接后,经推力测试,如图6所示,其断裂位置为芯片,而非电极处断裂,断裂层为芯片内部结构,由此可见,本发明的电极层的内部结构牢固,而采用现有芯片,芯片焊接后,经推力测试,如图7所示,断裂位置为电极,该电极内部结构相对不牢固。

示例性的,本发明还包括包覆GaN基外延层单元2的第二保护层 5,对GaN基外延层单元2进行保护,第二保护层5分别设有使P型电极层23外露的P型导电孔51和使串联下的最后一个N型电极层25 外露的N型导电孔52,便于P型电极层23和N型电极层25与电源连接,同时有助于GaN基外延层单元2的散热。

基于上面各项内容的倒装LED芯片的制作方法,包括以下步骤:

(1)、制作外延层,利用MOCVD设备在衬底1上依次生长N型 GaN层21、发光量子阱和P型GaN层22,完成GaN基外延层的制作;

(2)、在GaN基外延层上镀设ITO层26,然后对GaN基外延层进行刻蚀,使N型GaN层21外露出来且使GaN基外延层形成多个隔离的GaN基外延层单元2;

(3)、在ITO层26的表面镀上Ag层27;

(4)、在相邻的GaN基外延层单元2的间隙内沉积第一保护层4;

(5)、蒸镀电极层,分别在所述ITO层26上蒸镀P型电极层23,在所述N型GaN层21上蒸镀N型电极层25,在所述第一保护层4上蒸镀连接电极层24,其中所述连接电极层24的两端分别与所述P型电极层23和所述N型电极层25连接;

(6)在GaN基外延层上沉积第二保护层5,在第二保护层5上刻蚀出使P型电极层23外露的P型导电孔51和使串联下最后一个N型电极层25外露的N型导电孔52。

示例性的,在步骤(2)中,先在GaN基外延层上刻蚀N型台阶使N型GaN层21外露出来,再在GaN基外延层上刻蚀隔离沟槽3,将整个GaN基外延层划分为多个隔离的GaN基外延层单元2。

示例性的,在步骤(4)中,第一保护层4沉积于隔离沟槽内3,便于第一保护层3的沉积。

示例性的,第一保护层3和所述第二保护层5的材质为SiO

综上,本发明的倒装LED芯片能减少电极层数的设置,从而减少生产工序,提高效率,降低成本,同时能减少正负电极之间的高低差,有利于后续的焊接以及芯片的散热;并有效提高电极层的抗锡渗透性,且电极层的内部结构牢固。

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和替换,这些改进和替换也应视为本发明的保护范围。

- 一种LED倒装芯片、LED倒装芯片的图形化衬底及制作方法

- 一种高可靠性的倒装LED芯片、LED器件和LED芯片的制作方法