半导体封装及其制造方法

文献发布时间:2023-06-19 12:14:58

技术领域

本发明是关于一种半导体封装及其制造方法。

背景技术

半导体装置对于许多现代应用是必不可少的。随着电子技术的进步,半导体装置的尺寸越来越小,同时具有更大的功能和更多的集成电路。由于半导体装置的小型化,芯片堆叠封装技术现在被广泛用于制造半导体装置。在这种封装技术的生产过程中需执行许多制造步骤。

然而,以小型化规模制造的半导体装置变得越来越复杂。例如,将大量的微型MOS晶体管集成到一个小的芯片中,所形成的电路要比由分散在多个电子组件所构成的电路小,具有体积小、快速及成本低廉的优点。然而,随着对芯片中更小和更快的组件的需求,亦须使用较大的电流。当芯片的细小金属线以传输大电流的信号时,会导致未预期的信号失真和电源电压降(即IR降),并在芯片的接地或电源连接处产生杂讯。

发明内容

本发明的目的在于提供一种半导体封装,其具有梳型导电层提供具有较低电阻的电连接,从而防止了IR下降的问题。

根据本发明的一方面,提供一种半导体封装。半导体封装包含基板、半导体芯片、多个梳型导电层及多个引线。基板包含多个第一连接垫及多个第二连接垫与基板的第一边缘相邻,以及多个第三连接垫及多个第四连接垫与基板的第二边缘相邻,其中,第二边缘与第一边缘相对。半导体芯片设置在基板上,包含第一区域及第二区域,分别与第一边缘及第二边缘相邻。多个第五连接垫及多个第六连接垫设置在第一区域中,且多个第七连接垫及多个第八连接垫设置在第二区域中。第一梳型导电层及第二梳型导电层,设置在第一区域上,且第三梳型导电层及第四梳型导电层设置在第二区域上。多个第一引线及多个第五引线分别连接第一连接垫及第五连接垫至第一梳型导电层。多个第二引线及多个第六引线分别连接第二连接垫及第六连接垫至第二梳型导电层。多个第三引线及多个第七引线分别连接第三连接垫及第七连接垫至第四梳型导电层。多个第四引线及多个第八引线分别连接第四连接垫及第八连接垫至第三梳型导电层。

根据本发明的一些实施例,第一梳型导电层与第二梳型导电层相互交错,且第三梳型导电层与第四梳型导电层相互交错。

根据本发明的一些实施例,第一梳型导电层、第二梳型导电层、第三梳型导电层及第四梳型导电层中的每一个包含延第一方向延伸的基础部分、以及多个从基础部分延第二方向延伸的突出部分,其中第二方向与第一方向不同。

根据本发明的一些实施例,第一连接垫连接至电源,且第五连接垫为半导体芯片的电源连接垫。

根据本发明的一些实施例,第二连接垫接地,且第六连接垫为半导体芯片的接地电压连接垫。

根据本发明的一些实施例,第三连接垫接地,且第七连接垫为半导体芯片的的接地电压连接垫。

根据本发明的一些实施例,第四连接垫连接至电源,且第八连接垫为半导体芯片的电源连接垫。

根据本发明的一些实施例,第一区域及第二区域在中心线的相对两侧,第五连接垫及第六连接垫在第一区域中沿着中心线布置,且第七连接垫及第八连接垫在第二区域中沿着中心线布置。

根据本发明的一些实施例,半导体封装还包含粘着层设置于该半导体芯片与第一梳型导电层、第二梳型导电层、第三梳型导电层及第四梳型导电层之间。

根据本发明的一方面,提供一种半导体封装的制造方法。此方法包含以下步骤:提供基板,此基板包括多个第一连接垫及多个第二连接垫与基板的第一边缘相邻,以及多个第三连接垫及多个第四连接垫与基板的第二边缘相邻,其中第二边缘与第一边缘相对;在基板上放置半导体芯片,其中半导体芯片包含沿第一方向排列的多个第五连接垫及多个第六连接垫,以及沿第一方向排列且与第五连接垫及第六连接垫相邻的多个第七连接垫多个第八连接垫;在半导体芯片上放置第一梳型导电层,第二梳型导电层,第三梳型导电层及第四梳型导电层,其中第一梳型导电层及第二梳型导电层靠近第一边缘,第三梳型导电层及第四梳型导电层靠近第二边缘;形成多个第一引线连接第一连接垫及第一梳型导电层;形成多个第二引线连接第二连接垫及第二梳型导电层;形成多个第三引线连接第三连接垫及第四梳型导电层;形成多个第四引线连接第四连接垫及第三梳型导电层;形成多个第五引线连接第五连接垫及第一梳型导电层;形成多个第六引线连接第六连接垫及第二梳型导电层;形成多个第七引线连接第七连接垫及第四梳型导电层;以及形成多个第八引线连接第八连接垫及第三梳型导电层。

根据本发明的一些实施例,梳型导电层与第二梳型导电层相互交错,且第三梳型导电层与第四梳型导电层相互交错。

根据本发明的一些实施例,第一连接垫连接至电源,且第五连接垫为半导体芯片的电源连接垫;以及第二连接垫接地,且第六连接垫为半导体芯片的接地电压连接垫。

根据本发明的一些实施例,第三连接垫接地,且第七连接垫为半导体芯片的接地电压连接垫;以及其中第四连接垫连接至电源,且第八连接垫为半导体芯片的电源连接垫。

根据本发明的一些实施例,半导体芯片具有第一区域及与第一区域相邻的第二区域,第五连接垫及第六连接垫设置于第一区域中,第七连接垫及第八连接垫设置于第二区域中。

根据本发明的一些实施例,第一梳型导电层、第二梳型导电层、第三梳型导电层、及第四梳型导电层通过粘着层附接到半导体芯片。

与现有技术相比,本发明的半导体封装及其制造方法具有以下有益效果:半导体芯片和基板的电源接点和接地电压接点分别电连接到第一区域上的第一梳型导电层和第二梳型导电层,以及第二区域上的第三和第四梳型导电层,并且这些电源接点和接地电压接点与第一区域或第二区域相邻。半导体芯片和基板靠近第一区域或在第一区域中的电源接点和接地电压接点分别电连接到第一区域上方的第一和第二梳型导电层,并且靠近第二区域或在第二区域中的其他电源接点和接地电压接点分别电连接到第二区域上方的第三和第四梳型导电层。因此,梳型导电层可以通过引线同时连接至到右侧和左侧的连接垫上。梳型导电层提供具有较低电阻的电连接,从而防止了IR下降的问题。

应当理解,前述的一般性描述和下文的详细描述都是示例,并且旨在提供对所要求保护的本揭示内容的进一步解释。

附图说明

当结合随附附图阅读时,将自下文的详细描述最佳地理解本发明的方面。应注意,根据工业中的标准实务,并未按比例绘制各特征。事实上,为了论述清楚,可任意增加或减小各特征的尺寸。

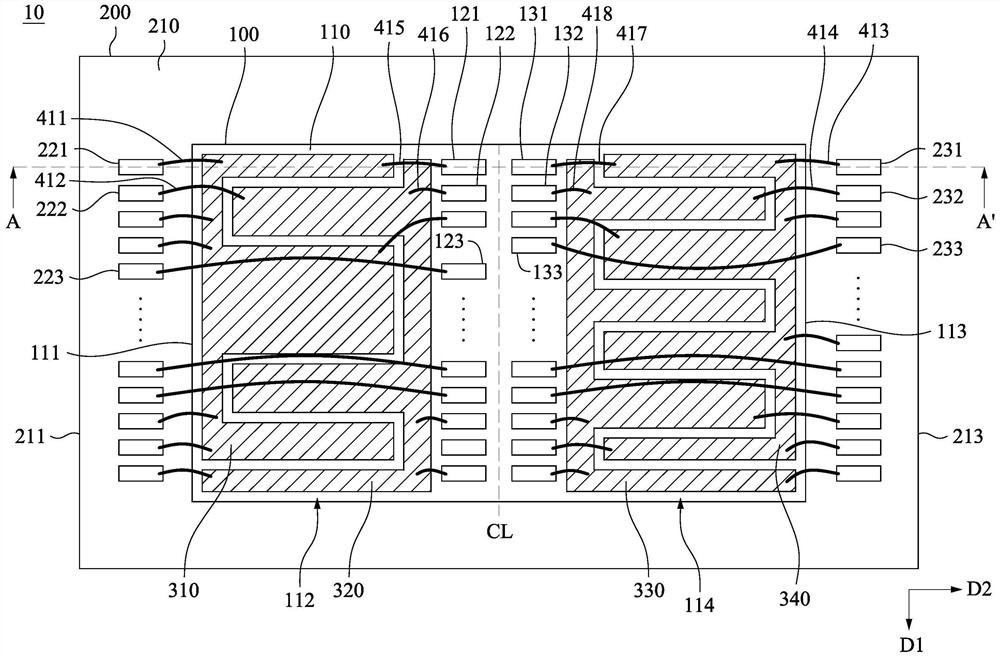

图1为根据本发明的某些实施方式绘示的半导体封装的制程中的各步骤的俯视图。

图2为根据本发明的某些实施方式绘示的半导体封装的制程各步骤的俯视图。

图3显示根据图2A-A'截线所视的剖面图。

图4为根据本发明的某些实施方式绘示的半导体封装的制程各步骤的俯视图。

图5显示根据图4A-A'截线所视的剖面图。

图6为根据本发明的某些实施方式绘示的半导体封装的制程中的各步骤的俯视图。

图7显示根据图6A-A'截线所视的剖面图。

主要附图标记说明:

10-半导体封装,100-半导体芯片,110-上表面,111-第一边缘,112-第一区域,113-第二边缘,114-第二区域121-第五连接垫,122-第六连接垫,123-信号垫,131-第七连接垫,132-第八连接垫,133-信号垫,200-基板,210-上表面,211-第一边缘,213-第二边缘,221-第一连接垫,222-第二连接垫,223-信号垫,231-第三连接垫,232-第四连接垫,233-信号垫,302、304-粘着层,310-第一梳型导电层,320-第二梳型导电层,330-第三梳型导电层,340-第四梳型导电层,310a、320a、330a、340a-基础部分,310b、320b、330b、340b-突出部分,411-第一引线,412-第二引线,413-第三引线,414-第四引线,415-第五引线,416-第六引线,417-第七引线,418-第八引线,A-A’-截线,CL-中心线,D1-第一方向,D2-第二方向。

具体实施方式

为了使本揭示内容的叙述更加详尽与完备,下文针对了本揭示内容的实施方面与具体实施例提出了说明性的描述,但这并非实施或运用本揭示内容具体实施例的唯一形式。以下所公开的各实施例,在有益的情形下可相互组合或取代,也可在一实施例中附加其他的实施例,而无须进一步的记载或说明。在以下描述中,将详细叙述许多特定细节以使读者能够充分理解以下的实施例。然而,可在无此等特定细节的情况下实践本揭示内容的实施例。

再者,空间相对用语,例如“下方”、“之下”、“上方”、“之上”等,这是为了便于叙述一元件或特征与另一元件或特征之间的相对关系,如图中所绘示。这些空间上的相对用语的真实意义包含其他的方位。例如,当图示上下翻转180度时,一元件与另一元件之间的关系,可能从“下方”、“之下”变成“上方”、“之上”。此外,本文中所使用的空间上的相对叙述也应作同样的解释。

根据本发明的部分实施例,一种制造半导体封装的方法说明如下:

请参考图1,准备半导体封装的步骤从提供半导体芯片100开始。半导体芯片100可以包括由半导体材料制成的半导体基板,该半导体材料包括但不限于块状硅、半导体芯片、绝缘体上硅(silicon-on-insulator,SOI)基板或硅锗基板。也可以使用包括III族、IV族和V族元素的其他半导体材料。

半导体芯片100可以包含电子层。电子层可以包括多个微电子元件。微电子元件的示例包括晶体管(例如,金属氧化物半导体场效应晶体管(MOSFET)、互补金属氧化物半导体晶体管(CMOS)、双极型接面晶体管(BJT)、高压晶体管、高频晶体管、p通道和/或n通道场效应晶体管(PFET/NFET)等);电阻器二极管;电容器;电感器;保险丝;和其他合适的装置。各种加工可用于形成上述微电子元件,包括沉积、蚀刻、注入、微影、退火和其他合适的加工。微电子元件互连以形成集成电路,例如逻辑装置、储存装置(例如SRAM)、射频装置、输入/输出(I/O)装置、系统整合芯片(system-on-chip,SOC)装置、系统芯片(system-in-chip,SIC)装置、动态存取记忆体(dynamic random-access memory,DRAM),其组合以及其他合适类型的装置。

如图1所示,半导体芯片100包含两行连接垫。例如,多个连接垫121、122、131、132形成在半导体芯片100的上表面110上。连接垫121、122可以沿着第一方向D1布置,连接垫131、连接垫132也沿着第一方向D1布置,且分别与连接垫121、122相邻。在一些实施方式中,半导体芯片100的上表面110分为第一区域112以及与第一区域112相邻的第二区域114。第一区域112和第二区域114位于中心线CL的两相对侧。第一区域112从中心线CL延伸到半导体芯片100的第一边缘111,第二区域114从中心线CL延伸到半导体芯片100的第二边缘113。连接垫121、122设置在第一区域112中,连接垫131、132设置在第二区域114中。在一些实施方式中,连接垫121、122、131、132电性连接半导体芯片100中的微电子元件。具体而言,连接垫121、122可以在第一区域112中沿着中心线CL对准,连接垫131、132可以在第二区域114中沿着中心线CL对准。

连接垫121、122、131、132代表形成在半导体芯片表面附近的各种端子中的任何一个,芯片中的集成电路通过该端子与外部电路之间进行电连接。例如,连接垫121可以为电源接点(也称为第五连接垫),连接垫122可以是接地电压接点(也称为第六连接垫)。例如,连接垫131可以为接地电压接点(也称为第七连接垫),连接垫132可以是电源接点(也称为第八连接垫)。在一些实施例中,半导体芯片100包括多个电源接点和多个接地电压接点;然而,为了清楚起见,其他连接垫未用附图标记表示。

在一些实施方式中,半导体芯片100还包含多个信号垫123、133。如图1所示,信号垫123可以设置在第一区域112中并与第五连接垫121及第六连接垫122对齐,信号垫133可以设置在第二区域114中并与第七连接垫131及第八连接垫132对齐。为了清楚起见,其他信号垫未用附图标记表示。

请参考图2及图3,准备半导体封装的步骤还包含放置半导体芯片100于基板200上。具体而言,半导体芯片100放置在基板200的上表面210上。在一些实施方式中,基板200可以为印刷电路板、陶瓷、有机物、玻璃和/或半导体材料或结构,以提供电源、接地、控制、监视等功能的基础。

如图2所示,基板200包含多个连接垫,例如连接垫221、连接垫222、连接垫231、连接垫232以将电子信号导向半导体芯片100或从半导体芯片100导回电子信号。连接垫221及连接垫222与基板200的第一边缘211相邻,连接垫231及连接垫232与基板200的第二边缘213相邻,且第二边缘213与第一边缘211。具体而言,连接垫221及连接垫222可以位于基板200的第一边缘211和半导体芯片100的第一边缘111之间,连接垫231及连接垫232位于基板200的第二边缘213和半导体芯片100的第二边缘113之间。

在一些实施方式中,连接垫221及连接垫222在与第一边缘111垂直的直线上分别与半导体芯片100的连接垫121及连接垫122对齐。类似地,在一些实施方式中,连接垫231及连接垫232在与第二边缘111垂直的直线上分别与半导体芯片100的连接垫131及连接垫132对齐。例如,连接垫221、连接垫121、连接垫131及连接垫231沿着与第一边缘111垂直的直线布置。此外,连接垫2212、连接垫122、连接垫132及连接垫232沿着与第二边缘1113垂直的另一直线布置。

在一些实施方式中,互相对准的连接垫具有相关的功能。例如,如图2所示,与第五连接垫121(电源接点)对准的连接垫221连接至电源,与第六连接垫122(接地连接垫)对准的连接垫222接地。此外,与连接垫131(接地连接垫)对准的连接垫231接地,与连接垫132(电源接点)对准的连接垫232连接至电源。然而,基板200上的连接垫的电性功能并不限于上述实施方式。

为了简洁起见,在以下的叙述中,连接至电源且与第一边缘211相邻的连接垫221称为“第一连接垫”,接地且与第一边缘211相邻的连接垫222称为“第二连接垫”,接地且与第二边缘213相邻的连接垫232称为“第三连接垫”,连接至电源且与第二边缘213相邻的连接垫232称为“第四连接垫”。

在一些实施方式中,基板200还包含多个信号垫223及信号垫233。如图2所示,信号垫223可以与第一连接垫221及第二连接垫222对齐,信号垫233可以与第三连接垫231及第四连接垫232对齐。为了清楚起见,其他信号垫未用附图标记表示。

请参考图4及图5。制造半导体封装还包含放置第一梳型导电层310、第二梳型导电层320、第三梳型导电层330及第四梳型导电层340于半导体芯片100上。如图4所示,第一梳型导电层310及第二梳型导电层320设置在上表面110的第一区域112上,第三梳型导电层330及第四梳型导电层340设置在上表面110的第二区域114上。

在一些实施方式中,第一梳型导电层310与第二梳型导电层320相互交错,第三梳型导电层330与第四梳型导电层340相互交错。此外。第一梳型导电层310及第二梳型导电层320彼此分离。相似地,第三梳型导电层330及第四梳型导电层340彼此分离。

在一些实施方式中,第一梳型导电层310、第二梳型导电层320、第三梳型导电层330及第四梳型导电层340中的每一个包含延第一方向D1延伸的基础部分、以及多个从基础部分延第二方向D2延伸的突出部分。例如,第一梳型导电层310具有基础部分310及多个突出部分310b。基础部分310a接近第一边缘111并沿第一方向D1延伸,突出部分310从基础部分310a沿第二方向D2延伸,且第二方向D2与第一方向D1不同。第二梳型导电层320具有基础部分320a及多个突出部分320b.基础部分320a接近第五连接垫121及第六连接垫122,并沿第一方向D1延伸。突出部分320b从基础部分320a沿第二方向D2延伸。类似地,第三梳型导电层330具有基础部分330a沿第一方向D1延伸,并接近第七连接垫131及第八连接垫132,以及多个突出部分330从基础部分330a沿着第二方向D2延伸。第四梳型导电层340具有沿着第一方向D1延伸并接近第二边缘113的基础部分340a,以及多个从基础部分340沿着第二方向D2延伸的突出部分340b。

应了解到,图4所示的梳型导电层仅为示例,且不旨在限制本发明。因此,应了解到,可根据需求选择梳型导电层的突出部分的尺寸及数量。

在一些实施方式中,第一梳型导电层310、第二梳型导电层320、第三梳型导电层330及第四梳型导电层340的材料可以包含金属如铜或铝,或具有低电阻率的其他金属。

第一梳型导电层310、第二梳型导电层320、第三梳型导电层330、及第四梳型导电层340可以通过合适的技术形成在半导体芯片100上。例如,如图5所示,第一梳型导电层310及第二梳型导电层320通过粘着层302连接至半导体芯片100,且第三梳型导电层330及第四梳型导电层340通过粘着层304连接至半导体芯片100。粘着层302设置在第一梳型导电层310、第二梳型导电层320与半导体芯片100之间,粘着层304设置在第三梳型导电层330、第四梳型导电层340与半导体芯片100之间。粘着层302及粘着层304使第一梳型导电层310、第二梳型导电层320、第三梳型导电层330和第四梳型导电层340与半导体芯片100绝缘。换句话说,粘着层302及粘着层304包括绝缘材料,并且被添加在梳型导电层和半导体芯片100之间以防止短路。

在一些实施方式中,第一梳型导电层310及第二梳型导电层320的上表面与第三梳型导电层330及第四梳型导电层340的上表面齐平。在一些实施方式中,粘着层302及粘着层304可以为粘合膜或胶。

请参考图6及图7,准备半导体封装还包含执行打线制程。在一些实施方式中,使用多个引线来提供半导体芯片100和基板200之间的电连接。下方描述用于上述实施例的半导体芯片100和基板200的打线制程的一个实施例。可以理解,可以提供另外的引线来连接半导体芯片100和基板200,并且可以减少下方描述的一些引线。操作的顺序可以互换,并且至少一些操作可以以不同的顺序执行。在一些实施例中,至少两个或更多个操作/过程在时间上重叠或几乎同时地执行。

打线制程包括:

(a)形成多个第一引线411连接第一连接垫221及第一梳型导电层310;

(b)形成多个第二引线412连接第二连接垫222及第二梳型导电层320;

(c)形成多个第三引线413连接第三连接垫231及第四梳型导电层340;

(d)形成多个第四引线414连接第四连接垫232及第三梳型导电层330;

(e)形成多个第五引线415连接第五连接垫121及第一梳型导电层310;

(f)形成多个第六引线416连接第六连接垫122及第二梳型导电层320;

(g)形成多个第七引线417连接第七连接垫131及第四梳型导电层340;以及

(h)形成多个第八引线418连接第八连接垫132及第三梳型导电层330。

在一些实施方式中,进一步形成多条信号线以连接基板200上的信号垫和半导体芯片100上的信号垫。例如,信号垫223通过一条信号线连接至信号垫123,信号垫233通过另一条信号线连接至信号垫133。在一些实施方式中,信号线可以分别穿过粘着层302和粘着层304以连接信号垫。即,信号线的一部分可以掩埋在粘着层302和粘着层304中。

在一些实施方式中,准备半导体封装还包含通过封装材料(未绘示于图中)封装半导体芯片100、基板200、第一梳型导电层310、第二梳型导电层320、第三梳型导电层330及第四梳型导电层340、第一引线411、第二引线412、第三引线413、第四引线414、第五引线415、第六引线416、第七引线417及第八引线418。封装材料可以包含热固性环氧树脂。如此完成半导体封装10。

在一些实施方式中,第一连接垫221连接至电源,且第五连接垫121连接至电源,且第五连接垫121为半导体芯片221连接至电源,且第五连接垫121为半导体芯片100的电源接点。通过第一引线411和第五引线415,基板200和半导体芯片100之间的Vdd(电源)信号经由第一梳型导电层稳定地传输。如此一来,由于第一梳型导电层310提供了具有较低电阻的电连接,因此防止了Vdd(电源)信号的IR下降问题。

类似地,在一些实施方式中,第四连接垫232连接至电源,且第八连接垫132为半导体芯片100的电源接点。通过第四引线414和第八引线418,基板200和半导体芯片100之间的Vdd(电源)信号经由第三梳型导电层330稳定地传输。如此一来,由于第三梳型导电层330提供了具有较低电阻的电连接,因此防止了Vdd(电源)信号的IR下降问题。

在一些实施方式中,第二连接垫222接地或连接到电源的接地电压,并且第六连接垫122是半导体芯片100的接地电压接点。通过第二引线412和第六引线416,基板200和半导体芯片100之间的接地信号通过第二梳型导电层320稳定地传输。如此一来,第二梳型导电层320提供了具有较低电阻的电连接,从而防止了接地信号的IR下降问题。

类似地,在一些实施方式中,第三连接垫231接地或连接到电源的接地电压,并且第七连接垫131是半导体芯片100的接地电压接点。通过第三引线413和第七引线417,基板200和半导体芯片100之间的接地信号通过第四梳型导电层340稳定地传输。

此外,第一梳型导电层310、第二梳型导电层320、第三梳型导电层330及第四梳型导电层340可以防止半导体芯片100受到电磁干扰和静电放电(ESD)。

如上所述,根据本揭示的实施方式,提供一种半导体封装及其制造方法。在本发明的实施方式中,将具有两行连接垫在中心线的相对两侧的半导体芯片放置在基板上。梳型导电层设置在半导体芯片上,并且位于两行连接垫的相对侧(即第一区域和第二区域)。梳型导电层提供具有较低电阻的电连接,从而防止了IR下降的问题。此外,半导体芯片和基板的电源接点和接地电压接点分别电连接到第一区域上的第一梳型导电层和第二梳型导电层,并且这些电源接点和接地电压接点与第一区域相邻。类似地,半导体芯片和基板靠近第二区域或在第二区域中的其他电源接点和接地电压接点分别电连接到第二区域上方的第三和第四梳型导电层。因此,梳型导电层可以通过引线同时连接至到右侧和左侧的连接垫上。

尽管本揭示内容已根据某些实施方式具体描述细节,其他实施方式也是可行的。因此,权利要求的精神和范围不应限于本文所记载的实施方式。

本领域技术人员也应当理解,在不脱离本揭示内容的精神和范围的情况下,对于本揭示内容所做的各种修改和变形是可行的。根据前述内容,本揭示内容旨在涵盖可落入权利要求范围内的本揭示内容中的各种修改和变形。

- 半导体封装体制造用支承体、半导体封装体制造用支承体的使用及半导体封装体的制造方法

- 半导体封装衬底及其制造方法、半导体封装及其制造方法