一种应用于模块电源初级侧的均流控制电路

文献发布时间:2023-06-19 12:16:29

技术领域

本发明属于电路设计技术领域,具体涉及一种应用于模块电源初级侧的均流控制电路。

背景技术

高功率密度、高可靠性DC/DC模块电源,被广泛应用,但是模块电源在使用时常需要并联备份冗余或功率倍增。

目前的处理方法是:

1、采用含有均流功能的电源模块,即在次级侧增加均流母线引脚,在多模块并联时,通过均流母线引脚相连。

2、在模块电源原边均流的,但一般电路简单,多用于民用设备。

但是,目前的处理方法均流精度不高,不能应用在高精度、高可靠性的电子设备中。

发明内容

本发明的目的在于提供一种应用于模块电源初级侧的均流控制电路,以解决上述的技术问题。

为实现上述目的,本发明提供如下技术方案:一种应用于模块电源初级侧的均流控制电路,其中,包括:延时电路及初级侧电流采样电路;所述延时电路延时控制均流开关的导通和关断,防止电源启动时的误动作;所述初级侧电流采样电路对初级侧电流进行采样并与初级侧电流放大电路连接,且所述初级侧电流放大电路对输入电流信号进行放大;所述初级侧电流放大电路输出端与电流误差放大器输入端连接;所述电流误差放大器比较本电源初级侧的电流与本电源并联的其他电源初级侧的电流差异,并对误差信号放大;所述误差信号经电阻衰减网络调节并驱动可变电抗器,调整PWM控制器的COMP脚电压,从而调节PWM控制器的占空比,调整输出电压,达到调节输出电流。

优选的,所述延时电路包括:电阻R13、电阻R20及电容C10;所述电阻R13一端连接电源端+Vp1,另一端连接电阻R20、电容C10及均流开关,且所述电阻R20、电容C10另一端接地-Vin。

优选的,所述均流开关包括:MOS管Q2及反相器;

所述反相器包括:单元一三极管U2A、单元二三极管U2B、电阻R11、电阻R12及电阻R19;

所述单元一三极管U2A第1脚接地-Vin;

所述单元一三极管U2A第2脚连接延时电路;

所述单元一三极管U2A第6脚连接电阻R12、电阻R19及单元二三极管U2B第5脚,所述电阻R12另一端连接电源端+Vp1,且所述电阻R19另一端接地-Vin;

所述单元二三极管U2B第4脚接地-Vin;

所述单元二三极管U2B第3脚连接MOS管Q2的第1脚及电阻R11,且所述R11的另一端连接电源端+Vp1。

优选的,所述初级侧电流放大电路包括:第二运放单元U1B、电阻R1、电阻R2、电阻R3、电阻R4、电容C1、电容C2、电容C3及电容C4;

所述第二运放单元U1B第4脚接地-Vin;

所述第二运放单元U1B第5脚连接电阻R1、电阻R2、电容C1及电容C2,且所述电阻R2及电容C1另一端接地-Vin;

所述电阻R1另一端连接初级侧电流采样电路的正端,且所述电容C2另一端连接第二运放单元U1B第6脚;

所述第二运放单元U1B第6脚连接电阻R3、电阻R4、电容C2及电容C4,所述电阻R3另一端连接初级侧电流采样电路的负端,且所述电阻R4及电容C4另一端连接第二运放单元U1B第7脚;

所述第二运放单元U1B第7脚连接电容C3,且所述电容C3另一端接地-Vin。

优选的,所述电阻R1与电阻R3阻值相等,且所述电阻R2与电阻R4阻值相等;所述电容C1与电容C4容量相等;所述电阻R4与电阻R3的比值决定电流放大倍数。

优选的,所述电流误差放大器包括:第一运放单元U1A、电阻R7、电阻R8、电阻R9、电阻R16、电阻R17、电阻R18、电容C5、电容C6及电容C9;

第一运放单元U1A第2脚连接电阻R7、电阻R9及电容C6,且电阻R7另一端连接第一运放单元U1A第8脚;

所述电容C6另一端连接电阻R8,且电阻R8另一端连接第一运放单元U1A第1脚;

第一运放单元U1A第3脚连接电阻R17、电阻R18、电容C9及均流开关,且所述电阻R18另一端接地-Vin;

所述电容C9另一端连接电阻R16,且所述电阻R16另一端接地-Vin;

第一运放单元U1A第8脚连接电容C5、电阻R7及磁珠FB1,所述磁珠FB1另一端连接电源+Vp3,且所述电容C5另一端接地-Vin;

所述电阻R9及电阻R17另一端连接初级侧电流放大电路输出端。

优选的,所述电阻衰减网络为线性分压电路,为可变电抗器提供合适的驱动电压。

优选的,所述电阻衰减网络包括:电阻R10及电阻R15。

优选的,所述可变电抗器包括:MOS管Q1及电阻R5。

优选的,所述可变电抗器输出阻抗与输入驱动电压呈单调变化曲线;当输入驱动电压减小时,输出阻抗减小;当输入驱动电压增大时,输出阻抗增大。

本发明的技术效果和优点:该应用于模块电源初级侧的均流控制电路:

1、采用受控阻抗调整PWM控制器的COMP脚电位,实现均流控制,达到各个并联模块输出电流均衡的目的;

2、采用初级侧均流,有利于优化电路,提高产品的可靠性。

附图说明

图1为初级侧电流采样电路简图;

图2为初级侧电流放大电路原理图;

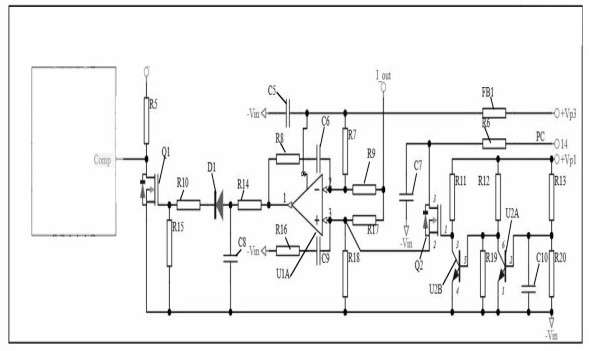

图3为初级侧均流控制电路原理图。

具体实施方式

下面将结合本发明实施例中的附图1-3,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

在本发明中芯片U1含有两个相同的功能单元电路,即两通道运放,组成单元为U1A及U1B,采用复合芯片U1可以减少元器件数量。

并且,在本发明中芯片U2内部为两个相同的单元,即单元一三极管U2A及单元二三极管U2B,采用复合芯片U2可以减少元器件数量。

其中:单元一三极管U2A第1脚为发射极、单元一三极管U2A第2脚为基极、单元一三极管U2A第6脚为集电极;单元二三极管U2B第3脚为集电极、单元二三极管U2B第4脚为发射极、单元二三极管U2B第5脚为基极。

参见图1,图1为初级侧电流采样电路简图,其中,左侧为电源输入,右侧为电源输出,Rs1为初级侧电流采样电阻,初级侧电流为Ips,经初级侧电流采样电阻转换为误差电压Vps。

在本发明中,初级侧电流采样电路的正端与电阻R1连接,电阻R1另一端与初级侧电流放大电路中的第二运放单元U1B第5脚连接;初级侧电流采样电路的副端与电阻R3连接,电阻R3另一端与初级侧电流放大电路中的第二运放单元U1B第6脚连接。

参见图2,图2为初级侧电流放大电路原理图,其中,包括:第二运放单元U1B、电阻R1、电阻R2、电阻R3、电阻R4、电容C1、电容C2、电容C3及电容C4,构成对称差分放大器。

所述第二运放单元U1B第4脚接地-Vin;所述第二运放单元U1B第5脚连接电阻R1、电阻R2、电容C1及电容C2,且所述电阻R2及电容C1另一端接地-Vin;所述电阻R1另一端连接初级侧电流采样电路的正端,且所述电容C2另一端连接第二运放单元U1B第6脚;所述第二运放单元U1B第6脚连接电阻R3、电阻R4、电容C2及电容C4,所述电阻R3另一端连接初级侧电流采样电路的负端,且所述电阻R4及电容C4另一端连接第二运放单元U1B第7脚;所述第二运放单元U1B第7脚连接电容C3,且所述电容C3另一端接地-Vin。

在本发明中,电阻R1与电阻R3阻值相等,且电阻R2与电阻R4阻值相等,并且电容C1与电容C4容量相等,则,根据初级侧电流放大电路原理图,可以得知电阻R4与电阻R3的比值决定电流放大倍数,本领域技术人员可以根据实际电路或布局对电阻R4与电阻R3的比值进行调整,以满足实际控制逻辑的需要。

参见图3,图3为初级侧均流控制电路原理图,其中,包括:延时电路及初级侧电流采样电路;所述延时电路延时控制均流开关的导通和关断,防止电源启动时的误动作;所述电流误差放大器比较本电源初级侧的电流与本电源并联的其他电源初级侧的电流差异,并对误差信号放大;所述误差信号经电阻衰减网络调节并驱动可变电抗器,调整PWM控制器的COMP脚电压,从而调节PWM控制器的占空比,调整输出电压,实现均流控制,达到各个并联模块输出电流均衡的目的。

具体的,所述延时电路包括:电阻R13、电阻R20及电容C10,所述电阻R13一端连接电源端+Vp1,另一端连接电阻R20、电容C10及单元一三极管U2A第2脚,且所述电阻R20、电容C10另一端接地-Vin,电源端+Vp1经电阻R13对电容C10充电,使电容C10上电压上升,能够延时控制均流开关的导通与关断,防止电源启动时的误动作。

具体的,所述均流开关包括:MOS管Q2及反相器;

所述反相器包括:单元一三极管U2A、单元二三极管U2B、电阻R11、电阻R12及电阻R19;

所述单元一三极管U2A第1脚为发射极,且接地-Vin;所述单元一三极管U2A第2脚连接延时电路中的电阻R13;

所述单元一三极管U2A第6脚连接电阻R12、电阻R19及单元二三极管U2B第5脚,所述电阻R12另一端连接电源端+Vp1,且所述电阻R19另一端接地-Vin;

所述单元二三极管U2B第4脚接地-Vin;

所述单元二三极管U2B第3脚为集电极,且连接MOS管Q2的第1脚及电阻R11,且所述R11的另一端连接电源端+Vp1。

具体的,所述电流误差放大器包括:第一运放单元U1A、电阻R7、电阻R8、电阻R9、电阻R16、电阻R17、电阻R18、电容C5、电容C6及电容C9;

第一运放单元U1A第2脚为输入负,且连接电阻R7、电阻R9及电容C6,且电阻R7另一端连接第一运放单元U1A第8脚,即芯片电源脚,所述电容C6另一端连接电阻R8,且电阻R8另一端连接第一运放单元U1A第1脚,即运放输出端。

第一运放单元U1A第3脚为输入正,且连接电阻R17、电阻R18、电容C9及MOS管Q2的第2脚,且所述电阻R18另一端接地-Vin,所述电容C9另一端连接电阻R16,且所述电阻R16另一端接地-Vin。

第一运放单元U1A第8脚为芯片供电脚,且连接电容C5、电阻R7及磁珠FB1,所述磁珠FB1另一端连接电源+Vp3,且所述电容C5另一端接地-Vin。

所述电阻R9及电阻R17另一端连接初级侧电流放大电路中第二运放单元U1B第7脚,即电流放大输出端I_out。

具体的,所述电阻衰减网络为线性分压电路,为可变电抗器提供合适的驱动电压,所述电阻衰减网络包括:电阻R10及电阻R15。

具体的,所述可变电抗器包括:MOS管Q1及电阻R5,所述可变电抗器输出阻抗与输入驱动电压呈单调变化曲线;当输入驱动电压减小时,输出阻抗减小;当输入驱动电压增大时,输出阻抗增大,从而影响调整PWM控制器COMP脚的电压。

在本发明中,还包括:电阻R14及电容C8,电阻R14及电容C8构成低通滤波器,用于滤除电流误差放大器输出的高频干扰噪声。

在本发明中,本领域技术人员可以根据实际电路或布局灵活应用,在电流误差放大器的输出端与可变电抗器之间添加二极管D1,只允许正电压通过。达到整流的目的。

工作原理,该应用于模块电源初级侧的均流控制电路控制与调节过程如下:

步骤1、在电源上电启动时,因电容C10上没有电荷,且电容C10电压不能突变,故,单元一三极管U2A的基极及发射极无偏置电压而截止;

则,单元二三极管U2B的基极因电阻R12和电阻R19分压得到大于开启阀值电压而饱和导通,将MOS管Q2的栅极电位拉低;

则,均流开关截止。

步骤2、随着电源端+Vp1对电容C10充电至单元一三极管U2A的开启阀值电压时,单元一三极管U2A饱和导通,将单元二三极管U2B的基极电位拉低;

则,单元二三极管U2B失去偏置电压而截止,MOS管Q2因上偏置电阻R11正向导通;

则,均流开关导通。

步骤3、本电源初级侧电流放大电路的输出端与本电源并联的其他初级侧电流放大电路的输出端与电流误差放大器输入端连接。

步骤4、当本电源初级侧电流大于与本电源并联的其他初级侧电流时,第一运放单元U1A输出电压上升,经电阻衰减网络后,由于电阻衰减网络为线性分压电路,可变电抗器输出阻抗与输入驱动电压呈单调变化曲线;

则,MOS管Q1的驱动电压上升,MOS管Q1的导通电阻增大。

步骤5、当MOS管Q1的导通电阻增大,PWM控制器的COMP脚电压上升,由芯片特性可知,PWM输出的占空比将适当增加,输出电压上拉,输出功率上升,输入电流上调,自动达到本电源电流与本电源并联的其他电源电流接近,达到各个并联模块输出电流均衡的目的。

步骤6、反之,当本电源初级侧电流小于与本电源并联的其他初级侧电流时,调节过程与上述相反,自动达到本电源电流与本电源并联的其他电源电流接近,达到各个并联模块输出电流均衡的目的。

最后应说明的是:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种应用于模块电源初级侧的均流控制电路

- 一种应用于模块电源初级侧的均流控制电路