微型半导体元件

文献发布时间:2023-06-19 12:16:29

技术领域

本发明涉及一种半导体元件,尤其涉及一种微型半导体元件。

背景技术

一般而言,在制作微型半导体元件的电极时,使用到的工艺(如干刻蚀工艺)容易于电极周围产生表面缺陷(defect),如此一来,当电流于电极之间流动时,电流载子(如电子/空穴)与这些表面缺陷就会产生表面复合现象及生成多余的废热,因此表面缺陷的存在会对微型半导体元件的性能表现产生负面影响。

发明内容

本发明提供一种微型半导体元件,其可以在降低电流载子与表面缺陷产生表面复合现象的机率的同时减少多余废热的生成,改善因表面缺陷的存在对其性能表现产生的负面影响。

本发明的一种微型半导体元件,包括半导体结构、电流局限层以及第一型电极与第二型电极。电流局限层设置于半导体结构中,其中电流局限层包括氧化区域与非氧化区域。第一型电极与第二型电极皆设置于电流局限层上。氧化区域的一部分于所述半导体结构远离所述第一型电极和所述第二型电极的一底面上的正投影位于所述第一型电极于所述底面上的正投影与所述第二型电极于所述底面上的正投影之间。

在本发明的一实施例中,上述的氧化区域的电阻值大于所述非氧化区域的电阻值。

在本发明的一实施例中,上述的半导体结构还包括第一型半导体层、第二型半导体层以及发光层。第一型半导体层设置于半导体结构上。第二型半导体层设置于第一型半导体层上。发光层设置于第一型半导体层与第二型半导体层之间。

在本发明的一实施例中,上述的电流局限层位于第二型半导体层内。

在本发明的一实施例中,第二型半导体层包括第一部分与第二部分,第一部分位于电流局限层与发光层之间,电流局限层位于第一部分与第二部分之间。

在本发明的一实施例中,上述的第一部分的掺杂浓度小于第二部分的掺杂浓度。

在本发明的一实施例中,上述的第一型电极于半导体结构上的正投影与非氧化区域于半导体结构上的正投影至少部分重叠。

在本发明的一实施例中,上述的第一型电极于半导体结构上的正投影与非氧化区域于半导体结构上的正投影完全重叠。

在本发明的一实施例中,上述的氧化区域的边缘与电流局限层的边缘切齐。

在本发明的一实施例中,上述的氧化区域的边缘与电流局限层的边缘具有距离。

在本发明的一实施例中,上述的电流局限层位于第一型半导体层内。

在本发明的一实施例中,上述的电流局限层为至少二层电流局限层,至少二层电流局限层的一者位于第一型半导体层内,至少二层电流局限层的另一者位于第二型半导体层内。

在本发明的一实施例中,上述的至少二层电流局限层的一者中的非氧化区域与所述至少二层电流局限层的另一者的非氧化区域于所述底面上的正投影至少部分重叠。

在本发明的一实施例中,上述的至少二层电流局限层的一者中的非氧化区域与所述至少二层电流局限层的另一者的非氧化区域于所述底面上的正投影完全错位。

在本发明的一实施例中,上述的在第一型电极与第二型电极的排列方向上,氧化区域与非氧化区域的交界位于第一型电极与第二型电极之间。

本发明的一种微型半导体元件,包括半导体结构、电流局限层以及第一型电极与第二型电极。电流局限层设置于半导体结构内上,其中电流局限层包括氧化区域与非氧化区域。第一型电极与第二型电极皆设置于电流局限层上。第二型电极具有朝半导体结构远离第一型电极和第二型电极的底面方向延伸的穿孔,且氧化区域环绕第一型电极、第二型电极或其组合。

基于上述,本发明的微型半导体元件中的电流局限层包括氧化区域与非氧化区域,且设计为氧化区域的至少一部分位于电极之间或氧化区域环绕电极,以通过氧化区域与非氧化区域的电阻值差异,有效地控制电流流向,使电流载子不易在电极之间进行横向扩散,进而降低电流载子通过电极之间的表面缺陷部分的机率,因此本发明的微型半导体元件可以在降低电流载子与表面缺陷产生表面复合现象的机率的同时减少多余的废热的生成,改善因表面缺陷的存在对其性能表现产生的负面影响。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

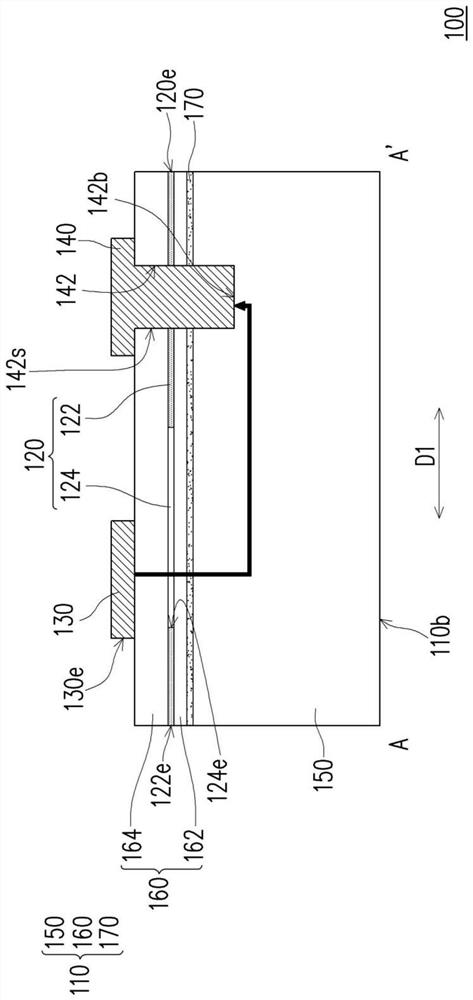

图1A示出本发明一实施例的微型半导体元件的部分剖面示意图;

图1B示出图1A的微型半导体元件的俯视示意图,其中图1A是沿图1B中的线A-A’的部分剖视图;

图1C示出本发明另一实施例的微型半导体元件的部分剖面示意图;

图1D示出本发明又一实施例的微型半导体元件的部分剖面示意图;

图2示出本发明再一实施例的微型半导体元件的部分剖面示意图;

图3示出本发明又另一实施例的微型半导体元件的部分剖面示意图;

图4A示出本发明又再一实施例的微型半导体元件的部分剖面示意图。

图4B示出本发明又再又一实施例的微型半导体元件的部分剖面示意图;

图5A示出本发明又再另一实施例的微型半导体元件的部分剖面示意图;

图5B示出图5A的微型半导体元件的俯视示意图,其中图5A是沿图5B中的线B-B’的部分剖视图。

特别说明的是,为了清楚示出,图1B、图5B采透视画法。

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

以下在实施方式中详细叙述本发明的详细特征以及优点,其内容足以使任何本领域技术人员了解本发明的技术内容并据以实施,且根据本说明书所公开的内容、权利要求及附图,任何本领域技术人员可轻易地理解本发明相关的目的及优点。以下的实施例进一步详细说明本发明的观点,但非以任何观点限制本发明的范畴。

图1A示出本发明一实施例的微型半导体元件的部分剖面示意图。图1B示出图1A的微型半导体元件的俯视示意图,其中图1A是沿图1B中的线A-A’的部分剖视图。

请参考图1A与图1B,在本实施例中,微型半导体元件100包括半导体结构110、电流局限层120以及第一型电极130与第二型电极140,其中电流局限层120设置于半导体结构110中,第一型电极130与第二型电极140皆设置于电流局限层120上。

在一些实施例中,半导体结构110例如是由适用于进行磊晶的半导体材料所形成,但本发明不限于此。

在一些实施例中,第一型电极130可以是P型电极,而第二型电极可以是N型电极,但本发明不限于此。

在本实施例中,电流局限层120例如是由可以进行选择性氧化的半导体材料所形成,以使电流局限层120可以包括用于控制电极之间的电流流向的部分氧化区域。举例而言,可以对电流局限层120进行选择性氧化,以于电流局限层120中形成电阻值不同的氧化区域122与非氧化区域124,其中氧化区域122与非氧化区域124可以用于控制第一型电极130与第二型电极140之间的电流流向。

在一些实施例中,氧化区域122的电阻值可以是大于非氧化区域124的电阻值,但本发明不限于此。

在本实施例中,微型半导体元件100中的电流局限层120可以包括氧化区域122与非氧化区域124,且可以设计为氧化区域122的一部分于半导体结构110远离第一型电极130和第二型电极130的底面110b上的正投影位于第一型电极130于半导体结构110的底面110b上的正投影与第二型电极140于半导体结构110的底面110b上的正投影之间,亦即氧化区域122的至少一部分位在电极之间,或者,设计为氧化区域122环绕第一型电极130、第二型电极140或其组合,亦即氧化区域122环绕电极,以通过氧化区域122与非氧化区域124的电阻值差异,有效地控制电流流向,使电流载子不易在电极之间进行横向扩散,进而降低电流载子通过电极之间的表面缺陷部分的机率,因此微型半导体元件100可以在降低电流载子与表面缺陷产生表面复合现象的机率的同时减少多余的废热的生成,改善因表面缺陷的存在对其性能表现产生的负面影响。

在本实施例中,第二型电极140可以具有朝半导体结构110的底面110b方向延伸的穿孔142,其中穿孔142例如是通过干刻蚀工艺所形成,因此在形成穿孔142的同时会于其侧壁上形成表面缺陷,因此设计为氧化区域122的至少一部分位于电极之间或氧化区域122环绕电极时可以使电流载子例如是由第一型电极130往下穿过电流局限层120的非氧化区域124,再由穿孔142的底部142b流至第二型电极140,电流路径可以如图1A的箭头方向所示,使电流载子不易在电极之间进行横向扩散,降低电流载子通过穿孔142侧壁上的表面缺陷部分,进而可以在降低电流载子与表面缺陷产生表面复合现象的机率的同时减少多余的废热的生成,改善因表面缺陷的存在对性能表现产生的负面影响。

在一些实施例中,氧化区域122可以同时位于第二型电极140的周围以及微型半导体元件100的边缘,因此氧化区域122可以同时环绕第一型电极130与第二型电极140且具有围绕第二型电极140的穿孔142的环形轮廓(如图1B所示),但本发明不限于此。

在一些实施例中,穿孔142可以是朝半导体结构110方向贯穿电流局限层120,穿孔142的底部142b可以位于电流局限层120与半导体结构110之间,但本发明不限于此。

在一些实施例中,氧化区域122可以是覆盖穿孔142的外侧壁142s并与外侧壁142s直接接触,但本发明不限于此。

在本实施例中,半导体结构110可以还包括第一型半导体层150、第二型半导体层160以及发光层170,其中第二型半导体层160可以设置于第一型半导体层150上,且发光层170可以设置于第一型半导体层150与第二型半导体层160之间,因此设计为氧化区域122的至少一部分位于电极之间或氧化区域122环绕电极时可以减少电流载子因与表面缺陷产生表面复合现象而造成的不必要损耗(电流载子被表面缺陷消耗而无法用于发光),以增加等效电流密度且提升发光效果,进而可以有利于微型半导体元件100的量子效率表现,但本发明不限于此。

在一些实施例中,第一型半导体层150例如是P型半导体层,而第二型半导体层160例如是N型半导体层,但本发明不限于此,可以视实际设计上的需求进行调整。

在一些实施例中,发光层170例如是多层量子井结构(Multiple Quantum Well,MQW),多重量子井结构包括交替堆叠的多层氮化铟镓(InGaN)以及多层氮化镓(GaN),通过设计发光层170中铟或镓的比例,可调整发光层170的发光波长范围,但本发明不限于此。

在一些实施例中,微型半导体元件100可以是微型发光元件,如微型发光二极管(Micro LED),其中微型发光元件的尺寸可以是小于等于50微米,但本发明不限于此。

在一些实施例中,当上述微型发光元件的电流范围在10毫安培(mA)以下时,例如是介于0.1毫安培至10毫安培之间,其可以具有更佳的发光效果,进而可以更有利于微型半导体元件100量子效率的表现,但本发明不限于此。

在一些实施例中,前述微型发光二极管可以是水平式微型发光二极管,但本发明不限于此。

应说明的是,本发明不限制微型半导体元件100的种类,举例而言,微型半导体元件100也可以是微型集成电路(micro IC)、微型激光二极管(micro LD)或微型传感器(micro sensor)等微型半导体元件。

在一些实施例中,发光层150可以设置于穿孔142的底部142b与电流局限层120之间,但本发明不限于此。

在本实施例中,电流局限层120可以位于第二型半导体层160内。举例而言,电流局限层120可以是位于第二型半导体层160内具有一定程度铝含量的膜层,以有效地对其进行选择性氧化,而形成包括氧化铝(AlO

在一些实施例中,第二型半导体层160可以是III V族半导体层,例如是氮化镓(GaN)层,而电流局限层120可以是具有一定程度铝含量的氮化铝铟(Al

在一些实施例中,第二型半导体层160可以是磷化铝镓铟(AlGaInP)层,而电流局限层120可以是具有一定程度铝含量的砷化铝镓(Al

应说明的是,本发明不限制电流局限层120中的氧化区域122中所包括的氧化物,也不限制电流局限层120的元素组成比例,只要电流局限层120包括氧化区域122与非氧化区域124皆属于本发明的保护范围。

在一些实施例中,第二型半导体层160可以包括第一部分162与第二部分164,其中第一部分162可以位于电流局限层120与发光层170之间,且电流局限层120位于第一部分162与第二部分164之间,但本发明不限于此。

在一些实施例中,第二型半导体层160例如是P型磷化铝镓铟(AlGaInP)或P型氮化铝镓铟(AlGaInN),且第一部分162与第二部分164中可以具有不同程度的铝含量,换句话说,第一部分162与第二部分164的铝含量可以不对称,但本发明不限于此。

在一些实施例中,第一部分162与第二部分164被电流局限层120分隔开,但本发明不限于此。

在一些实施例中,第一部分162的掺杂浓度可以不同于第二部分164的掺杂浓度。进一步而言,由于第二型半导体层160中的掺杂浓度的高低可能会影响电流流向,举例而言,当第一部分162的掺杂浓度过高时会增加电流载子的横向扩散能力,降低电流局限层120控制电流流向的能力,因此第一部分162的掺杂浓度可以是小于第二部分164的掺杂浓度,举例而言,可以小于约1018,以增加接触电阻,降低其影响电流流向的机率,但本发明不限于此。

在一些实施例中,第一型电极130于半导体结构110上的正投影与非氧化区域124于半导体结构110上的正投影可以是至少部分重叠。举例而言,如图1A所示,第一型电极130于底面110b上的正投影与非氧化区域124于底面110b上的正投影可以是至少部分重叠但没有完全重叠,可使电流流经下方非氧化区域124,但本发明不限于此。

在一些实施例中,氧化区域122的边缘122e可以与电流局限层120的边缘120e实质上切齐,但本发明不限于此。在一些实施例中,非氧化区域124的边缘124e可以与第一型电极130的边缘130e实质上切齐,但本发明不限于此。

在一些实施例中,在第一型电极130与第二型电极140的排列方向D1上,氧化区域122与非氧化区域124的交界位于第一型电极130与第二型电极140之间,但本发明不限于此。

在一些实施例中,氧化区域122与非氧化区域124之间可以具有大于等于一个交界(如图1A具有两个交界),因此可以是氧化区域122与非氧化区域124的任一个或多个交界位于第一型电极130与第二型电极140之间,但本发明不限于此。

在一些实施例中,氧化区域122的厚度可以与非氧化区域124的厚度实质上相同,因此电流局限层120可以是厚度均匀的膜层,但本发明不限于此。

在一些实施例中,电流局限层120的厚度可以是小于等于500埃

在一些实施例中,电流局限层120的厚度与微型半导体元件100的厚度比例可以是小于等于0.06%,当厚度比例大于0.06%将会影响微型半导体元件100效率。

在一些实施例中,氧化区域122与第一型电极130之间的距离可以大于等于10纳米(nm),距离小于10纳米可能造成第一型电极130与第一型半导体层160电性连接效率不佳,但本发明不限于此。

在一些实施例中,氧化区域122可以包括第二型电极140周围的第一横向氧化深度d1以及微型半导体元件100边缘的第二横向氧化深度d2与第三横向氧化深度d3,如图1B所示,其中第一横向氧化深度d1、第二横向氧化深度d2与第三横向氧化深度d3可以大于等于10纳米,横向氧化深度过小电流局限效果不佳,但本发明不限于此。

在一些实施例中,微型半导体元件100的中心部分C为电流密度较高的区域,如图1B框线所示,其中在中心部分C内氧化区域122的面积占总中心部分C的面积的0.1%到80%,过小电流局限效果不佳,过高正向电压会太高。在此,中心部分C可以是通过第一型电极130与第二型电极140的几何中心位置或圆心所定义出来。

在此必须说明的是,以下实施例沿用上述实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明,关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

图1C示出本发明另一实施例的微型半导体元件的部分剖面示意图。请参照图1C,相较于微型半导体元件100而言,本实施例的微型半导体元件100a的第一型电极130于半导体结构110上的正投影可以与非氧化区域124于半导体结构110上的正投影完全重叠,但本发明不限于此。

图1D示出本发明又一实施例的微型半导体元件的部分剖面示意图。请参照图1D,相较于微型半导体元件100而言,本实施例的微型半导体元件100b的氧化区域122的边缘122e与电流局限层120的边缘120e可以具有距离,换句话说,氧化区域122仅在第二型电极140的两侧,但本发明不限于此。

图2示出本发明再一实施例的微型半导体元件的部分剖面示意图。请参照图2,相较于微型半导体元件100而言,本实施例的微型半导体元件200的电流局限层220可以位于第一型半导体层150内,其中电流局限层220的氧化区域222的至少一部分位于电极之间或氧化区域222环绕电极。

此外,第一型电极130于半导体结构110上的正投影与非氧化区域224于半导体结构110上的正投影可以是至少部分重叠但没有完全重叠,但本发明不限于此。

图3示出本发明又另一实施例的微型半导体元件的部分剖面示意图。请参照图3,相较于微型半导体元件100而言,本实施例的微型半导体元件300的电流局限层可以为至少二层电流局限层,可以增加电流局限。举例而言,至少二层电流局限层可以例如是图1A所示的电流局限层120与图2所示的电流局限层220,其中电流局限层220位于第一型半导体层150内,电流局限层120位于第二型半导体层160内,但本发明不限于此。

在一些实施例中,由于当电流局限层的层数过多时会影响微型半导体元件的结构,因此电流局限层的层数可以是大于等于一层,且小于等于四层,但本发明不限于此。在此,多层电流局限层与发光层之间的排列方式可以视实际设计上的需求进行调整。

在本实施例中,电流局限层120中的非氧化区域124与电流局限层220的非氧化区域224在电流局限层120与电流局限层220的排列方向D2上可以相互对位,电流局限层120中的非氧化区域124与电流局限层220的非氧化区域224于底面110b上的正投影至少部分重叠,但本发明不限于此。

图4A示出本发明又再一实施例的微型半导体元件的部分剖面示意图。请参照图4A,相较于微型半导体元件300而言,本实施例的微型半导体元件400a的电流局限层120中的非氧化区域124与电流局限层220的非氧化区域224在电流局限层120与电流局限层220的排列方向D2上可以部分错位,亦即二者的正投影可以至少部分不重叠。较佳的,非氧化区域124靠近第一型电极130,非氧化区域224靠近第二型电极140,让电流可以往中间集中,但本发明不限于此。

图4B示出本发明又再又一实施例的微型半导体元件的部分剖面示意图。请参照图4B,相较于微型半导体元件400而言,本实施例的微型半导体元件400b的电流局限层120中的非氧化区域124与电流局限层220的非氧化区域224在电流局限层120与电流局限层220的排列方向D2上可以完全错位,亦即二者的正投影可以完全不重叠,以调配电流于特定中心位置集中密度,但本发明不限于此。

图5A示出本发明又再另一实施例的微型半导体元件的部分剖面示意图。图5B示出图5A的微型半导体元件的俯视示意图,其中图5A是沿图5B中的线B-B’的部分剖视图。请参照图5A与图5B,相较于微型半导体元件100而言,本实施例的微型半导体元件500可以是具有平台(MESA)结构的水平式微型半导体元件500,其中平台结构例如是微型半导体元件100具有高低差的区域。举例而言,微型半导体元件500的半导体结构110上可以具有凸起部分112与凹陷部分114,其中第一型电极130位于凸起部分112,第二型电极540位于凹陷部分114。

由于在制作平台结构时在第一型电极130所在的凸起部分112与第二型电极540所在的凹陷部分114之间会存在表面缺陷,因此在本实施例中,氧化区域522的一部分可以位于凸起部分112与凹陷部分114之间,以使电流载子不易在电极之间进行横向扩散,进而降低电流载子通过电极之间的表面缺陷部分的机率。

在一些实施例中,凸起部分112与凹陷部分114可以通过连接部分构成阶梯状结构,且氧化区域522与连接部分可以直接接触,但本发明不限于此。

在一些实施例中,电流局限层520中的氧化区域522与非氧化区域524可以仅位于凸起部分112,但本发明不限于此。

在一些实施例中,氧化区域522可以是仅环绕第一型电极130,如图5B所示,但本发明不限于此。

在一些实施例中,第二型电极540可以是不具有穿孔,但本发明不限于此。

在一些实施例中,微型半导体元件500在中心部分(如图5B的粗框线部分)内氧化区域522的面积占总中心部分的面积的0.1%至80%,过小电流局限效果不佳,过高正向电压会太高。在此,中心部分C可以是通过平台结构上的第一型电极130的几何中心位置或圆心与平台结构的凸起部分112的边缘112e所定义出来。

应说明的是,本发明的氧化区域与非氧化区域不限定于上述实施例中的配置方式与对应比例,只要氧化区域的至少一部分位于电极之间或氧化区域环绕电极皆属于本发明的保护范围。

综上所述,本发明的微型半导体元件中的电流局限层包括氧化区域与非氧化区域,且设计为氧化区域的至少一部分位于电极之间或氧化区域环绕电极,以通过氧化区域与非氧化区域的电阻值差异,有效地控制电流流向,使电流载子不易在电极之间进行横向扩散,进而降低电流载子通过电极之间的表面缺陷部分的机率,因此本发明的微型半导体元件可以在降低电流载子与表面缺陷产生表面复合现象的机率的同时减少多余的废热的生成,改善因表面缺陷的存在对其性能表现产生的负面影响。此外,由于可以减少电流载子因与表面缺陷产生表面复合现象而造成的不必要损耗(电流载子被表面缺陷消耗而无法用于发光),以增加等效电流密度且提升发光效果,进而可以有利于本发明的微型半导体元件的量子效率表现。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 微型半导体芯片、微型半导体元件结构、以及显示元件

- 微型半导体元件结构