集成芯片、多重晶体管装置及其制造方法

文献发布时间:2023-06-19 12:19:35

技术领域

本公开涉及一种多重晶体管装置(multi-transistor device),特别涉及一种利用虚拟晶体管以防止漏电的多重晶体管装置。

背景技术

半导体产业借由,举例来说,降低最小特征尺寸及/或设置电子装置使其彼此间更加靠近,来持续地改进各种电子组件(例如:晶体管、二极管、电阻器、电容器等)的集成密度,这允许更多的组件被整合在给定的面积中。举例来说,多重晶体管装置可包括多于一个的鳍式场效晶体管(fin field effect transistor,FinFET),其中第一栅极电极与第二栅极电极可被设置在相同的连续鳍片上,以降低装置面积及/或增加制造效率。

发明内容

本公开实施例提供一种多重晶体管装置的制造方法。上述制造方法包括:接收用于电路设计图的初始布局设计,初始布局设计包括设置于连续鳍片上的第一栅极电极、第二栅极电极、以及虚拟栅极电极,其中虚拟栅极电极被设置于第一栅极电极与第二栅极电极之间,第一源极/漏极区域被设置于第一栅极电极与虚拟栅极电极之间,且第二源极/漏极区域被设置于第二栅极电极与虚拟栅极电极之间,其中第一栅极电极对应具有第一临界电压的第一晶体管,第二栅极电极对应具有第二临界电压的第二晶体管,而虚拟栅极电极对应具有虚拟临界电压且分隔第一晶体管与第二晶体管的虚拟晶体管;判断第一源极/漏极区域或第二源极/漏极区域中的至少一者是否对应电路设计图中的一漏极;以及当第一源极/漏极区域或第二源极/漏极区域中的至少一者对应电路设计图中的上述漏极时,修改初始布局设计以将虚拟晶体管的虚拟临界电压增加为修改后虚拟临界电压,借此提供修改后布局设计,其中虚拟晶体管所具有的修改后虚拟临界电压高于第一临界电压及第二临界电压中的每一者。

本公开实施例提供一种多重晶体管装置。上述多重晶体管装置包括:一连续鳍片,自基板突出,连续鳍片在第一方向上延伸;第一晶体管装置,具有第一临界电压且包括:第一栅极电极,在基本上垂直于第一方向的第二方向上延伸,其中第一栅极电极直接覆盖连续鳍片的第一通道区域,以及包括连续鳍片的第一源极/漏极区域及第二源极/漏极区域,其中第一栅极电极将第一源极/漏极区域与第二源极/漏极区域分隔;第二晶体管装置,具有不同于第一临界电压的第二临界电压,第二晶体管装置包括:第二栅极电极,在第二方向上延伸且直接覆盖连续鳍片的第二通道区域,以及包括连续鳍片的第三源极/漏极区域及第四源极/漏极区域,其中第二栅极电极将第三源极/漏极区域与第四源极/漏极区域分隔;以及虚拟晶体管装置,具有虚拟栅极临界电压且包括:虚拟栅极电极,在第二方向上延伸且直接覆盖连续鳍片的虚拟通道区域,其中虚拟栅极电极直接位于第二源极/漏极区域与第三源极/漏极区域之间,且虚拟栅极临界电压大于第一临界电压与第二临界电压。

本公开实施例提供一种集成芯片。上述集成芯片包括:第一连续鳍片,设置于基板上且在第一方向上延伸;第二连续鳍片,设置于基板上,在第一方向上延伸,且在基本上垂直于第一方向的第二方向上与第一连续鳍片间隔;第一栅极电极,在第二方向上延伸,且被设置于第一连续鳍片的第一通道区域上以定义第一晶体管装置,并被设置于第二连续鳍片的第二通道区域上以定义第二晶体管装置;第二栅极电极,在第二方向上延伸,且被设置于第一连续鳍片的第三通道区域上以定义第三晶体管装置,并被设置于第二连续鳍片的第四通道区域上以定义第四晶体管装置;第一虚拟栅极电极,设置于第一栅极电极与第二栅极电极之间,且被设置于第一连续鳍片的第一虚拟通道区域上以定义第一虚拟晶体管装置,其中第一虚拟晶体管装置与第一晶体管装置共享一第一源极/漏极区域,且第一虚拟晶体管装置与第三晶体管装置共享第二源极/漏极区域;以及第二虚拟栅极电极,设置于第一栅极电极与第二栅极电极之间,且被设置于第二连续鳍片的第二虚拟通道区域上以定义第二虚拟晶体管装置,其中第二虚拟栅极电极在第二方向上与第一虚拟栅极电极间隔,其中第二虚拟晶体管装置与第二晶体管装置共享第三源极/漏极区域,且第二虚拟晶体管装置与第四晶体管装置共享第四源极/漏极区域;其中第一晶体管装置具有不同于第三晶体管装置的临界电压,且第一虚拟晶体管装置具有高于第一晶体管装置及第三晶体管装置的临界电压。

附图说明

本公开的态样自后续实施方式及附图可更佳理解。须强调的是,依据产业的标准作法,各种特征并未按比例绘制。事实上,各种特征的尺寸可能任意增加或减少以清楚论述。

图1A至图1E显示集成芯片的一些实施例的各种图示,该集成芯片包括第一虚拟栅极电极,第一虚拟栅极电极设置于第一栅极电极与第二栅极电极之间、设置于连续鳍片之上、以及对应的第一虚拟晶体管装置,该虚拟晶体管装置具有高于周遭的晶体管装置的临界电压。

图2A至图2B显示电路示意图的一些实施例的俯视图,该电路示意图对应第一连续鳍片及第二连续鳍片上的第一栅极电极、第二栅极电极、第一虚拟栅极电极、以及第二虚拟栅极电极。

图3A至图3C显示集成芯片的一些实施例的各种图示,该集成芯片包括第一连续鳍片及第二连续鳍片,其中第二连续鳍片在第二虚拟栅极电极下方,具有高于第一栅极电极和第二栅极电极下方的掺杂浓度。

图4显示集成芯片的一些实施例的俯视图,该集成芯片包括耦接至第一源极端子的第一对源极/漏极区域之间的第一虚拟栅极电极,以及包括耦接至第二源极端子的第二对源极/漏极区域之间的第二虚拟栅极电极。

图5显示集成芯片的一些实施例的俯视图,该集成芯片包括耦接至至少一个第一漏极端子的第一源极/漏极区域的第一者与第二者之间的第一虚拟栅极电极,以及耦接至至少一个第二漏极端子的第二源极/漏极区域的第一者与第二者之间的第二虚拟栅极电极。

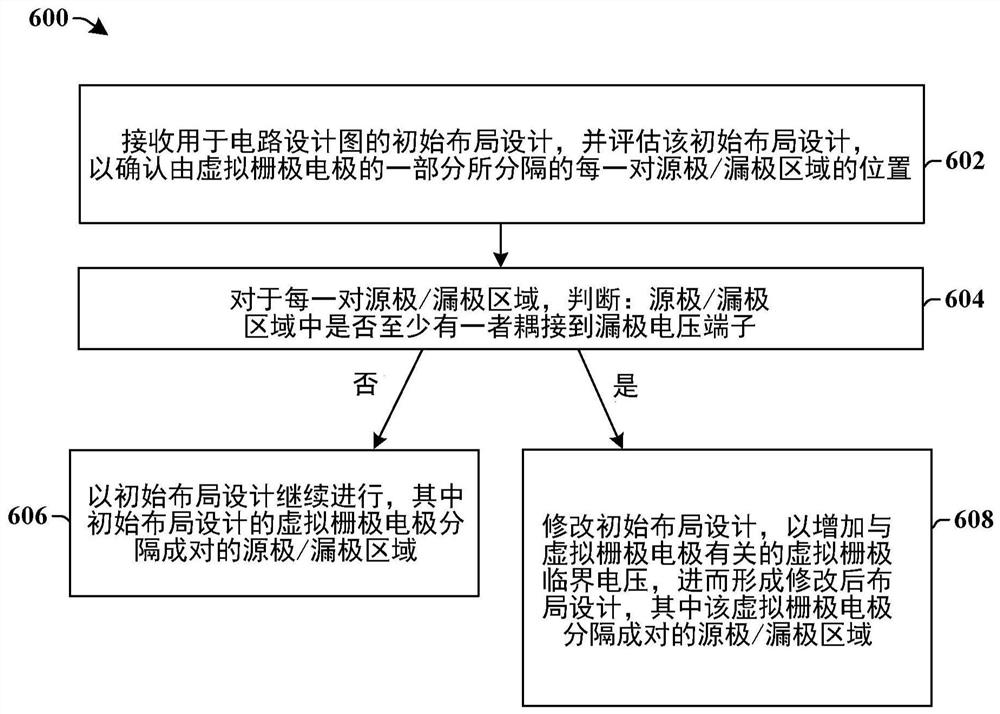

图6显示一方法的一些实施例的流程图,该方法判断用于包括虚拟栅极电极的连续鳍片装置的布局设计是否需要修改。

图7A至图7D显示对应图6的方法的集成芯片的一些实施例的各种图示。

图8、图9A至图9C及图10显示一方法的一些实施例,该方法借由改变第二虚拟栅极晶体管装置的第二虚拟栅极电极的材料,来改变第二连续鳍片上的第二虚拟栅极晶体管装置的临界电压。

图11显示对应图8、图9A至图9C及图10的方法的一些实施例的流程图。

图12、图13A至图13C、图14A至图14B及图15显示一方法的一些实施例,该方法借由改变直接覆盖第二虚拟栅极晶体管装置的第二虚拟栅极电极的第二连续鳍片的掺杂浓度,来改变第二连续鳍片上的第二虚拟栅极晶体管装置的临界电压。

图16显示对应图12、图13A至图13C、图14A至图14B及图10的方法的一些实施例的流程图。

图17显示简化的布局图示的一些实施例,该简化的布局图示包括具有不同临界电压的功能性单元单位(cell unit)。

其中,附图标记说明如下:

100A:透视图

102:基板

104:隔离结构

114:第一源极/漏极区域

116:第一连续鳍片

118:第二源极/漏极区域

120:第二连续鳍片

122:第一栅极电极

123a:第一晶体管装置

123b:第二晶体管装置

123c:第三晶体管装置

123d:第四晶体管装置

124:第二栅极电极

127:第一虚拟栅极电极

128:第二虚拟栅极电极

130:第一栅极介电层

132:第二栅极介电层

134:第二虚拟栅极介电层

150:第一虚拟晶体管装置

152:第二虚拟晶体管装置

100B:俯视图

106:低临界电压n型装置区域

108:低临界电压p型装置区域

110:超低临界电压n型装置区域

112:超低临界电压p型装置区域

114a:第一者

114b:第二者

118a:第一者

118b:第二者

140:标准临界电压p型装置区域

AA’,BB’,CC’:线段

100C:截面图

128t:最顶部表面

t

t

t

170:第二通道区域

172:第四通道区域

174:第二虚拟通道区域

100D:截面图

102d:掺杂部分

102u:未掺杂部分

136:第一虚拟栅极介电层

176:第一虚拟通道区域

182:点线

t

100E:截面图

192:点线

200A:俯视图

V

V

V

V

V

V

V

V

200B:俯视图

212:第一范例性路径

214:第二范例性路径

216:第三范例性路径

218:第四范例性路径

220:范例性漏电路径

300A:俯视图

302:第一高掺杂浓度区域

300B:截面图

300C:截面图

400:俯视图

500:俯视图

540:标准临界电压n型装置区域

600:方法

602~608:操作

700A:示意图

110a:第一反相器

110b:第二反相器

110c:第三反相器

110d:第四反相器

702:第一功能性单元单位

704:第二功能性单元单位

in1:第一输入

in2:第二输入

in3:第三输入

in4:第四输入

out1:第一输出

out2:第二输出

out3:第三输出

out4:第四输出

700B:示意图

M1:第一p型晶体管

M2:第二p型晶体管

M3:第一n型晶体管

M4:第二n型晶体管

D1~D4:虚拟晶体管

s1:第一源极区域

s2:第二源极区域

s3:第三源极区域

s4:第四源极区域

d1:第一漏极区域

d2:第二漏极区域

d3:第三漏极区域

d4:第四漏极区域

700C:初始布局设计

706~712:虚拟栅极电极

P1:第一对源极/漏极区域

P2:第二对源极/漏极区域

P3:第三对源极/漏极区域

P4:第四对源极/漏极区域

700D:修改后布局设计

D1_mod:第一修改后虚拟晶体管

D2_mod:第二修改后虚拟晶体管

800:透视图

900A~900C:透视图

1000:透视图

1100:方法

1102~1110:操作

1200:透视图

1300A:透视图

1302:第一遮罩结构

1304:第一部分

1300B:透视图

1306:掺杂制程

1308:第二高掺杂浓度区域

1300C:透视图

1400A,1400B:透视图

1500:透视图

1600:方法

1602~1610:操作

1700:布局图示

1710:功能性单元单位

1710a,1710b:第一功能性单元

1720:功能性单元单位

1720a,1720b:功能性单元

1730~1760:功能性单元单位

SVT:标准电压临界值

LVT:低电压临界值

uLVT:超低电临界值

具体实施方式

以下的公开提供许多不同实施例或范例,用以实施本公开的不同特征。本公开的各部件及排列方式,其特定范例叙述于下以简化说明。理所当然的,这些范例并非用以限制本公开。举例来说,若叙述中有着第一特征成形于第二特征之上或上方,其可能包含第一特征与第二特征以直接接触成形的实施例,亦可能包含有附加特征形成于第一特征与第二特征之间,而使第一特征与第二特征间并非直接接触的实施例。此外,本公开可在多种范例中重复参考数字及/或字母。该重复的目的是为简化及清晰易懂,且本身并不规定所讨论的多种实施例及/或配置间的关系。

进一步来说,本公开可能会使用空间相对术语,例如“在…下方”、“下方”、“低于”、“在…上方”、“高于”及类似词汇,以便于叙述图示中一个元件或特征与其他元件或特征间的关系。除了图示所描绘的方位外,空间相对术语亦欲涵盖使用中或操作中的装置其不同方位。设备可能会被转向不同方位(旋转90度或其他方位),而此处所使用的空间相对术语则可相应地进行解读。

图17以简化的布局图示1700的方式显示半导体装置,简化的布局图示1700包括被分隔为列(row)的多个功能性单元单位。功能性单元单位被配置以执行预定的电路功能,包括布林(Boolean)逻辑功能,例如反相器(inverter)。在一些实施例中,功能性单元单位包括非门(NOT gate)、与门(AND gate)、与非门(NAND gate)、或门(OR gate)、或非门(NORgate)、异或门(XOR gate)、异或非门(XNOR gate),其他逻辑门、或其组合。因此,这种功能性单元单位可被称为标准单元。在其他实施例中,功能性单元单位包括逻辑门与被动/主动元件(例如:电阻器、电容器、电感器、晶体管、二极管等)。

图17的范例包括数个功能性单元单位:功能性单元单位1710、1720、1730、1740、1750及1760。功能性单元单位1710、1720、1730、1740中的每一者,包括具有不同临界电压(threshold voltage)的一对功能性单元,而功能性单元单位1750、1760则包括具有相同临界电压的一对功能性单元。举例来说,功能性单元单位1710包括具有不同临界电压的第一功能性单元1710a与第二功能性单元1710b。进一步地,在一些实施例中,功能性单元单位1710可包括呈现具有标准电压临界值(standard voltage threshold,SVT)的第一反相器形式的第一功能性单元1710a,以及包括呈现具有低电压临界值(low voltage threshold,LVT)的第二反相器形式的第二功能性单元1710b。更进一步地,另一个功能性单元单位1720可包括超低电临界值(ultra-low voltage threshold,uLVT)的功能性单元1720a,以及SVT的功能性单元1720b。LVT的功能性单元所具有的临界电压小于SVT的功能性单元的临界电压,但高于uLVT的功能性单元的临界电压。在其他实施例中,功能性单元单位可仅包括单一功能性单元,或是两个以上的功能性单元,其中此等功能性单元可具有彼此相同的临界电压,或是具有彼此不同的临界电压。

为了产生简化的布局图示1700,自动设置与选路(auto-place and route)机台(典型的为在包括微处理器及半导体存储器的电脑系统上执行的自动设置与选路软件)始于半导体装置的示意性层级表述(schematic level representation)或半导体装置的功能性表述(functional representation)(例如:以诸如Verilog HDL的硬件描述语言(hardware description language,HDL)所编写的编码(code))。接着,自动设置与选路机台识别可耦接在一起以达成为半导体装置具体指定的功能的功能性单元单位。识别出这些功能性单元单位后,自动设置与选路机台将对应功能性单元单位的布局铺设(tile)为芯片布局,如图17所示,并使用芯片布局中的导线将功能性单元单位耦接在一起,以确保所计画的芯片布局符合将要制造芯片的制造设施所要求的时序规定(timing specification)及设计规则(design rule)。

在本公开中,自动设置与选路机台检查初始芯片布局,以判断相邻的功能性单元是否具有彼此直接相邻的源极与漏极区域,仅有虚拟栅极电极将那些源极与漏极区域分隔。因为这些直接相邻的源极与漏极区域可能会经历不同的电压电位(voltagepotential),所以虚拟栅极电极是这些源极与漏极区域之间的漏电的潜在来源。因此,当自动设置与选路机台在初始芯片布局中识别出此配置时,自动设置与选路机台修改布局以增加与虚拟栅极电极相关的临界电压(同时保持芯片布局中其他晶体管的临界电压不变),进而限制虚拟栅极电极漏电的风险。因为自动设置与选路机台修改了布局以限制半导体装置中的漏电,同时还为芯片布局维持了较小的占用面积,因此本公开提供了优于其他方法的多个优点。举例来说,先前的方法可能已在布局中插入了“填充”单元以减少漏电,然而,这些“填充”单元却增加了整体的芯片面积,这与理想有段差距。通过在不增加芯片布局面积的情况下改变一些虚拟栅极晶体管的临界电压,本公开在降低漏电的同时,使芯片的占用面积维持在较小的状态,从许多角度来看这都是人们所期望的。

图1A是根据一些实施例所示,包含多个晶体管(例如:FinFET)装置区域的集成芯片的透视图100A。集成芯片包括第一连续鳍片116以及第二连续鳍片120,自基板102突出并穿过隔离结构104。第一连续鳍片116以及第二连续鳍120可在第一方向上延伸,并且基本上彼此平行。在一些实施例中,第一连续鳍片116可包括具有与第一连续鳍片116不同的掺杂类型的第一源极/漏极区域114,而第二连续鳍片120可包括具有与第二连续鳍片120不同的掺杂类型的第二源极/漏极区域118。

第一栅极电极122可在第二方向上于第一连续鳍116及第二连续鳍120上延伸,其中第二方向基本上垂直于第一方向。第一栅极电极122可直接覆盖第一连续鳍片116上的第一通道区域,并在第一连续鳍片116上定义第一晶体管装置123a。在一些实施例中,第一栅极电极122亦可直接覆盖第二连续鳍片120上的第二通道区域(例如:图1C的第二通道区域170),并在第二连续鳍片120上定义第二晶体管装置123b。在一些实施例中,第一栅极介电层130被设置于第一栅极电极122与隔离结构104、第一连续鳍片116还有第二连续鳍片120之间。

第一栅极电极122、第一栅极介电层130及/或第一连续鳍片116,包括对应用于第一晶体管装置123a的第一临界电压的第一结构(例如:厚度、材料、掺杂浓度等),而第一栅极电极122、第一栅极介电层130及/或第二连续鳍片120,包括对应用于第二晶体管装置123b的第二临界电压的第二结构(例如:厚度、材料、掺杂浓度等)。举例来说,在一些实施例中,第一晶体管装置123a为n型装置,而第二晶体管装置123b为p型装置。在此等实施例中,第一临界电压可为正的,而第二临界电压则可为负的。

第二栅极电极124可在第一方向上与第一栅极电极122间隔,且可在第二方向上于第一连续鳍片116与第二连续鳍120上延伸。第二栅极电极124可直接覆盖第一连续鳍片116上的第三通道区域,并在第一连续鳍片116上定义第三晶体管装置123c。在一些实施例中,第二栅极电极124亦可直接覆盖第二连续鳍片120上的第四通道区域(例如:图1C的第四通道区域172),并在第二连续鳍片120上定义第二晶体管装置123d。在一些实施例中,第二栅极介电层132被设置于第二栅极电极124与隔离结构104、第一连续鳍片116还有第二连续鳍片120之间。

第二栅极电极124、第二栅极介电层132及/或第一连续鳍片116,可包括对应用于第三晶体管装置123c的第三临界电压的第三结构(例如:厚度、材料、掺杂浓度等),而第二栅极电极124、第二栅极介电层132及/或第二连续鳍片120,可包括对应用于第四晶体管装置123d的第四临界电压的第四结构(例如:厚度、材料、掺杂浓度等)。在一些实施例中,第三晶体管装置123c为n型装置,而第四晶体管装置123d为p型装置。在此等实施例中,第三临界电压可为正的,而第四临界电压则可为负的。

在一些实施例中,第一结构不同于第三结构,且因此第一晶体管装置123a的第一临界电压不同于第三晶体管装置123c的第三临界电压。在一些实施例中,第二结构不同于第四结构,且因此第二晶体管装置123b的第二临界电压不同于第四晶体管装置123d的第四临界电压。

第一虚拟栅极电极127可被设置于第一连续鳍片116上的第一虚拟通道区域(例如:图1D的第一虚拟通道区域176)上,并分隔第一晶体管装置123a与第三晶体管装置123c。第一虚拟栅极介电层(例如:图1D的第一虚拟栅极介电层136)可被设置于第一虚拟栅极电极127与第一虚拟通道区之间。第一虚拟栅极电极127并未连续延伸且并未覆盖第二连续鳍片120。第一虚拟栅极电极127可被配置为总是“关闭(turn off)”第一虚拟通道区域(例如:防止电流流通穿过),以防止第一连续鳍片116上的第一晶体管装置123a与第三晶体管装置123c之间的漏电。举例来说,若第一连续鳍片116为p型,则施加于第一虚拟栅极电极127的负电压或接地电压将“关闭”(例如:防止电流流通穿过)第一连续鳍片116的第一虚拟通道区域。

在一些实施例中,第一虚拟栅极电极127、第一虚拟栅极介电层、以及第一虚拟通道区域,可具有与第一栅极电极122、第一栅极介电层130、以及第一通道区域相同的结构,或者是可具有与第二栅极电极124、第二栅极介电层132、以及第三通道区域相同的结构。举例来说,在图1A所示的透视图100A中,第一虚拟栅极电极127、第一虚拟栅极介电层、以及第一虚拟通道区域可对应第一虚拟晶体管装置150,其中第一虚拟晶体管装置150具有等于第三晶体管装置123c的第三临界电压的第一虚拟栅极临界电压。在此等实施例中,第一虚拟栅极电极127、第一虚拟栅极介电层、以及第一虚拟通道区域,可具有与第二栅极电极124、第二栅极介电层132、以及第三通道区域相同的结构(例如:厚度、材料、掺杂浓度等)。

第二虚拟栅极电极128可被设置于第二连续鳍片120上的第二虚拟通道区域(例如:图1C的第二虚拟通道区域174)上,并分隔第二晶体管装置123b与第四晶体管装置123d。第二虚拟栅极介电层134可被设置于第二虚拟栅极电极128与第二虚拟通道区之间。第二虚拟栅极电极128可与第一虚拟栅极电极127分离。第二虚拟栅极电极128可被配置为总是“关闭(turn off)”第二虚拟通道区域(例如:防止电流流通穿过),以防止第二连续鳍片120上的第二晶体管装置123b与第四晶体管装置123d之间的漏电。举例来说,若第二连续鳍片120为n型,则施加于第二虚拟栅极电极128的正电压将“关闭”(例如:防止电流流通穿过)第二连续鳍片120的第二虚拟通道区域。

在一些实施例中,第二连续鳍片120的第二虚拟栅极电极128、第二虚拟栅极介电层134、以及第二虚拟通道区域,可对应具有第二虚拟栅极临界电压的第二虚拟晶体管装置,其中第二虚拟栅极临界电压大于第二临界电压及第四临界电压,以确保第二晶体管装置123b与第四晶体管装置123d之间的漏电经由第二虚拟通道而被防止。换句话说,在一些实施例中,比起第二通道区域及第四通道区域,第二连续鳍片120的第二虚拟通道区域可能更难以“导通”(例如:允许电流流通穿过)。在此等实施例中,第二虚拟栅极电极128可具有与第一栅极电极122及第二栅极电极124不同的结构、第二虚拟栅极介电层134可具有与第一栅极介电层130及第二栅极介电层132不同的结构、及/或第二虚拟通道区域可具有与第二通道区域及第四通道区域不同的结构。举例来说,在图1A的透视图100A中,第二虚拟栅极介电层134可厚于第一栅极介电层130/第二栅极介电层132。

因此,在集成芯片包含多重装置区域的实施例中,为了确保具有第二临界电压的第二晶体管装置123b与具有第四临界电压(不同于第二临界电压)的第四晶体管装置123d之间的漏电被防止,被设置于第二晶体管装置123b与第四晶体管装置123d之间的第二虚拟栅极电极128及第二虚拟晶体管装置152,可被设计为所具有的临界电压高于第二临界电压及第四临界电压。借由防止具有不同临界电压的装置之间的漏电,得以降低功率损失(power-loss)并提高装置的可靠性。

图1B显示对应图1A的透视图100A的集成芯片的一些实施例的俯视图100B。

如俯视图100B所示,在一些实施例中,第一虚拟晶体管装置150与第一晶体管装置123a共享第一源极/漏极区域114的第一者114a,且第一虚拟晶体管装置150与第三晶体管装置123c共享第一源极/漏极区域114的第二者114b。第一虚拟晶体管装置150包括第一虚拟栅极电极127,被配置以防止电流在第一源极/漏极区域114的第一者114a与第二者114b之间流动,进而维持第一晶体管装置123a与第三晶体管装置123c之间的隔离,尽管第一晶体管装置123a与第三晶体管装置123c共用相同的第一连续鳍片116。

此外,第二虚拟晶体管装置152与第二晶体管装置123b共享第二源极/漏极区域118的第一者118a,且第二虚拟晶体管装置152与第四晶体管装置123d共享第二源极/漏极区域118的第二者118b。第二虚拟晶体管装置152包括第二虚拟栅极电极128,被配置以防止电流在第二源极/漏极区域118的第一者118a与第二者118b之间流动,进而维持第二晶体管装置123b与第四晶体管装置123d之间的隔离,尽管第二晶体管装置123b与第四晶体管装置123d共用相同的第二连续鳍片120。

在一些实施例中,举例来说,第一临界电压的绝对值(absolute value)大于第三临界电压的绝对值,且第二临界电压的绝对值大于第四临界电压的绝对值。在一些实施例中,第一连续鳍片116为p型,第一源极/漏极区域114为n型,第二连续鳍片120为n型,而第二源极/漏极区域118为p型。在此等实施例中,集成芯片的低临界电压n型装置区域106可包括第一晶体管装置123a;集成芯片的低临界电压p型装置区域108可包括第二晶体管装置123b;集成芯片的超低临界电压n型装置区域110可包括第三晶体管装置123c;以及超低临界电压p型装置区域112可包括第四晶体管装置123d。

在一些实施例中,第一虚拟晶体管装置150的第一虚拟临界电压的绝对值,可约等于第三晶体管装置123c的第三临界电压的绝对值,也因此,集成芯片的超低临界电压n型装置区域110亦可包括第一虚拟晶体管装置150。低临界电压n型装置区域106与超低临界电压n型装置区域110被设置在相同的第一连续鳍片116上。在一些实施例中,第二虚拟晶体管装置152的第二虚拟临界电压的绝对值,可大于第二晶体管装置123b的第二临界电压与第四晶体管装置123d的第四临界电压两者的绝对值。举例来说,第四临界电压的绝对值可处于约0.05伏特与约0.1伏特之间的范围内;第二临界电压的绝对值可处于约0.1伏特至约0.15伏特之间的范围内;而第二虚拟临界电压的绝对值可处于约0.25伏特至约0.3伏特之间的范围内。

在此等实施例中,集成芯片的标准临界电压p型装置区域140可被设置在低临界电压p型装置区域108与超低临界电压p型装置区域112之间,且标准临界电压p型装置区域140可包括第二虚拟晶体管装置152。低临界电压p型装置区域108、超低临界电压p型装置区域112、以及标准临界电压p型装置区域140被设置于相同的第二连续鳍片120上。

图1C显示对应图1B的俯视图100B的线段AA’的集成芯片的一些实施例的截面图100C。

在一些实施例中,第二连续鳍片120包括第一栅极电极122下方的第二通道区域170、第二栅极电极124下方的第四通道区域172、以及第二虚拟栅极电极128下方的第二虚拟通道区域174。第二源极/漏极区域118可被设置于第二通道区域170、第四通道区域172与第二虚拟通道区域174之间。因此,在一些实施例中,第二源极/漏极区域118的第一者118a,被直接设置于第二连续鳍片120的第二通道区域170与第二虚拟通道区域174之间,而第二源极/漏极区域118的第二者118b,被直接设置于第二虚拟通道区域174与第四通道区域172之间。在一些实施例中,第二通道区域170及第四通道区域172具有相同的掺杂浓度。在一些实施例中,第二虚拟通道区域174亦具有与第二通道区域170及第四通道区域172相同的掺杂浓度。

在一些实施例中,第一栅极介电层130可具有第一厚度t

在一些实施例中,第二虚拟栅极电极128及/或第二虚拟栅极介电层134包括与第一栅极电极122及/或第一栅极介电层130不同的结构(例如:材料、厚度、掺杂浓度等),且包括与第二栅极电极124及/或第二栅极介电层132不同的结构。在此等实施例中,举例来说,第二虚拟栅极介电层134可具有第三厚度t

将能理解的是,在其他实施例中,标准临界电压p型装置区域140的第二虚拟临界电压亦可借由下列方式调整:对第二虚拟栅极电极128使用不同的材料、对第二虚拟栅极介电层134使用不同的材料、在第二虚拟栅极电极128与第二虚拟栅极介电层134之间包括功函数(work function)层、调整第二虚拟栅极电极128及/或第二虚拟通道区域174的掺杂浓度、及/或其组合。

因此,尽管低临界电压p型装置区域108、超低临界电压p型装置区域112、以及标准临界电压p型装置区域140被设置于相同的第二连续鳍片120上,但第二虚拟栅极电极128可被配置为总是“关闭”(例如:防止电流流通穿过)第二虚拟通道区域174,以防止低临界电压p型装置区域108与超低临界电压p型装置区域112之间的漏电。

图1D显示对应图1B的俯视图100B的线段BB’的集成芯片的一些实施例的截面图100D。

截面图100D包括与第二虚拟栅极电极128间隔且被设置于基板102上的第一虚拟栅极电极127。第一虚拟栅极电极127覆盖第一连续鳍片116的第一虚拟通道区域176。因此,第二虚拟栅极电极128与第一虚拟栅极电极127电性隔离。在一些实施例中,基板具有在未掺杂部分102u之间的掺杂部分102d。第一连续鳍片116及第二连续鳍片120可各自具有不同的掺杂类型,并自基板102的掺杂部分102d连续地突出。因此,第一连续鳍片116及第二连续鳍片120可包括与基板102相同的材料(例如:硅)。

在一些实施例中,第二虚拟栅极介电层134可被设置于第二虚拟栅极电极128之下,且具有第三厚度t

图1E显示对应图1B的俯视图100B的线段CC’的集成芯片的一些实施例的截面图100E。

在一些实施例中,第一源极/漏极区域114以及第二源极/漏极区域118在截面图100E中可呈现钻石状的形状。呈现钻石状的形状的原因,可以是因为第一源极/漏极区域114以及第二源极/漏极区域118分别在第一连续鳍片116及第二连续鳍片120上外延生长(epitaxial grow)。在其他实施例中,第一源极/漏极区域114以及第二源极/漏极区域118可呈现更加梯形的形状,分别类似于第一连续鳍片116及第二连续鳍片120,如点线192所示。第一源极/漏极区域114以及第二源极/漏极区域118可被设置于隔离结构104之上。在一些实施例中,第一源极/漏极区域114具有与第一连续鳍片116相反的掺杂类型,且第二源极/漏极区域118具有与第二连续鳍片120相反的掺杂类型。

图2A显示包含多重晶体管(例如:FinFET)装置区域的集成芯片的一些实施例的俯视图200A,以及对应一些多重晶体管装置区域电路示意图。

在一些实施例中,低临界电压n型装置区域106以及低临界电压p型装置区域108可包括多个第一栅极电极122。在一些实施例中,第一栅极电极122的每一者可被耦接到个别的栅极端子(terminal),而在其他实施例中,多个第一栅极电极122可被耦接到相同的栅极端子并共享该栅极端子。相似地,在一些实施例中,超低临界电压n型装置区域110以及超低临界电压p型装置区域112可包括多个第二栅极电极124。在一些实施例中,第二栅极电极124的每一者可被耦接到个别的栅极端子,而在其他实施例中,多个第二栅极电极124可被耦接到相同的栅极端子并共享该栅极端子。

在一些实施例中,第一栅极电极122耦接到第一栅极端子V

第一源极/漏极区域114及第二源极/漏极区域118可支配第一虚拟栅极电极127及第二虚拟栅极电极128的结构,及/或第一虚拟栅极电极127及第二虚拟栅极电极128下方的薄层。举例来说,在图2A的俯视图200A中,第一源极/漏极区域114的第一者114a耦接至第一源极端子V

然而,因为第二源极/漏极区域118的第二者118b耦接至第二漏极端子V

图2B显示对应图2A的俯视图200A的一些实施例的俯视图200B,以显示当电压被施加到第一栅极电极122、第一虚拟栅极电极127、第二虚拟栅极电极128、及/或第二栅极电极124时,范例性的流动的电荷载子路径。

在一些实施例中,第一晶体管装置123a及第三晶体管装置123c为n型装置,而第二晶体管装置123b及第四晶体管装置123d为p型装置。在此等实施例中,第一晶体管装置123a与第二晶体管装置123b形成由第一栅极电极122控制的第一反相器,而第三晶体管装置123c与第四晶体管装置123d形成由第二栅极电极124控制的第二反相器。举例来说,当大于第一晶体管装置123a的第一临界电压的正电压,被施加到第一栅极电极122的第一栅极端子V

进一步地,举例来说,当比第二晶体管装置123b的第二临界电压还负的负电压,被施加到第一栅极电极122的第一栅极端子V

进一步地,举例来说,当大于第三晶体管装置123c的第三临界电压的正电压,被施加到第二栅极电极124的第二栅极端子V

进一步地,举例来说,当比第四晶体管装置123d的第四临界电压还负的负电压,被施加到第二栅极电极124的第二栅极端子V

图3A显示了具有标准临界电压p型装置区域140的集成芯片的一些其他实施例的俯视图300A,其中标准临界电压p型装置区域140被设置于低临界电压p型装置区域108与超低临界电压p型装置区域112之间,且具有高于低临界电压p型装置区域108以及超低临界电压p型装置区域112的临界电压。

在一些实施例中,位于第二虚拟栅极电极128下方的第二连续鳍片120的第二虚拟通道区域,是第二连续鳍片120的第一高掺杂浓度区域302的一部分,且因此,第二虚拟通道区域所具有的掺杂浓度,高于分别位于第一栅极电极122及第二栅极电极124下方的第二连续鳍片120的第二通道区域及第四通道区域。因此,标准临界电压p型装置区域可具有高于低临界电压p型装置区域108以及超低临界电压p型装置区域112的临界电压,进而增加了用于将第二虚拟通道区域“导通”的第二虚拟栅极临界电压。

第3B图显示对应图3A的俯视图300A的线段AA’的集成芯片的一些实施例的截面图300B。

在一些实施例中,第二连续鳍片120的第一高掺杂浓度区域302包括第二虚拟通道区域174,其中第二连续鳍片120的第一高掺杂浓度区域302具有比第二连续鳍片120的其他区域更高的掺杂浓度。在一些实施例中,第一高掺杂浓度区域302延伸到基板102的底部表面,而在其他实施例中,第一高掺杂浓度区域302并未延伸到基板102中。因此,在一些实施例中,第二虚拟通道区域174具有高于第二通道区域170及第四通道区域172的掺杂浓度。举例来说,在一些实施例中,第二连续鳍片120具有n型掺杂浓度,而第二源极/漏极区域118具有p型掺杂浓度。在此等实施例中,第二虚拟通道区域174具有比第二通道区域170及第四通道区域172更高浓度的n型掺杂物。与第二虚拟通道区域174有关的第一高掺杂浓度区域302,可使标准临界电压p型装置区域140具有高于低临界电压p型装置区域108以及超低临界电压p型装置区域112的临界电压。

图3C显示对应图3A的俯视图300A的线段BB’的集成芯片的一些实施例的截面图300C。

在一些实施例中,第一虚拟栅极介电层136与第二虚拟栅极介电层134具有大致相等的厚度且包括相同的材料。在进一步的实施例中,第一虚拟栅极电极127与第二虚拟栅极电极128包括相同的材料。在一些实施例中,第二虚拟栅极电极128被设置在第二连续鳍片120上,且第二虚拟通道区域174具有相较于第二连续鳍片120的底部增加的掺杂浓度。在一些实施例中,第一连续鳍片116在第一虚拟通道区域176到第一连续鳍片116的底部可具有大致上相等的掺杂浓度。

图4显示集成芯片的一些实施例的俯视图400,其中第一源极/漏极区域114的第一者114a及第二者114b耦接至第一源极端子V

在此等实施例中,第一晶体管装置123a与第三晶体管装置123c之间的漏电,以及第二晶体管装置123b与第四晶体管装置123d之间的漏电是最小的。因此,第一连续鳍片116上的第一虚拟栅极电极127及下方的特征(例如:第一虚拟栅极介电层、第一虚拟通道区域等),可包括与第一连续鳍片116上的第一栅极电极122及下方的特征(例如:第一栅极介电层、第一通道区域等)相同的结构,或是与第一连续鳍片116上的第二栅极电极124及下方的特征(例如:第二栅极介电层、第三通道区域等)相同的结构。如图4的俯视图400所示,第一虚拟晶体管装置150具有与第三晶体管装置123c相同的结构与临界电压,且因此,超低临界电压n型装置区域110包括第一虚拟栅极电极127以及第一虚拟晶体管装置150。

进一步地,在一些实施例中,第二连续鳍片120上的第二虚拟栅极电极128及下方的特征(例如:第二虚拟栅极介电层、第二虚拟通道区域等),可包括与第二连续鳍片120上的第一栅极电极122及下方的特征(例如:第一栅极介电层、第二通道区域等)相同的结构,或是与第二连续鳍片120上的第二栅极电极124及下方的特征(例如:第二栅极介电层、第四通道区域等)相同的结构。如图4的俯视图400所示,第二虚拟晶体管装置152具有与第四晶体管装置123d相同的结构与临界电压,且因此,超低临界电压p型装置区域112包括第二虚拟栅极电极128以及第二虚拟晶体管装置152。

图5显示集成芯片的一些实施例的俯视图500,其中第一源极/漏极区域114的第一者114a与第二者114b中的至少一者,耦接至漏极端子(例如:V

在此等实施例中,可能会发生第一晶体管装置123a与第三晶体管装置123c之间的漏电,以及第二晶体管装置123b与第四晶体管装置123d之间的漏电。因此,为了减轻这种漏电,第一连续鳍片116上的第一虚拟栅极电极127及下方的特征(例如:第一虚拟栅极介电层、第一虚拟通道区域等),可包括与第一连续鳍片116上的第一栅极电极122及下方的特征(例如:第一栅极介电层、第一通道区域等)不同的结构,以及包括与第一连续鳍片116上的第二栅极电极124及下方的特征(例如:第二栅极介电层、第三通道区域等)不同的结构。因此,第一虚拟晶体管装置150可具有高于第一晶体管装置123a及第三晶体管装置123c的临界电压。因此,包括第一虚拟栅极电极127的标准临界电压n型装置区域540,可被设置于低临界电压n型装置区域106与超低临界电压n型装置区域110之间,以防止低临界电压n型装置区域106与超低临界电压n型装置区域110之间的漏电。

相似地,在此等实施例中,第二连续鳍片120上的第二虚拟栅极电极128及下方的特征(例如:第二虚拟栅极介电层、第二虚拟通道区域等),可包括与第二连续鳍片120上的第一栅极电极122及下方的特征(例如:第一栅极介电层、第二通道区域等)不同的结构,以及包括与第二连续鳍片120上的第二栅极电极124及下方的特征(例如:第二栅极介电层、第四通道区域等)不同的结构。因此,第二虚拟晶体管装置152可具有高于第二晶体管装置123b及第四晶体管装置123d的临界电压。因此,包括第二虚拟栅极电极128的标准临界电压p型装置区域140,可被设置于低临界电压p型装置区域108与超低临界电压p型装置区域112之间,以防止低临界电压p型装置区域108与超低临界电压p型装置区域112之间的漏电。

图6所示的流程图,是判断包含虚拟栅极电极的连续鳍片装置的设计布局是否应经过修改,以增加与虚拟栅极电极有关的虚拟栅极电极临界电压的方法600的一些实施例的流程图。此方法可借由自动设置与选路机台来执行,典型的方式是以在包括微处理器及半导体存储器的电脑系统上执行的自动设置与选路软件的形式来执行。

在操作602中,接收用于电路设计图(circuit schematic)的初始布局设计,并评估该初始布局设计,以确认由虚拟栅极电极的一部分所分隔的每一对源极/漏极区域的位置。

在操作604中,对于每一对源极/漏极区域,判断源极/漏极区域中是否至少有一者耦接到漏极电压端子。

在操作606中,若源极/漏极区域均未耦接至漏极端子,则该方法以初始布局设计继续进行,其中初始布局设计的虚拟栅极电极的一部分分隔成对的源极/漏极区域。

在操作608中,若源极/漏极区域的至少一者耦接至漏极端子,则修改初始布局设计,以增加与虚拟栅极电极有关的虚拟栅极临界电压,进而形成修改后布局设计,其中该虚拟栅极电极分隔成对的源极/漏极区域。

图7A至图7D显示对应图6的方法的各种图示700A至700D。

图7A显示半导体装置的第一功能性单元单位702及第二功能性单元单位704的示意图700A。在此范例中,第一功能性单元单位702包括第一反相器110a及第二反相器110b,而第二功能性单元单位704包括第三反相器110c及第四反相器110d。第一反相器110a包括第一输入in1以及第一输出out1,而第二反相器110b包括第二输入in2以及第二输出out2。在一些实施例中,第一输出out1可耦接到第二输入in2。相似地,在一些实施例中,第三反相器110c包括第三输入in3以及第三输出out3,且第四反相器110d包括第四输入in4以及第二输出out4。在一些实施例中,第三输出out3可耦接到第四输入in4。

如图7B的晶体管层级的示意图700B所示,第一反相器110a与第三反相器110c中的每一者,包括第一p型晶体管M1及第一n型晶体管M3。第一p型晶体管M1及第一n型晶体管M3的栅极电极耦接到输入端子(例如:用于第一反相器110a的第一输入in1、用于第三反相器110c的第三输入in3),而第一p型晶体管M1及第一n型晶体管M3的个别的漏极区域d1及d3,则耦接至输出端子(例如:用于第一反相器110a的第一输出out1、用于第三反相器110c的第三输出out3)。第二反相器110b与第四反相器110d中的每一者,包括第二p型晶体管M2及第二n型晶体管M4。第二p型晶体管M2及第二n型晶体管M4的栅极电极耦接到输入端子(例如:用于第二反相器110b的第二输入in2、用于第四反相器110d的第四输入in4),而第二p型晶体管M2及第二n型晶体管M4的漏极区域d2及d4,则分别耦接至输出端子(例如:用于第二反相器110b的第二输出out2、用于第四反相器110d的第四输出out4)。虚拟晶体管D1、虚拟晶体管D2、虚拟晶体管D3及虚拟晶体管D4亦包括在内。应理解的是,如本文所使用的术语“虚拟(dummy)”,应被理解为是指用于模仿其他结构的物理特性的结构(例如:虚拟晶体管模仿附近其他晶体管的结构完整性),且这是寄生的、电路无法操作的、及/或并非最终制造的装置中有意为之的电流的一部分。因此,尽管图7A中的示意图700A包括反相器110a-110d,但该电路示意图并未明确提及图7B中所示的虚拟晶体管D1-D4。因此,这些虚拟晶体管D1-D4是为寄生装置,这是制造上的实际情况,且在图7A的示意图700A的电路设计图中无意存在。

图7C显示对应图7B的晶体管层级的示意图700B的初始布局设计700C。初始布局设计700C再度包括由第一p型晶体管M1与第一n型晶体管M3所组成的第一反相器110a,以及由第二p型晶体管M2与第二n型晶体管M4所组成的第二反相器110b。第一p型晶体管M1及第二p型晶体管M2包括p型源极/漏极区域s1、p型源极/漏极区域d1、p型源极/漏极区域s2、p型源极/漏极区域d2,它们可被设置于第一连续鳍片116上。第一n型晶体管M3及第二n型晶体管M4包括n型源极/漏极区域s3、n型源极/漏极区域d3、n型源极/漏极区域s4、n型源极/漏极区域d4,它们可被设置于第二连续鳍片120上,其中第二连续鳍片120与第一连续鳍片116彼此间隔。因此,在一些实施例中,p型源极/漏极区域s1、d1、s2、d2被设置于第一连续鳍片116上,其中第一连续鳍片116为n型,而n型源极/漏极区域s3、d3、s4、d4被设置于第二连续鳍片120上,其中第二连续鳍片120为p型。尽管第一p型晶体管M1及第二p型晶体管M2被设置于第一连续鳍片116上,但第一p型晶体管M1可具有与第二p型晶体管M2不同的临界电压。相似地,尽管第一n型晶体管M3及第二n型晶体管M4被设置于第二连续鳍片120上,但第一n型晶体管M3可具有与第二n型晶体管M4不同的临界电压。

当虚拟栅极电极706在第一p型晶体管M1与第二p型晶体管M2之间覆盖于第一连续鳍片116上,但并未覆盖于第一功能性单元单位702的第二连续鳍片120上时,第一虚拟晶体管D1被建构于第一功能性单元单位702中。当虚拟栅极电极708在第一n型晶体管M3与第二n型晶体管M4之间覆盖于第二连续鳍片120上,但并未覆盖于第一功能性单元单位702的第一连续鳍片116上时,第二虚拟晶体管D2被建构于第一功能性单元单位702中。当虚拟栅极电极710在第一p型晶体管M1与第二p型晶体管M2之间覆盖于第一连续鳍片116上,但并未覆盖于第二功能性单元单位704的第二连续鳍片120上时,第三虚拟晶体管D3被建构于第二功能性单元单位704中。当虚拟栅极电极712在第一n型晶体管M3与第二n型晶体管M4之间覆盖于第二连续鳍片120上,但并未覆盖于第二功能性单元单位704的第一连续鳍片116上时,第四虚拟晶体管D4被建构于第二功能性单元单位704中。

如图6的操作602所述,可评估图7C的初始布局设计700C以确认由虚拟栅极电极的一部分所分隔的每一对源极/漏极区域的位置。因此,在图7C的初始布局设计700C中,第一虚拟栅极晶体管D1具有分隔第一对源极/漏极区域P1的虚拟栅极电极706,其中第一对源极/漏极区域P1包括第一漏极区域d1(亦称为p型源极/漏极区域d1)以及第二源极区域s2(亦称为p型源极/漏极区域s2)。第二虚拟栅极晶体管D2具有分隔第二对源极/漏极区域P2的虚拟栅极电极708,其中第二对源极/漏极区域P2包括第三漏极区域d3(亦称为n型源极/漏极区域d3)以及第四源极区域s4(亦称为n型源极/漏极区域s4)。第三虚拟栅极晶体管D3具有分隔第三对源极/漏极区域P3的虚拟栅极电极710,其中第三对源极/漏极区域P3包括第一源极区域s1(亦称为p型源极/漏极区域s1)以及第二源极区域s2(亦称为p型源极/漏极区域s2)。第四虚拟栅极晶体管D4具有分隔第四对源极/漏极区域P4的虚拟栅极电极712,其中第四对源极/漏极区域P4包括第三源极区域s3(亦称为n型源极/漏极区域s3)以及第四源极区域s4(亦称为n型源极/漏极区域s4)。在一些实施例中,第一至第四源极区域s1-s4可耦接至电压源(Vss、Vdd),而第一至第四漏极区域d1-d4(其中第二漏极区域d2亦称为p型源极/漏极区域d2,而第四漏极区域d4亦称为n型源极/漏极区域d4)可耦接至输出(out1-out4),或称为漏极端子。

对于图7C的初始布局设计700C中的第一对源极/漏极区域P1,当进入图6的操作604时,判断第一对源极/漏极区域P1包括至少一个漏极区域(第一漏极区域d1)。

对于图7C的初始布局设计700C中的第二对源极/漏极区域P2,当进入图6的操作604时,判断第二对源极/漏极区域P2包括至少一个漏极区域(第三漏极区域d3)。

对于图7C的初始布局设计700C中的第三对源极/漏极区域P3,当进入图6的操作604时,判断第三对源极/漏极区域P3并未包括至少一个漏极区域。

对于图7C的初始布局设计700C中的第四对源极/漏极区域P4,当进入图6的操作604时,判断第四对源极/漏极区域P4并未包括至少一个漏极区域。

如图7D的修改后布局设计700D所示,对第一对源极/漏极区域P1及第二对源极/漏极区域P2进行图6的操作608,并对第三对源极/漏极区域P3及第四对源极/漏极区域P4进行图6的操作606。

根据图6的操作606,第三虚拟晶体管D3及第四晶体管装置D4未被修改。这是因为第三虚拟晶体管D3及第四晶体管装置D4的虚拟栅极电极710及712位于相邻的源极区域之间,且因此由于源极处于相同或相似的电压电位,所以漏电的可能性很小。因此,图7C的初始布局设计700C中的第三虚拟晶体管D3与图7D的修改后布局设计700D中的第三虚拟晶体管D3具有相同的结构,并因此具有相同的临界电压。因此,图7C的初始布局设计700C中的第四虚拟晶体管D4与图7D的修改后布局设计700D中的第四虚拟晶体管D4具有相同的结构,并因此具有相同的临界电压。

根据图6的操作608,图7C的第一虚拟晶体管D1的结构被修改,以形成图7D的修改后布局设计700D中的第一修改后虚拟晶体管D1_mod。这是因为第一虚拟晶体管D1被设置于源极(第二源极区域s2)与漏极(第一漏极区域d1)之间,且这些源极与漏极区域(第二源极区域s2、第一漏极区域d1)由于在操作期间处于不同的电压电位而具有更高的漏电的可能性。因此,第一修改后虚拟晶体管D1_mod具有比图7C的初始布局设计700C中的第一虚拟晶体管D1更高的临界电压,以帮助降低图7D的修改后布局设计700D中的电流泄漏的风险。第一修改后虚拟晶体管D1_mod亦可具有比第一功能单元单位702中的第一p型晶体管M1及第二p型晶体管M2更高的临界电压,以防止第一p型晶体管M1与第二p型晶体管M2之间的漏电。

进一步地,根据图6的操作608,图7C的第二虚拟晶体管D2的结构被修改,以形成图7D的修改后布局设计700D中的第二修改后虚拟晶体管D2_mod。第二修改后虚拟晶体管D2_mod具有比图7C的初始布局设计700C中的第二虚拟晶体管D2更高的临界电压,以帮助降低图7D的修改后布局设计700D中的电流泄漏的风险。第二修改后虚拟晶体管D2_mod亦可具有比第一功能单元单位702中的第一n型晶体管M3及第二n型晶体管M4更高的临界电压,以防止第一n型晶体管M3与第二n型晶体管M4之间的漏电。

应理解的是,第一修改后虚拟晶体管D1_mod及第二修改后虚拟晶体管D2_mod的形成,可借由修改与它们有关的虚拟栅极电极(虚拟栅极电极706、708)、虚拟栅极介电层、虚拟通道区域、及/或其组合来达成,以增加“导通(允许流动的电荷载子流通穿过)”与它们有关的虚拟栅极电极下方的与它们有关的虚拟通道区域所需的与它们有关的虚拟临界电压。举例来说,在一些实施例中,可借由修改第一修改后虚拟晶体管D1_mod的虚拟栅极电极706下方的第一连续鳍片116的掺杂浓度,来形成第一修改后虚拟晶体管D1_mod,而在其他实施例中,可借由在第一修改后虚拟晶体管D1_mod的虚拟栅极电极706与第一修改后虚拟晶体管D1_mod的虚拟栅极介电层之间增加功函数层,来形成第一修改后虚拟晶体管D1_mod。功函数层可包括不同于第一修改后虚拟晶体管D1_mod的虚拟栅极电极706的材料,并因此影响第一修改后虚拟晶体管D1_mod的虚拟临界电压。

图7D的修改后布局设计700D在集成芯片上具有与图7C的初始布局设计700C相同的表面积。因此,可借由修改虚拟晶体管以增加虚拟临界电压的方式,在不增加集成芯片的表面积的情况下,减轻具有不同临界电压的晶体管之间的漏电。

图8、图9A至图9C以及图10分别显示一方法的一些实施例的透视图800、透视图900A-900C以及透视图1000,该方法以修改第一虚拟栅极电极的材料的方式,来增加与第一虚拟栅极电极有关的第一虚拟临界电压,并借此修改图7C的初始布局设计700C以形成图7D的修改后布局设计700D。尽管图8、图9A至图9C以及图10被描述为关于一种方法,但应理解的是,图8、图9A至图9C以及图10所公开的结构并不限于此种方法,而是可作为独立于此方法的独立存在的结构。

如图8的透视图800所示,第一连续鳍片116及第二连续鳍片120被形成于基板102上。第一连续鳍片116及第二连续鳍电120由基板102形成,因此第一连续鳍片116、第二连续鳍片120及基板102可包括相同的半导体材料,举例来说,例如硅、锗等。在一些实施例中,第一连续鳍片116与第二连续鳍片120可包括彼此不同的掺杂类型及/或不同的掺杂浓度。

为了形成第一连续鳍片116及第二连续鳍片120,可掺杂基板102,例如借由离子布植(ion implantation)来掺杂。在此等实施例中,可选择性地掺杂基板102,使得当第一连续鳍片116被形成时,其为p型,而当第二连续鳍片120被形成时,其为n型。在掺杂基板102后,可经由微影(photolithography)及移除(例如:蚀刻)制程移除基板102的一些部分,以形成并定义自基板102突出的第一连续鳍片116及第二连续鳍片120。隔离结构104可被形成以围绕第一连续鳍片116及第二连续鳍片120的一些部分,并覆盖基板102。在一些实施例中,隔离结构104包括介电材料,举例来说,例如氮化物(例如:氮化硅、氮氧化硅)、碳化物(例如:碳化硅)、氧化物(例如:氧化硅)、硼硅酸盐玻璃(borosilicate glass,BSG)、磷硅酸盐玻璃(phosphoric silicate glass,PSG)、硼磷硅酸盐玻璃(borophosphosilicateglass,BPSG)、低k值氧化物(例如:碳掺杂氧化物、SiCOH)等。

如图9A的透视图900A所示,在一些实施例中,第一栅极电极122可被形成在第一连续鳍片116及第二连续鳍片120上。隔离结构104、第一连续鳍片116及第二连续鳍120的其他部分可被遮罩覆盖,使得第一栅极电极122可经由沉积制程而被选择性地形成,沉积制程例如物理气相沉积(physical vapor deposition,PVD)、化学气相沉积(chemical vapordeposition,CVD)、PECVD、原子层沉积(atomic layer deposition,ALD)、溅镀(sputtering)等。在一些实施例中,第一栅极电极122可包括第一导电材料,举例来说,例如铝、钌、钯、钽、钛等。进一步地,在一些实施例中,在形成第一栅极电极122之前,可在第一连续鳍片116及第二连续鳍片120上选择性地形成第一栅极介电层(图1A的第一栅极介电层130)。在一些实施例中,第一栅极介电层(图1C的第一栅极介电层130)可具有第一厚度t

如图9B的透视图900B所示,在一些实施例中,第二栅极电极124可被形成在第一连续鳍片116及第二连续鳍片120上,且第二虚拟栅极电极128可被形成在第二连续鳍片120上。在此等实施例中,第二栅极电极124及第二虚拟栅极电极128可分别包括第二材料及第三材料,其中第二材料与第三材料相同。因为第二栅极电极124与第二虚拟栅极电极128包括相同的材料,因此它们可以同时形成。进一步地,在形成第二栅极电极124及第二虚拟栅极电极128之前,可在第一连续鳍片116及/或第二连续鳍片120上形成第二栅极介电层(图1A的第二栅极介电层132)及第二虚拟栅极介电层(图1A的第二虚拟栅极介电层134)。

在一些实施例中,第二栅极电极124的第二材料及第二虚拟栅极电极128的第三材料可不同于第一栅极电极122的第一材料,因为在一些实施例中,与被设置于第二连续鳍片120上的第二栅极电极124及第二虚拟栅极电极128有关的临界电压,不同于与被设置于第二连续鳍片上的第一栅极电极122有关的临界电压。在一些实施例中,第二栅极电极124及第二虚拟栅极电极128可包括导电材料,举例来说,例如铝、钌、钯、钽、钛等。

在一些实施例中,第二栅极介电层(图1C的第二栅极介电层132)及第二虚拟栅极介电层(图1C的第二虚拟栅极介电层134),可分别具有第二厚度(图1C的第二厚度t

如图9C的透视图900C所示,在一些实施例中,第一虚拟栅极电极127可被形成在第一连续鳍片116上。在此等实施例中,第一虚拟栅极电极127可自行包括第四材料。在一些实施例中,第一虚拟栅极电极127的第四材料,可不同于分属第一栅极电极122、第二栅极电极124及第二虚拟栅极电极128的第一材料、第二材料及第三材料。因此,第一虚拟栅极电极127可包括与第一栅极电极122及第二栅极电极124不同的材料,使得与第一虚拟栅极电极有关的临界电压,高于与被设置于第一连续鳍片116上的第一栅极电极122及第二栅极电极124有关的临界电压。在一些实施例中,举例来说,第一虚拟栅极电极127可包括一个以上的导电层,其中至导电层的至少一者包括第四材料。进一步地,在形成第一虚拟栅极电极127之前,可在第一连续鳍片116上形成第一虚拟栅极介电层(图1D的第一虚拟栅极介电层136)。在一些实施例中,第一栅极电极122、第二栅极电极124、第一虚拟栅极电极127、以及第二虚拟栅极电极128中的每一者所具有的厚度,举例来说,可处于约1纳米至约6纳米之间的范围。在一些实施例中,第一栅极电极122、第二栅极电极124、第一虚拟栅极电极127、及/或第二虚拟栅极电极128并不具有相同的厚度。

因此,可借由在第一连续鳍片116上选择性地形成第一虚拟栅极电极127来形成包括第一虚拟栅极电极127的标准临界电压n型装置区域(图5的标准临界电压n型装置区域540),其中第一虚拟栅极电极127包括与第一栅极电极122、第二栅极电极124、以及第二虚拟栅极电极128不同的材料,如图9A至图9C的透视图900A-900C所示。

如图10的透视图1000所示,在一些实施例中,第一源极/漏极区域114可被形成在第一连续鳍片116的一些部分上,其中这些部分并没有位于第一栅极电极122、第二栅极电极124或第一虚拟栅极电极127之下。在一些实施例中,第二源极/漏极区域118可被形成在第二连续鳍片120的一些部分上,其中这些部分并没有位于第一栅极电极122、第二栅极电极124或第二虚拟栅极电极128之下。在一些实施例中,可借由分别移除第一连续鳍片116及第二连续鳍片120的上方部分,并外延生长各自的第一源极/漏极区域114及第二源极/漏极区域118,来形成第一源极/漏极区域114及第二源极/漏极区域118。在其他实施例中,可借由掺杂未被第一栅极电极122、第二栅极电极124、第一虚拟栅极电极127、及/或第二虚拟栅极电极128所覆盖的第一连续鳍片116及第二连续鳍片120,来形成第一源极/漏极区域114及第二源极/漏极区域118。第一源极/漏极区域114具有与第一连续鳍片116相反的掺杂类型。举例来说,在一些实施例中,第一连续鳍片116是p型的,也因此,第一源极/漏极区域114被形成为n型。相似地,第二源极/漏极区域118具有与第二连续鳍片120相反的掺杂类型。举例来说,在一些实施例中,第二连续鳍片120是n型的,也因此,第二源极/漏极区域118被形成为p型。

图11显示对应图8、图9A至图9C以及图10的方法1100的一些实施例的流程图。

尽管下文将方法1100作为一系列的操作或事件来绘制及描述,但应理解的是,所示的此等操作或事件的顺序,不应以限制性的意义来解释。举例来说,除了本文所示及/或描述的那些操作或事件之外,某些操作能够以不同的顺序发生及/或与其他操作或事件同时发生。此外,实现本文所描述的一或多个态样或实施例可能不需要所有图示的操作。进一步地,本文所描述的一或多个操作可在一或多个单独的操作及/或阶段中执行。

在操作1102中,形成自具有第一掺杂类型的基板突出的第一连续鳍片。图8显示对应操作1102的一些实施例的透视图800。

在操作1104中,在第一连续鳍片上形成具有第一材料的第一栅极电极。图9A显示对应操作1104的一些实施例的透视图900A。

在操作1106中,在第一连续鳍片上形成具有第二材料的第二栅极电极,其中第二材料不同于第一栅极电极的第一材料。图9B显示对应操作1106的一些实施例的透视图900B。

在操作1108中,在第一栅极电极与第二栅极电极之间形成第一虚拟栅极电极,其中第一虚拟栅极电极包括不同于第一材料及第二材料的第四材料,且其中与第一虚拟栅极电极有关的临界电压,高于与第一栅极电极和第二栅极电极有关的临界电压。图9C显示对应操作1108的一些实施例的透视图900C。

在操作1110中,具有第二掺杂类型的源极/漏极区域被形成在第一连续鳍片上以及第一栅极电极、第二栅极电极与第一虚拟栅极电极之间。图10显示对应操作1110的一些实施例的透视图1000。

图12、图13A至图13C、图14A、图14B、以及图15分别显示一方法的一些实施例的透视图1200、透视图1300A-1300C、透视图1400A、透视图1400B、以及透视图1500,该方法以增加第一虚拟栅极电极下方的第一虚拟通道区域的掺杂浓度的方式,来增加与第一虚拟栅极电极有关的第一虚拟临界电压,并借此修改图7C的初始布局设计700C以形成图7D的修改后布局设计700D。尽管图12、图13A至图13C、图14A、图14B、以及图15被描述为关于一种方法,但应理解的是,图12、图13A至图13C、图14A、图14B、以及图15所公开的结构并不限于此种方法,而是可作为独立于此方法的独立存在的结构。

如图12的透视图1200所示,在一些实施例中,第一连续鳍片116、第二连续鳍片120、以及隔离结构104,可被形成在基板102上,如参照图8所述。

如图13A的透视图1300A所示,在一些实施例中,可以在第一连续鳍片116及第二连续鳍片120上形成第一遮罩结构1302。可经由图案化(例如:微影)及移除(例如:蚀刻)制程来图案化第一遮罩结构1302,以曝露第一连续鳍片116的第一部分1304,其中第一连续鳍片116的第一部分1304对应第一虚拟栅极电极(图7B的第一虚拟栅极电极127)将覆盖于第一连续鳍片116上的位置。

如图13B的透视图1300B所示,在一些实施例中,可实施掺杂制程1306,使得第二高掺杂浓度区域1308被形成在第一连续鳍片116的第一部分(图13A的第一部分1304)上。在一些实施例中,掺杂制程1306可为离子布植制程。第一遮罩结构1302可自掺杂制程1306中保护第一连续鳍片116及第二连续鳍片120的其余部分。

如图13C的透视图1300C所示,在一些实施例中,第一遮罩结构(图13B的第一遮罩结构1302)被移除。在一些实施例中,第一遮罩结构(图13B的第一遮罩结构1302)为光阻材料,且因此,第一遮罩结构(图13B的第一遮罩结构1302)经由剥离(stripping)而被移除。第一连续鳍片116包括第二高掺杂浓度区域1308,在一些实施例中,第二高掺杂浓度区域1308具有高于第一连续鳍片116的周围部分的掺杂浓度。在一些实施例中,第二高掺杂浓度区域1308与第一连续鳍片116的周围部分可包括相同的第一掺杂类型。

应理解的是,在其他实施例中,可在形成第一连续鳍片116之前,形成第一连续鳍片116的第二高掺杂浓度区域1308。在此等实施例中,举例来说,可在形成第一连续鳍片116之前在基板102上实施掺杂制程(图13B的掺杂制程1306)。

如图14A的透视图1400A所示,在一些实施例中,第一栅极电极122可被沉积在第一连续鳍片116及第二连续鳍片120上,举例来说,如参照图9A所述。

如图14B的透视图1400B所示,在一些实施例中,第二栅极电极124、第一虚拟栅极电极127及第二虚拟栅极电极128可被形成在第一连续鳍片116及第二连续鳍片120上。在一些实施例中,第二栅极电极124、第一虚拟栅极电极127及第二虚拟栅极电极128可包括相同的导电材料,举例来说,例如铝、钌、钯、钽、钛等。进一步地,在一些实施例中,第二栅极电极124,第一虚拟栅极电极127及第二虚拟栅极电极128可包括不同于第一栅极电极122的材料。

因此,可借由选择性地掺杂第一连续鳍片116的第一部分(图13A的第一部分1304)来形成包括第一虚拟栅极电极127的标准临界电压n型装置区域(图5的标准临界电压n型装置区域540),其中第一虚拟栅极电极127被设置于第一连续鳍片116的第二高掺杂浓度区域1308上,且与第一虚拟栅极电极127有关的临界电压,高于与被设置于第一连续鳍片116上的第一栅极电极122及第二栅极电极124有关的临界电压。

如图15的透视图1500所示,在一些实施例中,第一源极/漏极区域114可被形成在第一连续鳍片116的一些部分上,其中这些部分并没有位于第一栅极电极122、第二栅极电极124、或是第一虚拟栅极电极127之下。在一些实施例中,第二源极/漏极区域118可被形成在第二连续鳍片120的一些部分上,其中这些部分并没有位于第一栅极电极122、第二栅极电极124、或是第二虚拟栅极电极128之下。在一些实施例中,第一源极/漏极区域114以及第二源极/漏极区域118可使用如图10所述的方法来形成。

图16显示对应图12、图13A至图13C、图14A、图14B、以及图15的方法1600的一些实施例的流程图。

尽管下文将方法1600作为一系列的操作或事件来绘制及描述,但应理解的是,所示的此等操作或事件的顺序,不应以限制性的意义来解释。举例来说,除了本文所示及/或描述的那些操作或事件之外,某些操作能够以不同的顺序发生及/或与其他操作或事件同时发生。此外,实现本文所描述的一或多个态样或实施例可能不需要所有图示的操作。进一步地,本文所描述的一或多个操作可在一或多个单独的操作及/或阶段中执行。

在操作1602中,形成自具有第一掺杂类型的基板突出的第一连续鳍片。图12显示对应操作1602的一些实施例的透视图1200。

在操作1604中,选择性地掺杂第一连续鳍片的第一部分,以增加第一连续鳍片的第一部分的掺杂浓度。图13A至图13C显示对应操作1604的一些实施例的透视图1300A-1300C。

在操作1606中,于第一连续鳍片上形成与第一临界电压有关的第一栅极电极。图14A显示对应操作1606的一些实施例的透视图1400A。

在操作1608中,在第一连续鳍片上形成第二栅极电极以及第一虚拟栅极电极,其中第二栅极电极与第二临界电压有关且第二临界电压不同于第一临界电压,且其中第一虚拟栅极电极与第一虚拟栅极临界电压有关,并且第一虚拟栅极临界电压大于第一临界电压及第二临界电压。图14B显示对应操作1608的一些实施例的透视图1400B。

在操作1610中,源极/漏极区域被形成在第一连续鳍片上,以及第一栅极电极、第二栅极电极与第一虚拟栅极电极之间,其中源极/漏极区域具有第二掺杂类型。图15显示对应操作1610的一些实施例的透视图1500。

因此,本公开涉及一种结构及对应的方法,用于形成包括第一虚拟栅极电极的集成芯片,该第一虚拟栅极电极被设置于第一连续鳍片上,且被设置于具有第一临界电压的第一晶体管装置与具有不同于第一临界电压的第三临界电压的第三晶体管装置之间,其中若直接位于第一虚拟栅极电极旁边的至少一个源极/漏极区域耦接到漏极端子,则与第一虚拟栅极电极有关的第一虚拟临界电压被增加到大于第一临界电压及第三临界电压。

因此,在一些实施例中,本公开涉及一种多重晶体管装置的制造方法。上述制造方法包括:接收用于电路设计图的初始布局设计,初始布局设计包括设置于连续鳍片上的第一栅极电极、第二栅极电极、以及虚拟栅极电极,其中虚拟栅极电极被设置于第一栅极电极与第二栅极电极之间,第一源极/漏极区域被设置于第一栅极电极与虚拟栅极电极之间,且第二源极/漏极区域被设置于第二栅极电极与虚拟栅极电极之间,其中第一栅极电极对应具有第一临界电压的第一晶体管,第二栅极电极对应具有第二临界电压的第二晶体管,而虚拟栅极电极对应具有虚拟临界电压且分隔第一晶体管与第二晶体管的虚拟晶体管;判断第一源极/漏极区域或第二源极/漏极区域中的至少一者是否对应电路设计图中的一漏极;以及当第一源极/漏极区域或第二源极/漏极区域中的至少一者对应电路设计图中的上述漏极时,修改初始布局设计以将虚拟晶体管的虚拟临界电压增加为修改后虚拟临界电压,借此提供修改后布局设计,其中虚拟晶体管所具有的修改后虚拟临界电压高于第一临界电压及第二临界电压中的每一者。

在一或多个实施例中,第一晶体管在修改后布局设计中保持第一临界电压,且第二晶体管在修改后布局设计中保持第二临界电压。在一或多个实施例中,虚拟栅极介电层被设置于虚拟栅极电极与连续鳍片之间,且初始布局设计的修改包括:在虚拟栅极电极与虚拟栅极介电层之间形成功函数层。在一或多个实施例中,初始布局设计具有位在基板上的第一面积,且其中修改后布局设计具有位在基板上的第二面积,第二面积等于第一面积。在一或多个实施例中,初始布局设计的修改包括:调整连续鳍片的形成制程,以选择性地增加连续鳍片被虚拟栅极电极所覆盖的部分的掺杂浓度。在一或多个实施例中,初始布局设计的修改包括:调整用于形成虚拟栅极电极的沉积制程,以改变虚拟栅极电极的材料、掺杂浓度、及/或厚度。

在其他实施例中,本公开涉及一种多重晶体管装置。上述多重晶体管装置包括:一连续鳍片,自基板突出,连续鳍片在第一方向上延伸;第一晶体管装置,具有第一临界电压且包括:第一栅极电极,在基本上垂直于第一方向的第二方向上延伸,其中第一栅极电极直接覆盖连续鳍片的第一通道区域,以及包括连续鳍片的第一源极/漏极区域及第二源极/漏极区域,其中第一栅极电极将第一源极/漏极区域与第二源极/漏极区域分隔;第二晶体管装置,具有不同于第一临界电压的第二临界电压,第二晶体管装置包括:第二栅极电极,在第二方向上延伸且直接覆盖连续鳍片的第二通道区域,以及包括连续鳍片的第三源极/漏极区域及第四源极/漏极区域,其中第二栅极电极将第三源极/漏极区域与第四源极/漏极区域分隔;以及虚拟晶体管装置,具有虚拟栅极临界电压且包括:虚拟栅极电极,在第二方向上延伸且直接覆盖连续鳍片的虚拟通道区域,其中虚拟栅极电极直接位于第二源极/漏极区域与第三源极/漏极区域之间,且虚拟栅极临界电压大于第一临界电压与第二临界电压。

在一或多个实施例中,第二源极/漏极区域或第三源极/漏极区域中的至少一者耦接至漏极端子。在一或多个实施例中,虚拟栅极电极与第一栅极电极相比具有不同结构。在一或多个实施例中,上述不同结构是在材料及/或掺杂浓度上有所不同。在一或多个实施例中,连续鳍片的第一通道区域具有第一掺杂浓度,且连续鳍片的第二通道区域具有约略等于第一掺杂浓度的第二掺杂浓度。在一或多个实施例中,连续鳍片的虚拟通道区域具有第三掺杂浓度,第三掺杂浓度不同于第一掺杂浓度及第二掺杂浓度。在一或多个实施例中,上述多重晶体管装置还包括:第一栅极介电层,设置于第一栅极电极与连续鳍片的第一通道区域之间;第二栅极介电层,设置于第二栅极电极与连续鳍片的第二通道区域之间;以及虚拟栅极介电层,设置于虚拟栅极电极与虚拟通道区域之间,其中虚拟栅极介电层具有不同于第一栅极介电层及第二栅极介电层的厚度。

在又一些实施例中,本公开涉及一种集成芯片。上述集成芯片包括:第一连续鳍片,设置于基板上且在第一方向上延伸;第二连续鳍片,设置于基板上,在第一方向上延伸,且在基本上垂直于第一方向的第二方向上与第一连续鳍片间隔;第一栅极电极,在第二方向上延伸,且被设置于第一连续鳍片的第一通道区域上以定义第一晶体管装置,并被设置于第二连续鳍片的第二通道区域上以定义第二晶体管装置;第二栅极电极,在第二方向上延伸,且被设置于第一连续鳍片的第三通道区域上以定义第三晶体管装置,并被设置于第二连续鳍片的第四通道区域上以定义第四晶体管装置;第一虚拟栅极电极,设置于第一栅极电极与第二栅极电极之间,且被设置于第一连续鳍片的第一虚拟通道区域上以定义第一虚拟晶体管装置,其中第一虚拟晶体管装置与第一晶体管装置共享一第一源极/漏极区域,且第一虚拟晶体管装置与第三晶体管装置共享第二源极/漏极区域;以及第二虚拟栅极电极,设置于第一栅极电极与第二栅极电极之间,且被设置于第二连续鳍片的第二虚拟通道区域上以定义第二虚拟晶体管装置,其中第二虚拟栅极电极在第二方向上与第一虚拟栅极电极间隔,其中第二虚拟晶体管装置与第二晶体管装置共享第三源极/漏极区域,且第二虚拟晶体管装置与第四晶体管装置共享第四源极/漏极区域;其中第一晶体管装置具有不同于第三晶体管装置的临界电压,且第一虚拟晶体管装置具有高于第一晶体管装置及第三晶体管装置的临界电压。

在一或多个实施例中,第二晶体管装置具有不同于第四晶体管装置的临界电压,且第二虚拟晶体管装置具有高于第二晶体管装置及第四晶体管装置的临界电压。在一或多个实施例中,第二虚拟晶体管装置具有与第四晶体管装置约略相等的临界电压。在一或多个实施例中,第三源极/漏极区域及上述第四源极/漏极区域耦接至源极端子。在一或多个实施例中,第一源极/漏极区域或第二源极/漏极区域中的至少一者耦接至漏极电压端子。在一或多个实施例中,第一通道区域及第三通道区域中的每一者具有第一掺杂浓度,而第一虚拟通道区域具有上述第一掺杂浓度的第二掺杂浓度。在一或多个实施例中,第一虚拟栅极电极与第二虚拟栅极电极包括不同的结构。

前述内文概述多项实施例或范例的特征,如此可使于本技术领域中具有通常知识者更佳地了解本公开的态样。本技术领域中具有通常知识者应当理解他们可轻易地以本公开为基础设计或修改其他制程及结构,以完成相同的目的及/或达到与本文介绍的实施例或范例相同的优点。本技术领域中具有通常知识者亦需理解,这些等效结构并未脱离本公开的精神及范围,且在不脱离本公开的精神及范围的情况下,可对本公开进行各种改变、置换以及变更。

- 集成芯片、多重晶体管装置及其制造方法

- 薄膜晶体管用感光性树脂组合物、固化膜、薄膜晶体管、液晶显示装置或有机场致发光显示装置、固化膜的制造方法、薄膜晶体管的制造方法以及液晶显示装置或有机场致发光显示装置的制造方法