一种马达H桥驱动电路芯片版图布局

文献发布时间:2023-06-19 12:21:13

技术领域

本发明涉及马达驱动电路芯片版图技术,特别是一种马达H桥驱动电路芯片版图布局,通过在版图布局中将H桥驱动电路低边区设置在其他电路模块区的远端,而将H桥驱动电路高边区设置在其他电路模块区的近端,能够弱化马达从运转突变至滑行后的电感续流导致的低边漏极端负压影响,还能够通过设置多道NBL+HVNW隔离环或隔离层隔离负压,从而有利于保障芯片的工作稳定性。

背景技术

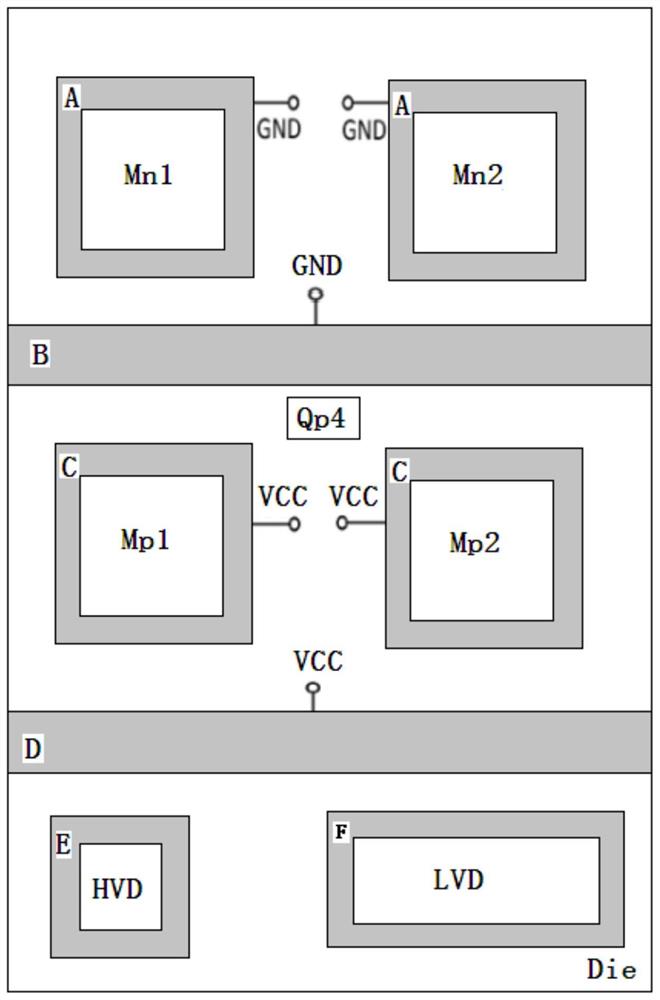

图1是马达驱动类产品典型的H桥驱动级芯片电路示意图。如图1所示,Mp1、Mp2为高边High-side(PMOS管),Mn1、Mn2为低边Low-side(NMOS管);当Mp1、Mn2或者Mp2、Mn1开启,为马达运转状态;当Mp1、Mp2、Mn1、Mn2均关闭,为马达滑行状态。如图1所示,当马达处在运转状态,马达绕组线圈内存在电流Iload,此时立即进入滑行状态,由于电感电流Iload不能突变,所以Iload需要经过Mp2的体二极管D2向VCC续流(即把OUT2点电位抬升,VOUT2>VCC+Vdiod),经过Mn1的体二极管D3向GND续流(即把OUT1点电位拉低,VOUT1 发明内容 本发明针对现有技术中存在的缺陷或不足,提供一种马达H桥驱动电路芯片版图布局,通过在版图布局中将H桥驱动电路低边区设置在其他电路模块区的远端,而将H桥驱动电路高边区设置在其他电路模块区的近端,能够弱化马达从运转突变至滑行后的电感续流导致的低边漏极端负压影响,还能够通过设置多道NBL+HVNW隔离环或隔离层隔离负压,从而有利于保障芯片的工作稳定性。 本发明的技术方案如下: 一种马达H桥驱动电路芯片版图布局,其特征在于,包括H桥驱动电路高边区和H桥驱动电路低边区,以及其他电路模块区,所述H桥驱动电路低边区位于所述其他电路模块区的远端,所述H桥驱动电路高边区位于所述其他电路模块区的近端。 所述H桥驱动电路低边区包括左半部第一NMOS管和右半部第二NMOS管,所述第一NMOS管和所述第二NMOS管以一对一的方式被两个第一道NBL+HVNW隔离环分别环绕。所述第一道NBL+HVNW隔离环连接固定强源接地端。 所述H桥驱动电路低边区与所述H桥驱动电路高边区之间设置有第二道NBL+HVNW隔离层,所述第二道NBL+HVNW隔离层连接固定强源接地端。 所述H桥驱动电路高边区包括左半部第一PMOS管和右半部第二PMOS管,所述第一PMOS管和所述第二PMOS管以一对一的方式被两个第三道NBL+HVNW隔离环分别环绕,所述第三道NBL+HVNW隔离环连接电源电压端。 所述H桥驱动电路高边区与所述其他电路模块区之间设置有第四道NBL+HVNW隔离层,所述第四道NBL+HVNW隔离层连接电源电压端。 所述其他电路模块区包括左半部高压器件和右半部低压器件,所述高压器件被高压器件NBL+HVNW隔离环围绕,所述低压器件被低压器件NBL+HVNW隔离环围绕,所述高压器件NBL+HVNW隔离环连接相对强源以保护支路电流,所述低压器件NBL+HVNW隔离环连接相对强源以保护内部器件。 所述H桥驱动电路的几何中心设置有第四感温PNP三极管。 所述第二道NBL+HVNW隔离层的中部下沿与所述第三道NBL+HVNW隔离环上部外沿之间设置有第四感温PNP三极管。 本发明的技术效果如下:本发明一种马达H桥驱动电路芯片版图布局,针对H桥Low-side的Drain端负压对其他器件影响最大这一现象,刻意将Low side放在Die的远端,距离其他电路模块(偏置电路、控制电路、保护电路)尽可能远,这样能够尽可能弱化负压影响。对于多道NBL+HVNW隔离,其均能起到隔离负压的作用,例如第一道NBL+HVNW隔离环连接固定强源接地端GND,既能隔离负压,又能降低功耗,并且该隔离层接固定强源GND,还能屏蔽激烈动作的输出端OUT(通过寄生电容)对P型基板PSUB的冲击影响。 附图说明 图1是马达驱动类产品典型的H桥驱动级芯片电路示意图。图1中第一PMOS管Mp1、第二PMOS管Mp2为高边High-side,第一NMOS管Mn1、第二NMOS管Mn2为低边Low-side。当Mp1、Mn2开启或者Mp2、Mn1开启,马达为运转状态。当Mp1、Mp2、Mn1、Mn2均关闭,马达为滑行状态。图1中马达运转时其绕组线圈L(即电感L)内存在负载电流Iload(即电感电流Iload)。 图2是图1中马达从运转突变至滑行时形成的第一寄生NPN三极管Qn1示意图。图2中的Qn1以周围N型器件N+为集电极,以P型基板端(即PSUB端)为基极,以低边Low-side(例如Mn1)的漏极为发射极。由于电感电流Iload不能突变,所以Iload需要经过Mp2的第二体二极管D2向电源电压端VCC续流(即抬升第二输出节点OUT2的电位VOUT2,使VOUT2>VCC+Vdiod),同时,续流使得第一输出节点OUT1的电位VOUT1被拉低,使VOUT1 图3是图1中马达从运转突变至滑行时形成的第二寄生PNP三极管Qp2示意图。图3中的Qp2以高边High side(例如Mp2)的漏极为发射极,以电源电压端VCC为基极,以P型基板端(即PSUB端)为集电极。 图4是实施本发明一种马达H桥驱动电路芯片版图布局的结构示意图。 图5是图4中第四感温PNP三极管Qp4的感温原理示意图。图5中,当Ib为固定电流,三极管的VBE压差随温度几乎线性变化。 图6是第三感温NPN三极管Qn3的感温原理示意图。图6中,当Ib为固定电流,三极管的VBE压差随温度几乎线性变化。用于感温时,NPN型三极管的基极和集电极是连接在一起的,构成Diod(二极管)形式。 附图标记列示如下:VCC-电源电压或电源电压端;GND-接地端;OUT1-第一输出节点;OUT2-第二输出节点;L-马达绕组线圈或电感;Iload-负载电流或电感电流;Mp1-第一PMOS管;Mp2-第二PMOS管;Mn1-第一NMOS管;Mn2-第二NMOS管;D1~D4-第一至第四体二极管(寄生二极管);Qn1-第一寄生NPN三极管;N+-周围N型器件;PSUB-P型基板;OUT-输出级;Qp2-第二寄生PNP三极管;Qn3-第三感温NPN三极管;Vt-感温电压;Ib-感温三极管电流;Qp4-第四感温PNP三极管;Die-芯片;HVD-高压器件;LVD-低压器件;A-第一道NBL+HVNW隔离环(NBL指N埋层,HVNW指高压N阱);B-第二道NBL+HVNW隔离层;C-第三道NBL+HVNW隔离环;D-第四道NBL+HVNW隔离层;E-高压器件NBL+HVNW隔离环;F-低压器件NBL+HVNW隔离环。 具体实施方式 下面结合附图(图1-图6)对本发明进行说明。 图1是马达驱动类产品典型的H桥驱动级芯片电路示意图。图2是图1中马达从运转突变至滑行时形成的第一寄生NPN三极管Qn1示意图。图3是图1中马达从运转突变至滑行时形成的第二寄生PNP三极管Qp2示意图。图4是实施本发明一种马达H桥驱动电路芯片版图布局的结构示意图。图5是图4中第四感温PNP三极管Qp4的感温原理示意图。图6是第三感温NPN三极管Qn3的感温原理示意图。如图4所示,同时参考其他附图,一种马达H桥驱动电路芯片版图布局,包括H桥驱动电路高边区和H桥驱动电路低边区,以及其他电路模块区(图4的图面下部),所述H桥驱动电路低边区位于所述其他电路模块区的远端(图4的图面上部),所述H桥驱动电路高边区位于所述其他电路模块区的近端(图4的图面中部)。所述H桥驱动电路低边区包括左半部第一NMOS管Mn1和右半部第二NMOS管Mn2,所述第一NMOS管Mn1和所述第二NMOS管Mn2以一对一的方式被两个第一道NBL+HVNW隔离环A分别环绕。所述第一道NBL+HVNW隔离环A连接固定强源接地端GND。所述H桥驱动电路低边区与所述H桥驱动电路高边区之间设置有第二道NBL+HVNW隔离层B,所述第二道NBL+HVNW隔离层B连接固定强源接地端GND。所述H桥驱动电路高边区包括左半部第一PMOS管Mp1和右半部第二PMOS管Mp2,所述第一PMOS管Mp1和所述第二PMOS管Mp2以一对一的方式被两个第三道NBL+HVNW隔离环C分别环绕,所述第三道NBL+HVNW隔离环C连接电源电压端VCC。所述H桥驱动电路高边区与所述其他电路模块区之间设置有第四道NBL+HVNW隔离层D,所述第四道NBL+HVNW隔离层D连接电源电压端VCC。所述其他电路模块区包括左半部高压器件HVD和右半部低压器件LVD,所述高压器件HVD被高压器件NBL+HVNW隔离环E围绕,所述低压器件LVD被低压器件NBL+HVNW隔离环F围绕,所述高压器件NBL+HVNW隔离环E连接相对强源以保护支路电流,所述低压器件NBL+HVNW隔离环F连接相对强源以保护内部器件。所述H桥驱动电路的几何中心设置有第四感温PNP三极管Qp4。所述第二道NBL+HVNW隔离层B的中部下沿与所述第三道NBL+HVNW隔离环C上部外沿之间设置有第四感温PNP三极管Qp4。 从背景技术对图1的分析可知,H桥Low-side的Drain端负压对其他器件影响最大。所以在图4中把Low side放在Die的最远端,距离其他电路模块(偏置电路、控制电路、保护电路)尽可能远,尽可能弱化负压影响。 如图4中A所示,NBL+HVNW形成一个“浴缸”,对Low side进行一次隔离,NBL+HVNW与Low side的Drain端形成NPN(如图2所示,NBL+HVNW为集电极,BULK端为基极,Low side的Drain端为发射极),提供负压漏电流,NBL+HVNW电位越高,提供电流能力越强,即屏蔽负压能力越强,但功率损耗也越大(P=V*I),隔离层越容易被烧毁。所以折衷设计,NBL+HVNW接强源GND,既能隔离负压,又能降低功耗。并且该隔离层接固定强源GND,还能屏蔽激烈动作的OUT(通过寄生电容)对PSUB的冲击影响。 如图4中B所示,在Low side下方,再加一道NBL+HVNW,接强源GND电位,来提供残余负压漏电流,进行二次隔离负压,隔离原理同上。 上述分析可知,在续流过程中,High side的Drain端会产生过压,与PSUB形成PNP寄生三极管(如图3所示,High side的Drain端为发射极,BULK端为基极,PSUB为集电极),向PSUB漏电,这样正好会抵消被Low side负压拉负的PSUB,且High side的隔离环为接VCC的NBL+HVNW(如图4中C所示),能起到三次隔离负压作用。 如图4所示,第四感温PNP三极管Qp4放置于H桥的几何中心,由于H桥正常运转时,为斜对角开关管开启工作(Mp1、Mn2或者Mp2、Mn1开启),所以几何中心的温度为平均温度。 如图5和图6所示,为感温三极管工作原理图,当感温三极管电流Ib为固定电流,三极管的VBE压差随温度几乎线性变化,由于具有这个特性,三极管可用于检测温度。如果用NPN型三极管(例如图6中的第三感温NPN三极管Qn3)检测温度,在H桥Low side出现负压时,N型的集电极会出现漏电,干扰其检测温度(如图6中的VBE会被拉低),出现误动作。本发明采用PNP型三极管(例如图5中的第四感温PNP三极管Qp4)检测温度,N型的B端在最外层,且接强源GND,来提供负压漏电流,所以使得负压不会影响发射极E与基极B的感温节的温度检测。 如图4中D所示,最终,在动作激烈的H桥驱动级Low side和High side下再加一道NBL+HVNW隔离层,进行四次隔离,且接VCC高电位,由于经过上层的三道隔离,此时残余负压漏电流已经不多,所以接VCC不会产生过多的功率损耗,还能进一步加强隔离负压效果。 如图4中E所示,其他电路模块中的所有高压器件HVD的隔离环电位,需要接相对强源,保护支路电流,隔离原理同上。如图4中F所示,其他电路模块中的所有低压器件LVD,需要被NBL+HVNW隔离环保护,且接相对强源,保护内部器件,隔离原理同上。 在此指明,以上叙述有助于本领域技术人员理解本发明创造,但并非限制本发明创造的保护范围。任何没有脱离本发明创造实质内容的对以上叙述的等同替换、修饰改进和/或删繁从简而进行的实施,均落入本发明创造的保护范围。

- 一种马达H桥驱动电路芯片版图布局

- 一种可通过电信号切换的双H桥马达驱动电路