忆阻器-CMOS逻辑模块及因式分解超前进位加法器

文献发布时间:2023-06-19 12:21:13

技术领域

本发明属于加法器技术领域,具体涉及一种忆阻器-CMOS逻辑模块及基于忆阻器-CMOS逻辑模块的因式分解超前进位加法器。

背景技术

作为减、除、乘等运算的基础,加法运算是最重要、最基本的运算。加法器常被用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用等。在后摩尔时代,不断缩小特征尺寸已超越物理承受的极限,摩尔定律已难以延续下去。1971年chua教授发现并证明了忆阻器的存在,忆阻器是除电阻、电感、电容之外的第四种基本元件。忆阻器具有非易失性、记忆性、纳米尺寸、与CMOS兼容等特性。众多科研成果表明,忆阻器将成为延续摩尔定律的新型元件。所以基于忆阻器-CMOS逻辑的新型因式分解超前进位加法器拓扑电路的设计与仿真实现具有实际应用意义。

发明内容

本发明的目的在于提供一种忆阻器-CMOS逻辑模块。

本发明的目的通过如下技术方案来实现:包括第一忆阻器U

本发明的目的还在于提供一种基于忆阻器-CMOS逻辑模块的因式分解超前进位加法器。

本发明的目的通过如下技术方案来实现:包括三部分,第一部分产生进位传播和进位生成函数,第二部分完成进位的因式分解,第三部分完成进位和求和;所述的第一部分包括四组忆阻器-CMOS逻辑模块;所述的第二部分包括二十组忆阻器;所述的第三部分包括四组忆阻器-CMOS逻辑模块和十四组忆阻器。

本发明还可以包括:

所述的第一部分包括第一组忆阻器-CMOS逻辑模块、第二组忆阻器-CMOS逻辑模块、第三组忆阻器-CMOS逻辑模块、第四组忆阻器-CMOS逻辑模块;

所述的第一组忆阻器-CMOS逻辑通用模块包括第一忆阻器U

所述的第二组忆阻器-CMOS逻辑通用模块包括第五忆阻器U

所述的第三组忆阻器-CMOS逻辑通用模块包括第九忆阻器U

所述的第四组忆阻器-CMOS逻辑通用模块包括第十三忆阻器U

所述的第二部分包括第十七忆阻器U

所述的第十七忆阻器U

所述的第三十四忆阻器U

所述的第三部分包括第二十九忆阻器U

所述的第三十忆阻器U

所述的第二部分中第三十九忆阻器U

所述的第五组忆阻器-CMOS逻辑通用模块包括第四十三忆阻器U

所述的第四十七忆阻器U

所述的第六组忆阻器-CMOS逻辑通用模块包括第五十一忆阻器U

所述的第六十二忆阻器U

所述的第七组忆阻器-CMOS逻辑通用模块包括第五十五忆阻器U

所述的第八组忆阻器-CMOS逻辑通用模块包括第六十三忆阻器U

本发明的有益效果在于:

本发明提供了利用因式分解将逻辑分解,后将逻辑物理融合在一起的基于忆阻器-CMOS逻辑模块的超前进位加法器拓扑电路结构。在本发明的拓扑电路结构下,减少了器件使用数量和功耗,实现更高速的加法运算。

附图说明

图1是忆阻器模型图。

图2是忆阻器-CMOS逻辑模块的电路图。

图3是忆阻器-CMOS逻辑模块的仿真图。

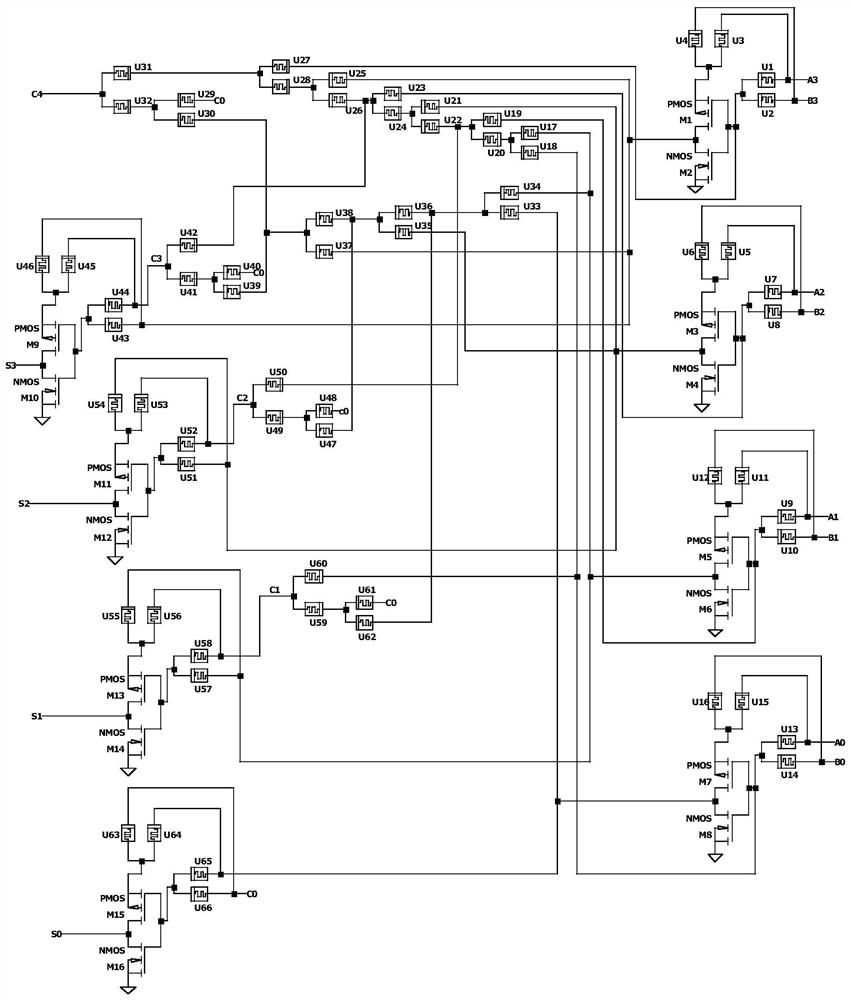

图4是基于忆阻器-CMOS逻辑模块的因式分解超前进位加法器的电路图。

图5是基于忆阻器-CMOS逻辑模块的因式分解超前进位加法器的仿真图。

具体实施方式

下面结合附图对本发明做进一步描述。

本发明涉及一种基于忆阻器-CMOS逻辑的新型因式分解超前进位加法器的拓扑电路结构设计与仿真实现。本发明提供了利用因式分解将逻辑分解,后将逻辑物理融合在一起的基于忆阻器-CMOS逻辑模块的超前进位加法器拓扑电路结构。在本发明的拓扑电路结构下,减少了器件使用数量和功耗,实现更高速的加法运算。

本发明采用如下技术手段实现发明目的:

S1:忆阻器模型调试与仿真。

S11:将平均亚稳态开关忆阻器spice模型导入到LTspice中进行调试,直到能够完成正确的布尔逻辑。

S12:经过调试给定初试参数为:R

S13:对调试好的忆阻器进行仿真测试。

S2:引入忆阻器-CMOS逻辑通用模块。利用次模块产生P

S3:基于忆阻器-CMOS逻辑的新型因式分解超前进位加法器拓扑电路结构的搭建,包括以下步骤:

S31:对超前进位加法逻辑表达式进行逻辑因式分解。

C

S32:令W

S33:根据

S1中首先对忆阻器的数学模型进行分析:

平均亚稳态开关忆阻器数学模型:

dX=N

(4)式中dX描述开关数量的变化(范围为0到1)。

(5)式中P

(6)式为开关的状态数,将此式代入下式中可得开关状态数关于时间t对的微分方程。

(8)式为忆阻器电导的总和,将忆阻器建模为两个并联的电阻,阻值通过X相互耦合。根据欧姆定律,得到忆阻器两端的电压,其中电流和电导都是函数。

I=V·G (9)

经过S11、S12、S13将调试好的忆阻器SPICE模型导入到LTspice中,在LTspice中建立图1所示的忆阻器模型。图1为忆阻器在LTspice中的Symbol,其中左侧为极性端,右侧为非极性端。电流由极性端流入忆阻设备后,忆阻器的阻值下降,直至R

本发明的拓扑电路结构包括三个部分:

第一部分产生进位传播和进位生成函数P

利用图1所示的忆阻器模型,搭建忆阻器-CMOS逻辑通用模块,如图2所示。图2为忆阻器-CMOS逻辑通用模块,由忆阻器U

验证S2中构建的忆阻器-CMOS通用模块的逻辑功能,图3为忆阻器-CMOS逻辑通用模块仿真图。A

在S1、S2的准备工作后根据S3构建新型因式分解超前进位加法器,得到图4。

图4为基于忆阻器-CMOS逻辑的新型因式分解超前进位加法器电路,此电路由三部分构成:第一部分产生进位传播和进位生成函数、第二部分完成进位的因式分解、第三部分完成进位和求和。

第一部分:忆阻器U

忆阻器U

忆阻器U

忆阻器U

第二部分:忆阻器U

忆阻器U

第三部分:忆阻器U

忆阻器U

忆阻器U

忆阻器U

忆阻器U

忆阻器U

忆阻器U

验证S3中构建的新型超前进位加法器电路的逻辑功能,图5为基于忆阻器-CMOS逻辑的新型因式分解超前进位加法器仿真图,对A

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 忆阻器-CMOS逻辑模块及因式分解超前进位加法器

- 一种基于可逆逻辑的16位超前进位加法器