一种宽频带收发芯片内部高精度PLL输出频率的校准方法

文献发布时间:2023-06-19 12:24:27

技术领域

本发明涉及无线通信领域,特别是一种宽频带收发芯片内部高精度PLL(PhaseLocked Loop,内锁相环)输出频率的校准方法。

背景技术

在通信系统中,终端射频电路的本振频率精度对系统信号的收发有着很大影响。如果本振频率偏差过大将导致终端无法正常与基站(或终端)正常通信,即便偏差较小,终端和基站通过适当的处理纠正频偏可以正常通信,但是会增大终端的正确解调解码信号的难度,即终端收机的性能降低,还有可能导致基站错误解码终端的发射信号,导致通信的错误。因此,在终端射频电路的设计中通常采用外部PLL芯片来保证射频本振的精度。但是,采用外置PLL芯片增加了电路设计的难度和复杂度,不利于系统的集成。同时随着无线通信的发展,射频本振频率要求越来越高,使得本振信号易于在电路板上产生高频电磁辐射,对其他电路产生干扰。因此,近几年推出的宽频带射频收发芯片都开始内部集成PLL锁相环电路作为收发链路的本振信号。用户可以通过频率控制字对芯片内部集成PLL的输出频率进行控制,但是由于频率控制字精度、受到温度及射频放大器的线性度影响,本振频率通常会出现较大的偏移,为此,现有文献也提供了一些解决方法,如:文献1(周斌,崔葛瑾.采用遗传算法对AVR片内RC校频处理.微型电脑应用,2009,25(004):54-57)利用遗传算法对AVR片内的RC振荡器进行实时校准,在遗传变异概率取值为0.01时,在遗传算法进行10次迭代后,AVR片内振荡器的频率偏差为2%,但是,所提出的基于遗传算法的频率校准算对于频率控制字的输入位数有限制,算法的计算时间和迭代次数会随着频率控制字的位数增加而增加,从而占用过多的CPU资源。

文献2(范文晶,王召利,周渭.改进卡尔曼滤波算法在时钟驯服技术中的应用.宇航计测技术,2016,36(03):46-49.)提出了一种改进的Kalman滤波算法来消除时钟驯服系统中GPS信号随机抖动的方法,由实验结果可见,该算法很好的消除了抖动带来的误差,将误差控制在了±2ns之内,但是,所提出的采用改进曼德拉算法消除时钟驯服系统中GPS信号随机抖动的方法其精度为±2ns,这个对于高频率的无线通信系统不太适用,而且也存在与文献1相同的问题。

文献3(高帅,谷力,刘烈曙.高精度时间间隔测量在时间比对和频率校准中的应用.现代导航,2016,7(04):239-245.)提出了高精度时间间隔测量方法,并对时间比对和频率校准的实例进行了讨论和说明。

文献4(何光宇.基于内插法的频率校准系统.舰船电子对抗,2008(05):111-113+117.)提出了一种内插法的频率校准系统主要包括引导电路、微波器件、瞬时测量电路。

文献3和文献4在对系统频率进行校准时都需要额外添加测量模块,这样会增加电路的复杂度,增加额外的成本,其精度也不好保证。

因此,综合现有技术,目前大多的频率校准方法主要的缺点有:1、额外添加测量电路,增加成本;2、校准算法过多占用CPU资源,降低系统性能。因此,如何快速准确的对芯片内部PLL的频率进行校准,以减小其输出频率偏移量提高频率精度是亟需解决的技术问题。

发明内容

针对上述情况,为克服现有技术之缺陷,本发明之目的就是提供一种宽频带收发芯片内部高精度PLL输出频率的校准方法,可有效解决现有频率校准方法需要额外添加测量电路,增加成本以及校准算法过多占用CPU资源,降低系统性能,不能达到快速准确的对芯片内部PLL的频率进行校准,以减小其输出频率偏移量提高频率精度的问题。

为实现上述目的,本发明解决的技术方案是,一种宽频带收发芯片内部高精度PLL输出频率的校准方法,在确定宽频带收发芯片PLL频率误差范围后,根据系统特性选取参考点进行测量,得到一组结果,然后将宽频带收发芯片PLL各个频率误差等级值在此组结果内进行线性插值,得到频率误差与频率控制字之间的折线关系模型,然后将此模型算法写入系统中,以芯片内部PLL频率控制字设置频率值为基准,采用线性耦合的方式,对芯片内部PLL的频率进行校准,给出折线模型算法的操作流程,实现对宽频带收发芯片内部的PLL输出频率进行校准。

进一步地,所述的频率偏移量的表达式设为:y=a

(1)、将评估板的发射端与频谱分析仪连接,设置系统时钟,平台发射单音正弦波信号数据,平台的测试代码衰减数设为0,采用DDS模式;

(2)、控制评估板发射端中心的本振频率,设定本振频率F

(3)、确定频率误差Fn与频率控制字fn之间的关系:

(4)、对步骤(3)计算出来的a

(5)、将步骤(3)和(4)的结果写入系统的文件系统;

(6)、在每次频率控制字改变时,通过查询折线值对频率控制字进行补偿,进而达到对PLL输出频率的校准。

进一步地,所述的评估板为KC705+AD系列评估板。

所述的系统时钟设为122.88MHz。

本发明方法可靠、易实现,在改变原有无线电传输系统的情况下,通过算法对系统本振频率进行校准,降低了系统成本及电路的复杂程度,降低了算法对CPU的占用时间,可以提高系统CPU利用率,有显著的社会和经济效益。

附图说明

图1是本发明芯片内部PLL的结构图。

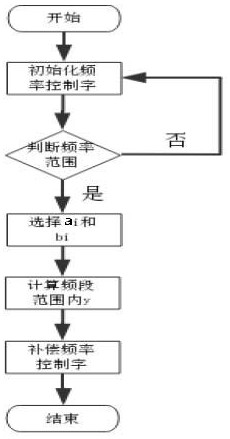

图2是本发明PLL频率校准程序流程图。

具体实施方式

以下结合附图和具体情况对本发明的具体实施方式作详细说明。

本发明在具体实施时,可有以下实施例实现,具体实验资料如下:

在宽频带收发芯片中的锁相环合成器是由一个由相位频率检测器(鉴相器)、电荷泵、环路滤波器、反馈分频器和核心压控振荡器(VCO)构成。根据宽频带收发芯片的技术指导书可知:在宽频带收发芯片中PLL的输出频率是通过频率控制字来进行设置。其输出频率与频率控制字之间在全频带满足下面公式(1)和(2)

Count=频率控制字/LO步进 (1)

Actual LO Frequency=Count*LO步进 (2)

设备在不同PLL输出频段上均满足公式(1)和(2),那么也就是说PLL的输出频率在一定频段内可以认为其与频率控制字为线性关系,故也可以认为其频率偏移量与频率控制字之间亦为线性关系,因此,可以采用折线耦合算法对校准PLL输出频率进行校准,设频率偏移量的表达式如式(3)所示。

y=a

其中a

本发明采用折线耦合算法对芯片内部PLL输出频率进行校准,具体包括以下步骤:

(1)、将KC705+AD系列评估板的发射端与频谱仪连接,系统时钟为122.88MHz,平台发射数据都为单音正弦波信号,平台的测试代码衰减数设为0,采用DDS模式;

(2)、控制KC705+AD系列评估板的发射端中心的本振频率,设定本振频率F

(3)、确定频率偏差与频率控制字之间的关系:

(4)、对步骤(3)计算出来的ai和bi的结果求平均数,确定折线;

(5)、将步骤(3)和(4)的结果写入系统的文件系统;

(6)、在每次频率控制字改变时软件通过查询折线值对频率控制字进行补偿,进而达到对PLL输出频率的校准。

本发明经多次不同量的测试,均取得了与实施例相同或相近似的结果,表明方法稳定、可靠,这里不再一一赘述。

要指出的是,上述仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出更动或者修饰为等同变化的等效实施例,均落在本发明的保护范围内。

本发明采用一种使用折线模型算法对宽频带收发芯片内锁相环(PLL)输出频率进行校准,方法可靠、易实现,与现有技术相比,有以下优点:

1、适用于大部分宽频带收发芯片内部PLL输出频率的校准,适用面广;

2、在改变原有无线电传输系统的情况下,通过算法对系统本振频率进行校准,降低了系统成本及电路的复杂程度;

3、采用关键点测量加折线模拟的方法降低了算法对CPU的占用时间,可以提高系统CPU利用率,有显著的社会和经济效益。

- 一种宽频带收发芯片内部高精度PLL输出频率的校准方法

- 一种宽频带高精度接收机的功率校准装置及方法