晶体管及其制作方法

文献发布时间:2023-06-19 12:24:27

技术领域

本发明涉及半导体技术领域,特别涉及一种晶体管及其制作方法。

背景技术

Planar(平面栅)IGBT(绝缘栅双极型晶体管)、Planar VDMOS(声效应功率晶体管)等属于半导体行业中常见的晶体管。但是,采用现有的晶体管制造工艺生产平面栅IGBT时普遍会造成Vcesat(声效应功率晶体管)变大,或生产平面栅VDMOS时普遍会造成Rdson(导通电阻)变大的情况发生,不能满足实际制作要求。

发明内容

本发明要解决的技术问题是为了克服现有技术中的晶体管制造工艺会使得平面栅IGBT的Vcesat或VDMOS的Rdson变大的缺陷,目的在于提供一种晶体管及其制作方法,以避免平面栅IGBT或VDMOS的Vth(阈值电压)离散,同时使得平面栅IGBT的Vcesat或VDMOS的Rdson不发生变大的情况。

本发明是通过下述技术方案来解决上述技术问题:

本发明提供一种晶体管的制作方法,所述制作方法包括:

提供半导体衬底;

在所述半导体衬底上形成栅氧化层;

在所述栅氧化层上形成多晶硅层;

对所述多晶硅层进行刻蚀,并沿着刻蚀方向在所述半导体衬底中注入P型离子以形成P阱区;

沿着所述刻蚀方向对所述栅氧化层进行刻蚀,并注入n种目标离子以形成N区;n≥1且取整数;

其中,n种所述目标离子中的至少一种所述目标离子的扩散系数大于硼离子的扩散系数;

所述P阱区包饶在所N区外部;

在所述栅氧化层和所述多晶硅层的沿着所述刻蚀方向的侧壁上处形成侧墙;

沿着所述侧墙依次注入P+离子和N+离子。

较佳地,所述沿着所述刻蚀方向对所述栅氧化层进行刻蚀,并注入目标离子以形成N区的步骤包括:

沿着所述刻蚀方向对所述栅氧化层进行刻蚀;

在刻蚀后,沿着所述刻蚀方向注入磷离子;

沿着所述刻蚀方向注入目标离子以形成所述N区。

较佳地,所述在所述栅氧化层和所述多晶硅层的沿着所述刻蚀方向的侧壁上处形成侧墙的步骤之后、所述沿着所述侧墙依次注入P+离子和N+离子的步骤之前还包括:

对所述侧墙进行回流处理以加固所述侧墙。

较佳地,所述沿着所述侧墙依次注入P+离子和N+离子的步骤包括:

沿着所述侧墙向所述N区中注入P+离子以形成P+区;

沿着所述侧墙向所述N区中注入N+离子以形成N+区;

其中,所述N+离子为高浓度砷离子;

所述P+区穿透所述N区且未穿透所述P阱区,所述N+区未穿透所述N区。

较佳地,所述晶体管包括平面栅IGBT。

较佳地,所述平面栅IGBT包括平面型IGBT、平面型FS IGBT、平面型CS IGBT或平面型FS CS IGBT(平面型IGBT、平面型FS IGBT、平面型CS IGBT以及平面型FS CS IGBT均为一种晶体管)。

较佳地,所述晶体管包括平面栅VDMOS。

较佳地,所述平面栅VDMOS包括平面型VDMOS或平面型Cool VDMOS(平面型VDMOS、平面型Cool VDMOS均为一种晶体管)。

本发明还提供一种晶体管,所述晶体管采用上述的晶体管的制作方法得到。

本发明的积极进步效果在于:

本发明中,利用一种或一种以上离子完成N区制作,其中形成N区离子中至少一种离子的扩散系数大于硼离子的扩散系数,利用其中至少一种离子(如磷)比硼离子扩得快的特点以补偿掉扩入沟道的硼离子;同时通过在Spacer(侧墙)底下具有扩散慢但稳定的As离子保证n+离子不会因磷扩散快而产生浓度梯度,从而在避免平面栅IGBT或VDMOS的阈值电压离散的同时,也避免了因n+区有浓度梯度而导致平面栅IGBT的Vcesat变大或VDMOS的Rdson变大的情况发生,使得平面栅IGBT的Vcesat和VDMOS的Rdson不变大,提高了平面栅IGBT以及VDMOS的使用性能。

附图说明

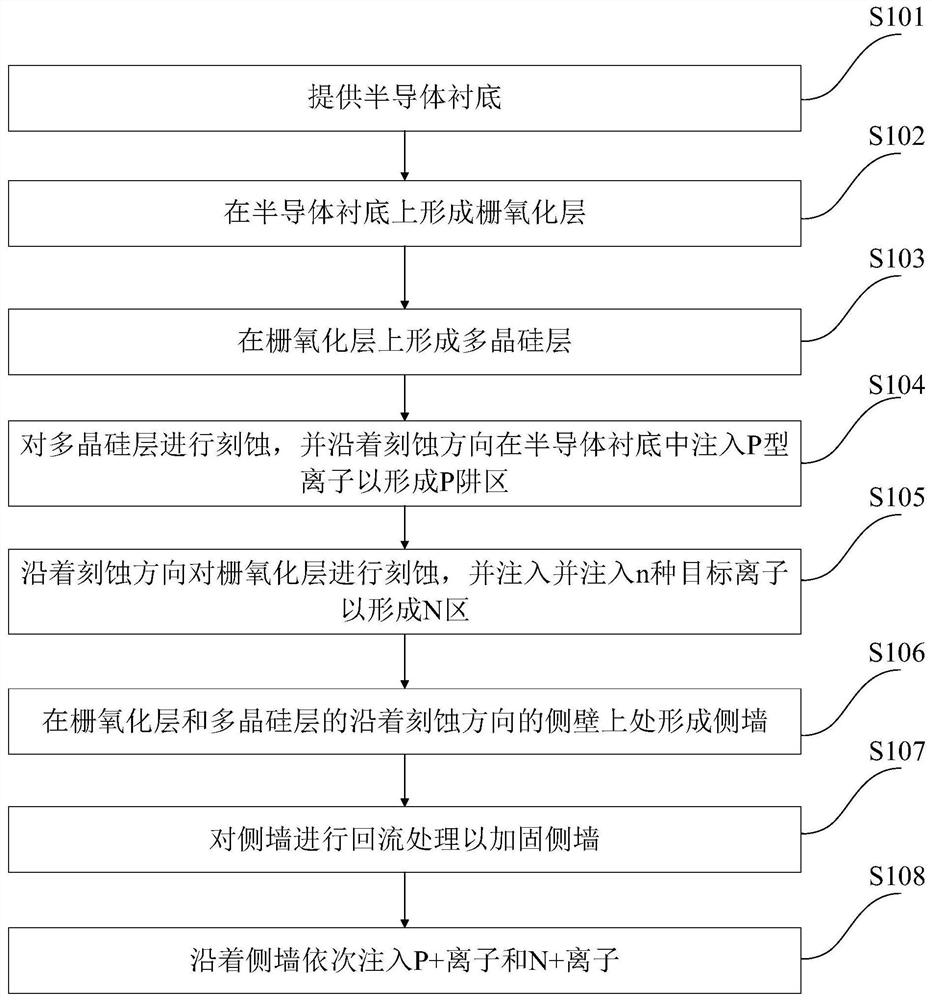

图1为本发明实施例1的晶体管的制作方法的流程图。

图2为本发明实施例1的晶体管的制作方法对应的第一结构示意图。

图3为本发明实施例1的晶体管的制作方法对应的第二结构示意图。

图4为本发明实施例1的晶体管的制作方法对应的第三结构示意图。

图5为本发明实施例1的晶体管的制作方法对应的第四结构示意图。

图6为本发明实施例1的晶体管的制作方法对应的第五结构示意图。

图7为本发明实施例1的晶体管的制作方法对应的第六结构示意图。

图8为本发明实施例1的晶体管的制作方法对应的第七结构示意图。

图9为本发明实施例1的晶体管的制作方法对应的第八结构示意图。

具体实施方式

下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

实施例1

本实施例的晶体管为平面栅IGBT,其中,平面栅IGBT包括但不限于平面型IGBT、平面型FS IGBT、平面型CS IGBT或平面型FS CS IGBT。

如图1所示,本实施例的晶体管的制作方法包括:

S101、提供半导体衬底(如图2所示中的A);

其中,该衬底A的材质的选择根据实际情况进行确定,属于本领域的成熟技术,因此此处就不再赘述。

S102、在半导体衬底上形成栅氧化层(如图3所示中的B);

S103、在栅氧化层上形成多晶硅层(如图4所示中的C);

S104、对多晶硅层进行刻蚀,并沿着刻蚀方向在半导体衬底中注入P型离子以形成P阱区(如图5所示中的D,箭头方向为刻蚀方向以及离子注入方向,下述类似);

S105、沿着刻蚀方向对栅氧化层进行刻蚀,并注入n种目标离子以形成N区(如图6所示中的E);n≥1且取整数;

其中,n种目标离子中的至少一种目标离子的扩散系数(例如P磷离子等其他施主离子)大于硼离子的扩散系数。

P阱区包饶在N区外部;

具体地,沿着刻蚀方向对栅氧化层进行刻蚀;

在刻蚀后,沿着刻蚀方向注入磷离子;

沿着刻蚀方向注入目标离子以形成N区。

S106、在栅氧化层和多晶硅层的沿着刻蚀方向的侧壁上处形成侧墙(如图7所示中的F);

S107、对侧墙进行reflow(回流处理)以加固侧墙。

S108、沿着侧墙依次注入P+离子和N+离子。

具体地,沿着侧墙向N区中注入P+离子以形成P+区(如图8所示中的G);

沿着侧墙向N区中注入N+离子以形成N+区(如图9所示中的H);

其中,N+离子为高浓度砷离子;

P+区穿透N区且未穿透P阱区,N+区未穿透N区。

当然,在上述步骤之后还要进行ILD(绝缘层工序)、CONTACT(开孔工序)、METAL(金属层工序)、PASSIVATION(钝化层工序)等相关工序以完成器件的制作,这些制作工序均属于本领域的成熟技术,因此此处就不再赘述。其中,值得一提的是在CONTACT层工序中,在SPACER之间要刻硅且刻穿N区(如图6中的E)。

本实施例中,利用一种或一种以上离子完成N区制作,其中形成N区离子中至少一种离子的扩散系数大于硼离子的扩散系数,利用其中至少一种离子(如磷)比硼离子扩得快的特点以补偿掉扩入沟道的硼离子;同时通过在Spacer底下具有扩散慢但稳定的As离子保证n+离子不会因磷扩散快而产生浓度梯度,从而在避免平面栅IGBT的阈值电压离散的同时,也避免了因n+区有浓度梯度而导致平面栅IGBT的Vcesat变大的情况发生,使得平面栅IGBT的Vcesat不变大,提高了平面栅IGBT的使用性能。

实施例2

本实施例的晶体管为平面栅IGBT,具体采用实施例1的晶体管的制作方法得到。

本实施例的晶体管采用上述制作工艺能够使得平面栅IGBT的Vcesat不发生变大的情况,增强了晶体管的使用性能,能够满足更高的使用需求。

实施例3

本实施例的晶体管为平面栅VDMOS时,平面栅VDMOS包括但不限于平面型VDMOS或平面型Cool VDMOS。

如图1所示,本实施例的晶体管的制作方法包括:

S101、提供半导体衬底(如图2所示中的A);

其中,该衬底A的材质的选择根据实际情况进行确定,属于本领域的成熟技术,因此此处就不再赘述。

S102、在半导体衬底上形成栅氧化层(如图3所示中的B);

S103、在栅氧化层上形成多晶硅层(如图4所示中的C);

S104、对多晶硅层进行刻蚀,并沿着刻蚀方向在半导体衬底中注入P型离子以形成P阱区(如图5所示中的D,箭头方向为刻蚀方向以及离子注入方向,下述类似);

S105、沿着刻蚀方向对栅氧化层进行刻蚀,并注入n种目标离子以形成N区(如图6所示中的E);n≥1且取整数;

其中,n种目标离子中的至少一种目标离子的扩散系数(例如P磷离子等其他施主离子)大于硼离子的扩散系数。

P阱区包饶在N区外部;

具体地,沿着刻蚀方向对栅氧化层进行刻蚀;

在刻蚀后,沿着刻蚀方向注入磷离子;

沿着刻蚀方向注入目标离子以形成N区。

S106、在栅氧化层和多晶硅层的沿着刻蚀方向的侧壁上处形成侧墙(如图7所示中的F);

S107、对侧墙进行reflow以加固侧墙。

S108、沿着侧墙依次注入P+离子和N+离子。

具体地,沿着侧墙向N区中注入P+离子以形成P+区(如图8所示中的G);

沿着侧墙向N区中注入N+离子以形成N+区(如图9所示中的H);

其中,N+离子为高浓度砷离子;

P+区穿透N区且未穿透P阱区,N+区未穿透N区。

当然,在上述步骤之后还要进行ILD、CONTACT、METAL、PASSIVATION等相关工序以完成器件的制作,这些制作工序均属于本领域的成熟技术,因此此处就不再赘述。其中,值得一提的是在CONTACT层工序中,在SPACER之间要刻硅且刻穿N区(如图6中的E)。

本实施例中,利用一种或一种以上离子完成N区制作,其中形成N区离子中至少一种离子的扩散系数大于硼离子的扩散系数,利用其中至少一种离子(如磷)比硼离子扩得快的特点以补偿掉扩入沟道的硼离子;同时通过在Spacer底下具有扩散慢但稳定的As离子保证n+离子不会因磷扩散快而产生浓度梯度,从而在避免平面栅VDMOS的阈值电压离散的同时,也避免了因n+区有浓度梯度而导致平面栅VDMOS的Rdson变大的情况发生,使得平面栅VDMOS的Rdson不变大,提高了VDMOS的使用性能。

实施例4

本实施例的晶体管为平面栅VDMOS,具体采用实施例3的晶体管的制作方法得到。

本实施例的晶体管采用上述制作工艺能够使得平面栅VDMOS的Rdson不发生变大的情况,增强了晶体管的使用性能,能够满足更高的使用需求。

虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

- 薄膜晶体管及制作方法和薄膜晶体管阵列基板及制作方法

- 薄膜晶体管及制作方法和薄膜晶体管阵列基板及制作方法