平板探测器及其制备方法、摄影设备

文献发布时间:2023-06-19 12:24:27

技术领域

本公开涉及成像技术领域,具体而言,涉及一种平板探测器及其制备方法、摄影设备。

背景技术

平板型数字化摄影(DR)技术,可以清晰的拍摄出病人体内多种器官,被广泛应用于医疗成像中。其中,X光平板探测器是平板型数字化摄影(DR)技术的关键组件之一。然而,当前平板探测器存在均一性差的问题,制约了成像效果的提升。

需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

发明内容

本公开的目的在于克服上述现有技术的不足,提供一种平板探测器及其制备方法、摄影设备,提高平板探测器的均一性。

根据本公开的一个方面,提供一种平板探测器,包括依次层叠设置的无机缓冲层、驱动层、检测层和闪烁层;所述检测层设置有感光元件;所述驱动层包括层叠设置的驱动电路层和图案限定层;

所述图案限定层具有容置凹槽,所述感光元件至少部分容置于所述容置凹槽中。

根据本公开的一种实施方式,所述容置凹槽贯穿所述图案限定层。

根据本公开的一种实施方式,所述感光元件包括依次层叠设置的第一电极、光敏半导体层和第二电极;

所述容置凹槽的深度,不小于所述光敏半导体层的厚度的一半。

根据本公开的一种实施方式,所述感光元件包括依次层叠设置的第一电极、光敏半导体层和第二电极;所述第一电极位于所述第二电极靠近所述无机缓冲层的一侧;

所述第二电极在所述无机缓冲层上的正投影,与所述容置凹槽在所述无机缓冲层上的正投影重合。

根据本公开的一种实施方式,所述图案限定层位于所述驱动电路层远离所述无机缓冲层的一侧;

所述感光元件包括依次层叠设置的第一电极、光敏半导体层和第二电极;所述第一电极位于所述第二电极靠近所述无机缓冲层的一侧;

所述光敏半导体层至少部分嵌入所述容置凹槽中。

根据本公开的一种实施方式,所述驱动电路层包括开关晶体管;

所述图案限定层位于所述开关晶体管的漏电极远离所述无机缓冲层的一侧,且所述容置凹槽贯穿所述图案限定层;所述容置凹槽在所述无机缓冲层上的正投影,位于所述开关晶体管的漏电极在所述无机缓冲层上的正投影内;

所述开关晶体管的漏电极作为所述感光元件的第一电极。

根据本公开的一种实施方式,所述图案限定层位于所述驱动电路层与所述无机缓冲层之间。

根据本公开的另一个方面,提供一种摄影设备,包括上述的平板探测器。

根据本公开的另一个方面,提供一种平板探测器的制备方法,包括:

形成无机缓冲层;

在所述无机缓冲层的一侧形成驱动层;所述驱动层包括层叠设置的驱动电路层和图案限定层;所述图案限定层具有容置凹槽;

在所述驱动层远离所述无机缓冲层的一侧形成检测层,所述检测层设置有感光元件;所述感光元件至少部分容置于所述容置凹槽中;

在所述检测层远离所述无机缓冲层的一侧形成闪烁层。

根据本公开的一种实施方式,在所述无机缓冲层的一侧形成驱动层包括:

形成图案限定材料层,所述图案限定材料层的材料为负光刻胶;

采用第一掩膜板对所述图案限定材料层进行图案化处理,以形成所述容置凹槽;

在所述驱动层远离所述无机缓冲层的一侧形成检测层包括:

形成依次层叠于所述驱动层的感光半导体材料层和第二电极材料层;

采用所述第一掩膜板,对所述第二电极材料层进行图案化操作,以形成第二电极;

采用所述第二电极作为掩膜,对所述感光半导体材料层进行图案化操作,以形成感光半导体层。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

附图说明

此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本公开的实施例,并与说明书一起用于解释本公开的原理。显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

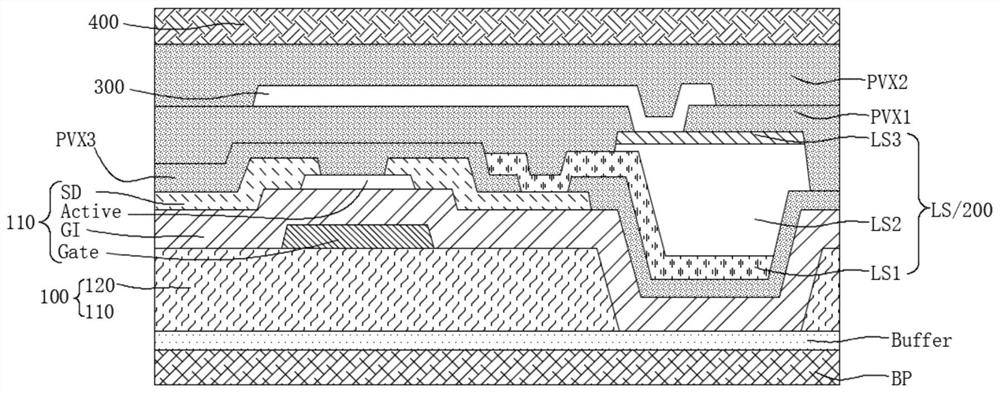

图1为相关技术中,一种平板探测器的结构示意图。

图2为本公开的一种实施方式中,一种平板探测器的结构示意图。

图3为本公开的一种实施方式中,图案限定层的结构示意图。

图4为本公开的一种实施方式中,一种平板探测器的结构示意图。

图5为本公开的一种实施方式中,图案限定层的结构示意图。

图6为本公开的一种实施方式中,平板探测器的制备方法的流程示意图。

附图标记说明:

BP、支撑背板;Buffer、无机缓冲层;100、驱动层;110、驱动电路层;120、图案限定层;A、容置凹槽;200、检测层;300、屏蔽金属层;400、闪烁层;LS、感光元件;LS1、第一电极;LS2、光敏半导体层;LS3、第二电极;Gate、栅极层;GI、栅极绝缘层;Active、半导体层;SD、源漏金属层;PVX1、第一钝化层;PVX2、第二钝化层;PVX3、第三钝化层;FBP、柔性衬底基板;ACR、有机平坦化层。

具体实施方式

现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的实施方式;相反,提供这些实施方式使得本公开将全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。图中相同的附图标记表示相同或类似的结构,因而将省略它们的详细描述。此外,附图仅为本公开的示意性图解,并非一定是按比例绘制。

在相关技术中,参见图1,柔性平板探测器可以包括依次层叠设置的柔性衬底基板FBP、驱动电路层110、检测层200、有机平坦化层ACR和闪烁层400。其中,检测层200中设置有与驱动电路层110电连接的感光元件LS,该感光元件LS可以为PIN元件。参见图1,感光元件LS包括层叠设置的第一电极LS1、光敏半导体层LS2和第二电极LS3。为了提高感光元件LS的检测效果,光敏半导体层LS2往往具有较大的厚度,例如具有约10000埃左右的厚度。在制备光敏半导体层LS2时,需要先沉积形成PIN半导体材料层,然后通过刻蚀工艺对PIN半导体材料层进行图案化操作,以形成感光元件LS所需的光敏半导体层LS2。然而,在图案化操作过程中,由于需要对PIN半导体材料层进行大深度的刻蚀,这导致刻蚀过程的均一性差,且光敏半导体层LS2的侧面具有较多毛刺等缺陷。这导致了平板探测器存在诸多不良,例如第三钝化层PVX3和第一电极LS1具有较大的损失量、平板探测器形成红绿色斑或者水波纹色斑等宏观不良。

本公开提供一种平板探测器及其制备方法。参见图2~图5,本公开提供的平板探测器包括依次层叠设置的无机缓冲层Buffer、驱动层100、检测层200和闪烁层400。检测层200设置有感光元件LS;驱动层100包括层叠设置的驱动电路层110和图案限定层120;图案限定层120具有容置凹槽A,感光元件LS至少部分容置于容置凹槽A中。

参见图2~图6,本公开提供的平板探测器,可以通过如下方法进行制备:

步骤S110,形成无机缓冲层Buffer;

步骤S120,在无机缓冲层Buffer的一侧形成驱动层100;驱动层100包括层叠设置的驱动电路层110和图案限定层120;图案限定层120具有容置凹槽A;

步骤S130,在驱动层100远离无机缓冲层Buffer的一侧形成检测层200,检测层200设置有感光元件LS;感光元件LS至少部分容置于容置凹槽A中;

步骤S140,在检测层200远离无机缓冲层Buffer的一侧形成闪烁层。

根据本公开提供的平板探测器及其制备方法,感光元件LS至少部分容置于容置凹槽A中,因此感光元件LS的至少部分侧壁容置于容置凹槽A中而无需通过刻蚀的方法来形成,因此该部分侧壁均一性良好且缺陷较少。因此,本公开的感光元件LS的侧壁具有更少的缺陷和更好的均一性,进而消除或者减弱通过刻蚀通过形成大厚度的感光元件LS时所导致的缺陷过多和刻蚀均一性差的缺陷,提高平板探测器的均一性。

下面,结合附图对本公开提供的平板探测器的结构、效果和制备方法做进一步地解释和说明。

参见图2和图4,本公开提供的平板探测器包括层叠设置的无机缓冲层Buffer、驱动层100、检测层200和闪烁层400。其中,驱动层100设置有开关晶体管,检测层200设置有感光元件LS;感光元件LS与开关晶体管电连接。本公开提供的平板探测器在工作时,闪烁层400可以将外部的X光转化为可见光,感光元件LS可以响应可见光而产生光生电荷;当开关晶体管导通时,可以将感光元件LS所产生的光生电荷传输出去,进而形成检测信号。如此,本公开提供的平板探测器可以检测X射线。

在一些实施方式中,如图2~图5所示,本公开的平板探测器可以预先制备于一支撑背板BP上,例如在支撑背板BP的一侧依次形成无机缓冲层Buffer、驱动层100、检测层200和闪烁层400,获得固定于支撑背板BP上的平板探测器。其中,该支撑背板BP可以为刚性背板,以便于平板探测器的制备。示例性地,该支撑背板可以为玻璃背板。

在获得固定于支撑背板BP上的平板探测器后,可以通过剥离支撑背板BP的方式,获得本公开的平板探测器。可选地,可以采用激光剥离的方法剥离支撑背板BP。这样本公开的平板探测器没有刚性的支撑背板BP,依次可以弯折,使得该平板探测器为柔性平板探测器。在获得本公开的平板探测器后,可以将该平板探测器应用于摄影设备中,使得该摄影设备能够对X射线成像。

可选地,无机缓冲层Buffer的材料可以为无机绝缘材料,例如可以为氧化硅、氮化硅、氮氧化硅或者其他无机绝缘材料,以利于将平板探测器从支撑背板BP剥离。在本公开的一种实施方式中,无机缓冲层Buffer的材料为氧化硅。

当然的,在本公开的其他一些实施方式中,平板探测器还可以包括柔性衬底基板,该柔性衬底基板可以设置于无机缓冲层Buffer远离驱动层100的一侧。在制备时,可以先在支撑背板BP上依次形成层叠的柔性衬底基板、无机缓冲层Buffer、驱动层100、检测层200和闪烁层400等,然后再剥离支撑背板BP。柔性衬底基板可以包括一层材料,也可以包括层叠的多层材料。举例而言,在本公开的一种实施方式中,柔性衬底基板可以包括一层聚酰亚胺(polyimide,PI)层。再举例而言,在本公开的一种实施方式中,柔性衬底基板可以包括依次层叠设置的底膜层(Bottom Film)、压敏胶层、第一聚酰亚胺层和第二聚酰亚胺层。

参见图2~图5,驱动层100可以包括层叠的图案限定层120和驱动电路层110。其中,驱动电路层110可以设置有驱动感光元件LS的开关晶体管,图案限定层120可以为绝缘材料且形成有容置凹槽A,容置凹槽A向远离无机缓冲层Buffer的方向开口。开关晶体管位于容置凹槽A以外,且感光元件LS至少部分容置于容置凹槽A内。如此,可以减少感光元件LS与驱动层100之间的段差,使得感光元件LS的侧面不完全由刻蚀获得,进而减小通过刻蚀所获得的侧面在整个侧面中的占比,以及减小通过刻蚀所获得的侧面的高度。这样,感光元件LS的侧面因刻蚀而产生的缺陷将大幅减少,进而可以提高感光元件LS自身的性能以及提高不同感光元件LS之间的均一性,进而提高平板探测器的均一性。

可选地,容置凹槽A的深度可以为5000~12000埃;进一步地,容置凹槽A的深度为9000~11000埃。

可选地,驱动电路层110还可以包括沿列方向延伸的多个检测线和沿行方向延伸的多个扫描线。开关晶体管的数量为多个且阵列分布,任意一个开关晶体管可以位于一个检测线与一个扫描线交汇处附近,以便与该扫描线和该检测线电连接。感光元件LS的数量为多个且阵列分布,各个感光元件LS可以与各个开关晶体管一一对应设置且电连接。进一步地,一个感光元件与对应的开光元件组成一个检测单元;本公开的平板探测器设置有阵列分布的多个检测单元。

示例性地,开关晶体管可以有源层、源电极、漏电极和栅极;其中,有源层可以包括沟道区和位于沟道区两侧的源电极接触区、漏电极接触区。栅极和沟道区之间通过栅极绝缘层GI隔离,源电极与源电极接触区连接,漏电极与漏电极接触区连接。其中,开关晶体管的源电极可以与检测线电连接,开关晶体管的栅极可以与扫描线电连接,开关晶体管的漏电极可以与感光元件LS电连接。如此,可以通过逐行扫描各个开关晶体管的方法,使得各个感光元件LS与外部电路连接。

在本公开的一种实施方式中,参见图2和图4,开关晶体管可以薄膜晶体管。该薄膜晶体管可以为顶栅型薄膜晶体管、底栅型薄膜晶体管或者双栅型薄膜晶体管;薄膜晶体管的有源层的材料可以为非晶硅半导体材料、低温多晶硅半导体材料、金属氧化物半导体材料、有机半导体材料或者其他类型的半导体材料;薄膜晶体管可以为N型薄膜晶体管或者P型薄膜晶体管。在本公开的一种实施方式中,薄膜晶体管为非晶硅晶体管或者金属氧化物晶体管。在本公开的另一种实施方式中,薄膜晶体管为底栅型薄膜晶体管。

在本公开的一些实施方式中,参见图2和图4,驱动电路层110可以包括依次层叠于无机缓冲层Buffer一侧的栅极层Gate、栅极绝缘层GI、半导体层Active和源漏金属层SD。其中,栅极层Gate可以形成扫描线和开关晶体管的栅极。半导体层Active形成有开关晶体管的有源层;源漏金属层SD可以形成有开关晶体管的源电极和漏电极。进一步地,开关晶体管的栅极可以作为扫描线的一部分。

可选地,平板探测器还设置有绑定区,源漏金属层SD在绑定区还可以形成平板探测器的绑定焊盘。

可以理解的是,平板探测器的驱动电路层110,还可以形成其他导电结构,例如在平板探测器的边缘区域形成周边走线等,本公开对此不做具体的限定。

可以理解的是,源漏金属层SD可以根据电阻和负载等情况,合理确定其厚度。当源漏金属层SD的方阻比较大、负载比较大时,可以考虑适当增大源漏金属层SD的厚度。

在本公开的一种实施方式中,参见图4,开关晶体管的漏电极可以复用为感光元件LS的第一电极LS1。

在一些实施方式中,参见图2和图3,驱动电路层110位于图案限定层120远离无机缓冲层Buffer的一侧。换言之,可以在无机缓冲层Buffer上先形成图案限定层120,然后再在图案限定层120远离无机缓冲层Buffer的一侧形成驱动电路层110。其中,驱动电路层110的开关晶体管等可以设置在容置凹槽A以外。当形成检测层200时,感光元件LS可以至少部分容置于该容置凹槽A内,以便减小感光元件LS与驱动电路层110之间的段差。

在一种示例性地实施例中,参见图2,平板探测器包括依次层叠于无机缓冲层Buffer一侧的图案限定层120、驱动电路层110和检测层200。其中,图案限定层120具有容置凹槽,容置凹槽贯穿图案限定层120以暴露部分无机缓冲层Buffer。驱动电路层110包括依次层叠设置的栅极层Gate、栅极绝缘层GI、半导体层Active和源漏金属层SD,以便在驱动电路层形成开关晶体管。其中,栅极层Gate、半导体层Active和源漏金属层SD所形成的图案均在容置凹槽以外,以避免这些膜层在容置凹槽内形成图案而减小容置凹槽的深度。换言之,驱动电路层中的走线(例如扫描线和检测线)和开关晶体管可以均位于容置凹槽以外。栅极绝缘层GI可以覆盖容置凹槽的底面和侧面,以避免对栅极绝缘层GI专门进行图案化处理而增加掩膜板数量和提高制备工序数量,降低平板探测器的制备成本。在驱动电路层110远离无机缓冲层Buffer一侧可以设置有第三钝化层PVX3,第三钝化层PVX3可以设置有暴露开关晶体管的漏电极的至少部分区域的过孔。其中,在容置凹槽内,既可以覆盖有第三钝化层PVX3,也可以不覆盖有第三钝化层PVX3。感光元件LS至少部分容置于容置凹槽内,其可以包括第一电极LS1。其中,第一电极LS1位于第三钝化层PVX3远离无机缓冲层Buffer的一侧,且通过过孔与开关晶体管的漏电极电连接。可选地,在一些实施方式中,平板探测器的一些绑定焊盘,可以与第一电极LS1同层设置。换言之,可以在第三钝化层PVX3远离无机缓冲层Buffer形成第一电极材料层,然后对第一电极材料层进行图案化处理,获得第一电极LS1和绑定焊盘。

在另一些实施方式中,参见图4和图5,驱动电路层110位于图案限定层120靠近无机缓冲层Buffer的一侧。换言之,可以在无机缓冲层Buffer上先形成驱动电路层110,然后再在图案限定层120远离无机缓冲层Buffer的一侧形成图案限定层120。其中,驱动电路层110的开关晶体管与容置凹槽A不交叠。当形成检测层200时,感光元件可以至少部分容置于该容置凹槽A内,以便减小感光元件与图案限定层120之间的段差。

可选的,容置凹槽A可以贯穿图案限定层120以呈孔状,也可以不贯穿图案限定层120以保持槽状,本公开不做具体的限定。可以根据容置凹槽A的深度和图案限定层120的厚度进行确定。参见图3和图5,在本公开的一种实施方式中,容置凹槽A可以贯穿图案限定层120,以便使得容置凹槽A的深度最大化,尽可能的减小感光元件LS与驱动层100之间的段差。

在本公开的一种具体示例中,参见4,图案限定层120位于驱动电路层110远离无机缓冲层Buffer的一侧,且容置凹槽A贯穿图案限定层120。如此,感光元件LS的第一电极LS1可以设置在图案限定层120靠近无机缓冲层Buffer的一侧,且至少部分被容置凹槽A所暴露;该第一电极LS1可以复用为开关晶体管的漏电极。换言之,感光元件LS的第一电极LS1和开关晶体管的漏电极为同一电极。在该具体示例中,可以无需在图案限定层120上开设使得第一电极LS1和开关晶体管的第二端连接的过孔,可以简化平板探测器的结构和制备工艺。

在本公开中,检测层200中设置有感光元件LS。在本公开的一种实施方式中,感光元件LS为PIN感光元件LS,其可以包括依次层叠设置的第一电极LS1、光敏半导体层LS2和第二电极LS3,第一电极LS1与开关晶体管连接。其中,光敏半导体层LS2可以为PIN半导体层。

可选地,光敏半导体层LS2的厚度可以为5000~15000埃,例如可以为9000~11000埃。如此,光敏半导体层LS2具有较大的厚度,可以提高对光线的灵敏度。

可选地,在本公开中,可以通过如下方法形成光敏半导体层LS2和第二电极LS3:

步骤S310,在第一电极LS1远离无机缓冲层Buffer的一侧,依次形成光敏半导体材料层和第二电极LS3材料层;

步骤S320,采用第一掩膜板对第二电极LS3材料层进行图案化操作,以形成第二电极LS3。

步骤S330,以第二电极LS3层作为掩膜(刻蚀阻挡层),对光敏半导体材料层进行图案化操作,以形成光敏半导体层LS2。

在一些实施方式中,在步骤S310中,可以依次形成P型掺杂的非晶硅层、本征非晶硅层和N型掺杂的非晶硅层;然后,再在N型掺杂的非晶硅层远离无机缓冲层Buffer的一侧形成第二电极LS3材料层。

可选地,三层非晶硅层的总厚度可以为10000埃左右。

可选地,第二电极LS3材料层的材料可以为透明导电材料,例如可以为透明导电金属氧化物。示例性地,在本公开的一种实施方式中,第二电极LS3材料层的材料为ITO(氧化铟锡)。

可以理解的是,还可以通过其他方法和半导体材料来形成光敏半导体材料层,以所形成的光敏半导体材料层能够响应可见光而生成光生电荷或者改变电阻为准。

在一些实施方式中,在步骤S120中,可以采用光刻工艺对第二电极LS3材料层进行图案化操作。具体的,可以在第二电极LS3材料层远离无机缓冲层Buffer的一侧形成光刻胶层,然后采用第一掩膜板对光刻胶层进行曝光;之后,通过显影,获得图案化的光刻胶层。该图案化的光刻胶层可以覆盖第二电极LS3材料层的至少部分区域,且暴露其他区域。然后,对第二电极LS3材料层进行刻蚀,去除第二电极LS3材料层未被图案化的光刻胶层覆盖的部分,可以获得第二电极LS3。可选地,在制备第二电极LS3时,使得所获得的第二电极LS3与容置凹槽A至少部分交叠,这可以使得光敏半导体层LS2至少部分嵌入容置凹槽A中。

可以理解的是,可以在获得第二电极LS3层后,直接去除图案化的光刻胶层,也可以在形成光敏半导体层LS2后,再去除图案化的光刻胶层。在本公开的一种实施方式中,可以在形成光敏半导体层LS2后,再去除图案化的光刻胶层。

在步骤S330中,可以通过对光敏半导体材料层进行刻蚀,进而获得光敏半导体层LS2。在相关技术中,由于光敏半导体材料层的厚度太大,因此对其刻蚀时,难以保证刻蚀的均一性,且所获得的光敏半导体层LS2的侧面具有大量损伤,这些损伤可以为形成的孔洞或者毛刺,均会对光敏半导体层LS2的性能产生不利影响。

而在本公开中,由于光敏半导体材料层的至少部分容置于容置凹槽A中,且该部分可以保留以作为光敏半导体层LS2的一部分,因此光敏半导体层LS2仅有部分侧壁是通过刻蚀工艺获得的,这降低了刻蚀工艺对光敏半导体层LS2的影响程度,进而能够减小光敏半导体层LS2的侧面的缺陷比例,提高光敏半导体层LS2的性能和不同光敏半导体层LS2之间的均一性。进一步地,光敏半导体层LS2至少部分嵌入容置凹槽A中。如此,光敏半导体层LS2的至少部分侧面,由容置凹槽A来限定而非通过刻蚀工艺形成。

可选地,容置凹槽A的深度,不小于光敏半导体层LS2的厚度的一半,以明显地减小感光元件LS与驱动层100之间的段差。进一步地,容置凹槽A的深度,可以为光敏半导体层LS2的厚度0.95~1.05倍,以使得感光元件LS的至少部分区域容置或者基本容置于容置凹槽A内。

可选地,在形成图案限定层120时,所采用的掩膜板与形成第二电极LS3时所采用的掩膜板相同。换言之,可以先形成图案限定材料层,然后采用第一掩膜板对图案限定材料层进行图案化操作,且图案限定材料层的材料为负性光刻胶。如此,第二电极LS3在无机缓冲层Buffer上的正投影,与容置凹槽A在无机缓冲层Buffer上的正投影重合。这样,制备第二电极LS3和图案限定层120时可以采用相同的掩膜板,能够减少平板探测器制备过程中所需的掩膜板的数量,进而降低平板探测器的制备成本。

在一实施方式中,参见图4,可以采用如下步骤S210~步骤S240所示的方法制备驱动层和检测层:

步骤S210,在无机缓冲层Buffer的一侧制备驱动电路层110,驱动电路层具有开关晶体管的漏电极,该漏电极可以复用为感光元件的第一电极。在步骤S210中,漏电极与第一电极为同一电极,相较于分别设置两个不同的电极的方案,可以减少一层电极以及减少一层隔离两个电极的绝缘层,因此在结构上减少两个膜层的厚度,在制备工序减少两个膜层的物料和两个掩膜板,能够显著地降低平板探测器的制备成本并提高生产效率。

步骤S220,在驱动电路层110远离无机缓冲层Buffer的一侧形成图案限定材料层,图案限定材料层的材料为负性光刻胶。近一步的,图案限定材料层的厚度为10000埃左右。

步骤S230,采用第一掩膜板,对图案限定材料层进行图案化处理,以便形成贯穿图案限定材料层的容置凹槽,获得图案限定层。其中,容置凹槽开设于用于设置感光元件的位置,其暴露第一电极的部分区域。进一步地,容置凹槽的底部在无机缓冲层Buffer上的正投影,完全位于第一电极在无机缓冲层Buffer上的正投影内。

可以理解的是,在平板探测器的边缘附近,例如平板探测器的周边区域、绑定区等,也可以去除图案限定材料层的光刻胶。

根据步骤S230的制备方法,图案限定层远离无机缓冲层Buffer的一侧没有设置金属膜层或者无机材料,例如没有设置走线、电极、钝化层等。

步骤S240,参照步骤S310的方法,在图案限定层远离无机缓冲层Buffer的一侧,通过沉积依次形成光敏半导体材料层和第二电极LS3材料层。然后,按照步骤S320和步骤S330的方法,形成第二电极LS3和光敏半导体层LS2。进一步地,光敏半导体层LS2的厚度为10000埃左右。

在步骤S240中,在对光敏半导体材料层进行刻蚀时,为了保证刻蚀充分以克服支撑背板不同位置处的刻蚀速率差异,可以进行过刻蚀。在过刻蚀过程中,刻蚀液直接接触图案限定层,而无法与源漏金属层、钝化层等进行接触,因此不会导致源漏金属层、钝化层在过刻蚀过程中产生损伤而加剧平板探测器的不均一性。

由此,在该实施例中,图案限定层不仅可以限定感光元件的位置并减少光敏半导体层LS2的侧面的损伤,而且可以避免过刻蚀导致的源漏技术处损伤和钝化层损伤。这样,可以同时提高感光元件的性能和平板探测器的均一性。尤其是,当图案限定层的厚度与光敏半导体层LS2的厚度基本一致时,例如均为10000埃左右时,光敏半导体层LS2可以恰好填充于容置凹槽内,其侧面基本通过容置凹槽的侧壁进行限定。

当然的,可以理解的是,在对图案限定材料层进行图案化处理时也可以采用其他掩膜板,例如采用与第一掩膜板不同的第二掩膜板,以能够形成所需的容置凹槽为准。

参见图2和图4,在本公开的一些实施方式中,平板探测器还可以设置有屏蔽金属层300,屏蔽金属层300可以设置于检测层200远离无机缓冲层Buffer的一侧。其中,屏蔽金属层300可以至少覆盖开关晶体管的沟道区,并暴露至少感光元件LS的至少部分区域。换言之,开关晶体管的沟道区在无机缓冲层Buffer上的正投影,完全位于屏蔽金属层300在无机缓冲层Buffer上的正投影内。如此,屏蔽金属层300既可以遮蔽照射至开关晶体管上光线,避免开关晶体管在光线照射向而改变其电学特性;还可以使得光线可以照射至感光元件LS。可选地,屏蔽金属层300还可以形成偏置引线,偏置引线与感光元件LS的第二电极LS3电连接,以便向感光元件LS加载偏置电压。

示例性地,参见图2和图4,平板探测器在检测层200远离无机缓冲层Buffer的一侧依次设置有第一钝化层PVX1和屏蔽金属层300,闪烁层400设置于屏蔽金属层300远离无机缓冲层Buffer的一侧。其中第一钝化层PVX1设置有暴露第二电极LS3的过孔;屏蔽金属层300覆盖各个开关晶体管的沟道区,且形成有偏置引线;偏置引线可以通过过孔与第二电极LS3连接,且延伸至与绑定区连接。

进一步地,屏蔽金属层300在绑定区设置有与各个绑定焊盘一一对应的转接绑定焊盘,第一钝化层PVX1设置有暴露各个绑定焊盘的过孔;转接绑定焊盘与绑定焊盘之间通过过孔一一对应的电连接。

参见图1,在相关技术中,由于感光元件LS与驱动电路层110之间存在较大的段差,因此需要在检测层200与第一钝化层PVX1之间设置有机平坦化层ACR。该有机平坦化层ACR具有较大的厚度且在远离无机缓冲层Buffer的一侧设置,其材料为树脂。然后,有机平坦化层ACR在制备时容易引发多种不良,例如裂纹(尤其是钝化层容易出现裂纹)、膜层脱落(尤其是金属膜层容易脱落)、气泡、坡度角形貌不利等。另外,有机平坦化层ACR与第一钝化层PVX1之间还容易出现粘接不良等问题。参见图2和图4,在本公开提供的平板探测器中,通过在图案限定层120上设置容置凹槽A,可以明显减小感光元件LS与驱动层100之间的段差,进而可以避免设置有机平坦化层ACR层。如此,可以克服设置有机平坦化层ACR所引起的多种不良,进而提高平板探测器的良率。不仅如此,本公开通过避免设置有机平坦化层ACR,还可以减少用于形成有机平坦化层ACR的掩膜板,进而减少平板探测器的制备中所需的掩膜板数量。

进一步地,由于感光元件LS与驱动层100之间的段差较小,因此第一钝化层PVX1无需具有较大的厚度。示例性地,第一钝化层PVX1的厚度可以在4500埃~6000埃之间。

参见图2和图4,在本公开的一种实施方式中,平板探测器还可以设置有依次层叠于屏蔽金属层300远离无机缓冲层Buffer一侧的第二钝化层PVX2和绑定层,闪烁层400设置于绑定层远离无机缓冲层Buffer的一侧。其中第二钝化层PVX2的可以形成有暴露各个转接绑定焊盘的连接过孔;绑定层可以形成与各个转接绑定焊盘一一对应的辅助焊盘,辅助焊盘通过连接过孔与对应的转接绑定焊盘连接。其中,辅助焊盘的材料为导电且与外部电路具有良好结合性能的材料,以提高平板探测器与外部电路之间的绑定强度。可选地,绑定层的材料可以为氧化铟锡。其中,外部电路可以为电路板、柔性电路板、覆晶薄膜或者其他能够与平板探测器绑定连接的电路结构。

可选地,在本公开的一种实施方式中,平板探测器还包括有机保护层,有机保护层位于绑定层远离无机缓冲层Buffer的一侧,用于为闪烁层400提供平坦化表面并保护平板探测器。进一步地,有机保护层的材料为树脂,其可以起到保护平板探测器的功能,例如起到防潮的作用。

可选地,闪烁层可以包括闪烁体。闪烁体能够吸收高能粒子或射线后发光,其可以制备呈晶体态。闪烁体的材料可以为碘化铯、钨酸镉、氟化钡、硫氧化钆(GOS)或者其他可行的材料。在本公开的一种实施方式中,闪烁层包括碘化铯。

本公开还提供一种摄影设备,该摄影设备包括上述平板探测器实施方式所描述的任意一种平板探测器。可选地,该平板探测器可以为一种医疗成像设备,例如可以为X光成像设备。在本公开的一种实施方式中,本公开的摄影设备还可以包括X光发生器、X光球管、准直器、图像处理系统灯。进一步地,本公开的摄像设备为一种移动式的摄影设备,其平板探测器可以在移动式应用场景下应用。

需要说明的是,尽管在附图中以特定顺序描述了本公开中平板探测器的制备方法的各个步骤,但是,这并非要求或者暗示必须按照该特定顺序来执行这些步骤,或是必须执行全部所示的步骤才能实现期望的结果。附加的或备选的,可以省略某些步骤,将多个步骤合并为一个步骤执行,以及/或者将一个步骤分解为多个步骤执行等。

本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其它实施方案。本申请旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原理并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的真正范围和精神由所附的权利要求指出。

- 平板探测器及其制备方法、摄影设备

- 平板探测器基板及其制备方法、平板探测器