伺服器及相关的控制方法

文献发布时间:2023-06-19 12:27:31

技术领域

本发明有关于存储器控制,尤指一种用以进行全快闪存储器阵列(All FlashArray,简称AFA)伺服器的数据存取管理的方法以及相关设备(apparatus)诸如AFA伺服器及其控制电路等。

背景技术

数据储存伺服器可以被设置为储存一个或多个用户的用户数据,并且在现有技术中已经提出了针对数据储存伺服器的各种控制方法,以便给用户带来良好的用户体验。由于非挥发性(Non-Volatile,NV)存储器诸如快闪存储器已经被广泛应用于各种数据储存装置诸如固态硬盘(solid state drive,SSD)等,现有技术中提出将数据储存伺服器用NV存储器作为其储存介质的非挥发性(NV)存储器类型数据储存伺服器来实现,例如其中安装有多个SSD的AFA伺服器。但是,可能会出现某些问题。例如,存取该多个SSD中的任一SSD的快闪存储器的管理会很复杂。为了确保这个SSD中的快闪存储器的存取控制符合相关规范,这个SSD中的快闪存储器的控制器通常配备有某些管理机制以妥善地管理其内部操作。虽然SSD制造商可能试着使SSD看起来像是替代硬式磁碟机(HDD)的不错的解决方案,但是SSD的某些特性与HDD完全不同。如此一来,上述控制方法对于安装有多个SSD的AFA伺服器可能变得不适合或无效,进而导致AFA伺服器的整体效能下降。因此,需要以在没有副作用或较不会带来副作用的情况下提供一种新颖的方法和相关的架构来解决这些问题。

发明内容

因此,本发明的目的之一在于提出一种伺服器的控制方法,以解决上述的问题。

在本发明的一实施例中,揭露了一种伺服器,其包含有一固态硬盘以及一节点,其中该节点包含了一通信模块、一处理器以及一存储器。该存储器包含了作为一写入缓冲器的一环形缓冲器,其中该写入缓冲器包含多个区段,每个区段的大小等于该电子装置的一写入单元;该写入缓冲器具有用于指示最后写入之区段的终点的一写入指标,且该写入缓冲器另具一刷新指标,其用来指示一区段的数据已准备好搬移至该固态硬盘;该处理器将每个区段设置为具有多个状态中的其一,该多个状态包含一空白状态、一合并状态、一需要刷新状态以及一刷新状态,其中针对任一区段,当该区段具有该空白状态表示该区段中没有储存任何数据,当该区段具有合并状态表示该处理器正在从该固态硬盘载入其他数据并将储存在该区段中的数据与从该固态硬盘载入的其他数据合并,当该区段具有需要刷新状态表示其数据已准备好被搬移至该固态硬盘,当该区段具有该刷新状态表示该处理器正在将该区段的数据搬移至该固态硬盘;以及该处理器另外参考该写入指标所指向之一特定区段的状态,以判断是否忽略该特定区段,并直接处理位于该特定区段之后的区段。

在本发明的另一实施例中,揭露了一种伺服器的控制方法,其中该伺服器包含了用来暂存来自一电子装置的一写入缓冲器,该写入缓冲器包含了多个区段,每一个区段的大小相同于该电子装置的一写入单位;该写入缓冲器具有用于指向最后写入之区段的终点的一写入指标,且该写入缓冲器另具一刷新指标,其用来指示一区段的数据已准备好搬移至一固态硬盘;以及该控制方法包含有:设置每一个区段具有多个状态中的其一,该多个状态包含一空白状态、一合并状态、一需要刷新状态以及一刷新状态,其中针对任一区段,当该区段具有该空白状态表示该区段中没有储存任何数据,当该区段具有合并状态表示正在从该固态硬盘载入其他数据并将储存在该区段中的数据与从该固态硬盘载入的其他数据合并,当该区段具有需要刷新状态表示其数据已准备好被搬移至该固态硬盘,当该区段具有该刷新状态表示正在将该区段的数据搬移至该固态硬盘;以及参考该写入指标所指向之一特定区段的状态,以判断是否忽略该特定区段,并直接处理位于该特定区段之后的区段。

在本发明的另一实施例中,揭露了一种伺服器的控制方法,其中该伺服器包含了用来暂存来自一电子装置的一写入缓冲器,该写入缓冲器包含了多个区段,每一个区段的大小相同于该电子装置的一写入单位;该写入缓冲器具有用于指向最后写入之区段的终点的一写入指标,且该写入缓冲器另具一刷新指标,其用来指示一区段的数据已准备好搬移至一固态硬盘;以及该控制方法包含有:自一电子装置接收数据;判断该写入指标所指向的一区段是否具有一空白状态;若是该写入指标所指向的该区段具有该空白状态,将该数据写入至该区段;若是该写入指标所指向的该区段不具有该空白状态,判断该写入指标所指向的该区段是否具有一合并状态;若是该写入指标所指向的该区段具有该合并状态,在该区段改变为其他状态前都不将该数据写入至该写入缓冲器中;若是该写入指标所指向的该区段不具有该合并状态,判断该写入指标与该刷新指标之间是否有任何区段具有该空白状态;以及若是该写入指标与该刷新指标之间是否有任一区段具有该空白状态,则将该数据写入至该写入指标与该刷新指标之间具有该空白状态的区段。

附图说明

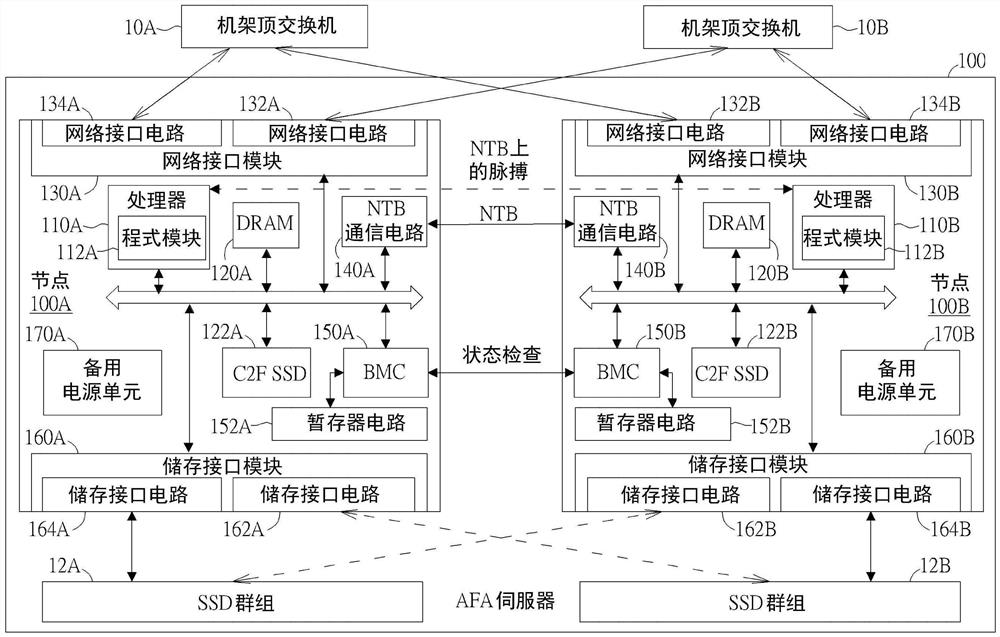

图1是依据本发明一实施例的一全快闪存储器阵列(All Flash Array,简称AFA)伺服器的示意图。

图2是依据本发明一实施例中如图1所示的该AFA伺服器的某些实施细节的示意图。

图3是依据本发明一实施例所绘示的如图1所示的该AFA伺服器的一双节点架构的示意图。

图4是依据本发明一实施例所绘示的如图1所示的多个节点的任一节点中的某些程式模块的示意图。

图5为根据本发明一个实施例之写入缓冲器的示意图。

图6是根据本发明的一个实施例之状态机的示意图。

图7为根据本发明一实施例之刷新指标的移动示意图。

图8为根据本发明一实施例之写入指标的移动示意图。

图9为根据本发明的一实施例之写入缓冲器的控制机制的流程图。

【符号说明】

10A,10B:机架顶(TOR)交换机

12A,12B:固态硬盘(SSD)群组

100:全快闪存储器阵列(AFA)伺服器

100A,100B:节点

110A,110B:处理器

112A,112B:程式模块

120A,120B:动态随机存取存储器(DRAM)

122A,122B:复制到快闪存储器(C2F)固态硬盘(SSD)

130A,130B:网络接口(IF)模块

132A,132B,134A,134B:网络接口(IF)电路

140A,140B:非透明网桥(NTB)通信电路

150A,150B:主机板管理控制器(BMC)

152A,152B:暂存器电路

160A,160B:储存接口(IF)模块

162A,162B,164A,164B:储存接口(IF)电路

170A,170B:备用电源单元

500:写入缓冲器

900~912:步骤

具体实施方式

图1是依据本发明一实施例的一全快闪存储器阵列(All Flash Array,简称AFA)伺服器100的示意图。AFA伺服器100可以包含多个节点,诸如二节点,分别为节点100A和节点100B,其中该多个节点中的任一个(例如节点100A和节点100B的其中一个)可以具有与该多个节点中的另一个(例如节点100A和节点100B中的另一个)相同或相似的架构。例如,节点100A可包含可以被统称为处理器110A的至少一处理器(例如,一个或多个处理器诸如一个或多个中央处理单元(Central Processing Units.CPU)),并包含一动态随机存取存储器(Dynamic Random Access Memory,DRAM)120A、一复制到快闪存储器(Copy-to-Flash,简称C2F)固态硬盘(Solid State Drive,简称SSD)122A、包含有一个或多个网络接口(interface,IF)电路诸如网络接口电路132A和134A(分别标示为“网络IF CKT”以求简明)的一网络接口(IF)模块130A、一非透明网桥(Non-Transparent Bridge,简称NTB)模块(或NTB)诸如一NTB通信电路140A(标示为“NTB CKT”以求简明)、一主机板管理控制器(BoardManagement Controller,简称BMC)150A、一暂存器(register)电路152A(标示为“REG CKT”以求简明)其耦接至BMC 150A、一储存接口(IF)模块160A其包含一个或多个储存接口电路诸如储存接口电路162A和164A(分别标示为“储存IF CKT”以求简明)以及一备用电源诸如一备用电源单元170A(例如,电池),其中这些组件的至少一部分(例如,一部分或全部)可以藉由节点100A的总线彼此耦接,但本发明不限于此。依据某些实施例,节点100A的架构可以作不同变化。

相似地,节点100B可包含可以统称为处理器110B的至少一处理器(例如,一个或多个处理器诸如一个或多个CPU),并包含一DRAM 120B、一C2F SSD 122B、包含有一个或多个网络接口(IF)电路诸如网络接口电路132B和134B(分别标示为“Network IF CKT”以求简明)的一网络接口(IF)模块130B、一NTB模块(或NTB)诸如一NTB通信电路140B标示为“NTBCKT”以求简明)、一BMC 150B、一暂存器电路152B(标示为“Register CKT”以求简明)其耦接至BMC 150B、一储存接口(IF)模块160B其包含一个或多个储存接口电路诸如储存接口电路162B和164B(分别标示为“Storage IF CKT”以求简明)以及一备用电源诸如一备用电源单元170B(例如,电池),其中这些组件的至少一部分(例如,一部分或全部)可以藉由节点100B的总线彼此耦接,但本发明不限于此。依据某些实施例,节点100B的架构可以作不同变化。

如图1所示,AFA伺服器100可以更包含耦接到节点100A和100B的多个SSD,诸如一SSD群组12A和一SSD群组12B,SSD群组12A和12B可以耦接到节点100A和100B,且可以预设分别连接/连线(link)到节点100A和100B,其中节点100A和100B与SSD群组12B和12A之间的虚线可指出多个可选的(optional)连线。举例来说,节点100A可以利用储存接口模块160A以启动储存接口电路164A和SSD群组12A之间的连线,以存取SSD群组12A中的数据,且节点100B可以利用储存接口模块160B启动储存接口电路164B和SSD群组12B之间的连线,以进一步存取SSD群组12B中的数据。当需要时,节点100A和100B与SSD群组12A和12B之间的连线关系可以改变。例如节点100A可以利用储存接口模块160A来启动储存接口电路162A和SSD群组12B之间的连线,以存取SSD群组12B中的数据,且节点100B可以利用储存接口模块160B来启动储存接口电路162B和SSD群组12A之间的连线,以存取SSD群组12A中的数据。

运行着程式模块112A的处理器110A可用以控制节点100A的操作。DRAM 120A可用以缓冲数据(例如待写入SSD群组12A的数据),并且C2F SSD 122A可用以将DRAM 120A中的缓冲后数据(简称“缓冲数据”)复制到C2F SSD 122A中的快闪存储器中,以在需要时防止缓冲数据的数据遗失(data loss)。举例来说,C2F SSD 122A可以藉由安装在节点100A内的主电路板(例如主机板或母板)上的一扩充卡诸如一M.2模块(例如具有符合M.2规范的连接器的电路板)来实现,其中C2F SSD 122A可以包含一储存控制器、一个或多个快闪存储器晶片等,但本发明不限于此。另外,包含有网络接口电路132A和134A的网络接口模块130A可用以将节点100A(例如该主电路板上的处理器110A、DRAM 120A等)藉由至少一网络交换机诸如机架顶(top-of-rack,可简称TOR)交换机10A和10B耦接到至少一网络(例如区域网络(Local Area Network,LAN)、广域网络(Wide Area Network,WAN)、互联网(Internet)等)。另外,包含储存接口电路162A和164A的储存接口模块160A可用以将节点100A(例如该主电路板上的处理器110A、DRAM 120A等)耦接到多个快闪储存装置(例如节点100A和100B共享的SSD群组12A和12B),用以存取(例如读取或写入)该多个快闪储存装置中的数据。如此一来,AFA伺服器100可用以藉由节点100A提供用户储存服务。

相似地,运行着程式模块112B的处理器110B可用以控制节点100B的操作。DRAM120B可用以缓冲数据(例如待写入SSD群组12B的数据),并且C2F SSD 122B可用以将DRAM120B中的缓冲后数据(简称“缓冲数据”)复制到C2F SSD 122B中的快闪存储器中,以在需要时防止缓冲数据的数据遗失。举例来说,C2F SSD 122B可以藉由安装在节点100B内的主电路板(例如主机板或母板)上的一扩充卡诸如一M.2模块(例如具有符合M.2规范的连接器的电路板)来实现,其中C2F SSD 122B可以包含一储存控制器、一个或多个快闪存储器晶片等,但本发明不限于此。另外,包含有网络电路132B和134B的网络接口模块130B可用以将节点100B(例如该主电路板上的处理器110B、DRAM 120B等)藉由至少一网络交换机诸如TOR交换机10A和10B耦接到至少一网络(例如LAN、WAN、互联网等)。另外,包含储存接口电路162B和164B的储存接口模块160B可用以将节点100B(例如该主电路板上的处理器110B、DRAM120B等)耦接到多个快闪储存装置(例如节点100A和100B共享的SSD群组12A和12B),用以存取(例如读取或写入)该多个快闪储存装置中的数据。如此一来,AFA伺服器100可用以藉由节点100B提供用户储存服务。

关于节点100A及其对等(peer)节点(例如节点100B)之间的通信,该NTB模块(例如NTB通信电路140A)可用以藉由在节点100A和100B之间的一NTB路径(标示为“NTB”以求简明)与对应的NTB模块(例如NTB通信电路140B)通信,使节点100A和100B的数据和储存状态同步,并进一步使它们相同。相似地,关于节点100B及其对等节点(例如节点100A)之间的通信,该NTB模块(例如NTB通信电路140B)可用以藉由在节点100A和100B之间的该NTB路径(标示为“NTB”以求简明)与对应的NTB模块(例如NTB通信电路140A)通信,使节点100A和100B的数据和储存状态同步,并进一步使它们相同。尤其,诸如NTB通信电路140A和140B的NTB模块可以提供节点100A和100B之间一传输桥的功能以及分离节点100A和100B的各自的地址域以使节点100A和100B分别有彼此独立的地址域,以在没有任何地址冲突的情况下提供/加强节点100A和100B之间的通信。例如,节点100A和100B的各个总线可以符合快捷外设组件互联(Peripheral Component Interconnect Express,PCIe)标准,并且节点100A和100B中的每一节点的NTB模块可以被认为是该节点的一端点(endpoint),其中节点100A和100B可以透过该传输桥彼此通信和共享装置,但本发明不限于此。依据某些实施例,诸如NTB通信电路140A和140B的NTB模块可以透过客制化的网络接口电路来实现,以控制节点100A和100B彼此通信,使得它们就像正在透过网络接口电路进行通信一样。

在运行着程式模块112A的处理器110A和运行着程式模块112B的处理器110B的控制下,节点100A和100B可维持和监视NTB上的脉搏,以确定对等节点的可用性,以进行高可用性(High Availability,HA)控制。举例来说,节点100B可用以向节点100A发送脉搏信号,且节点100A可用以检测并监视来自节点100B的脉搏信号以确定节点100B的可用性,其中来自节点100B的脉搏信号是否存在可以指出节点100B是否可用(或健康程度)。对于另一个例子来说,节点100A可用以向节点100B发送脉搏信号,并且节点100B可用以检测并监视来自节点100A的脉搏信号以确定节点100A的可用性,其中来自节点100A的脉搏信号是否存在可以指出节点100A是否可用(或健康程度)。依据图1所示的架构,如图1所示,当节点100A和100B其中一个不可使用时,节点100A和100B其中的另一个可以继续为用户提供AFA伺服器100的储存服务。

需注意的是,AFA伺服器100配备了超过一个的节点间(inter-node)通信路径(例如节点之间的超过一个的相互通信路径)。除NTB路径外,AFA伺服器100还可配置为具有一个或多个其他通信路径,例如BMC 150A和150B之间的一BMC路径,其中BMC 150A可用以管理节点100A的硬体层的至少一部分(例如一部分或全部),而BMC 150B可用以管理节点100B的硬体层的至少一部分(例如一部分或全部)。关于节点100A及其对等节点(例如节点100B)之间的通信,BMC 150A可用以透过该BMC路径与BMC 150B通信以存取(例如读取或写入)暂存器电路152B中的一个或多个暂存器的一个或多个暂存器值,以在节点100B上进行状态检查操作等。相似地,关于节点100B及其对等节点(例如节点100A)之间的通信,BMC 150B可用以透过该BMC路径与BMC 150A通信以存取(例如读取或写入)暂存器电路152A中一个或多个暂存器的一个或多个暂存器值,以在节点100A上进行状态检查操作等。尤其,BMC 150A与BMC150B可独立地管理节点100A与100B的各自的硬体层,而不需要仰赖处理器110A与110B。举例来说,当处理器110A发生故障时,BMC 150A可以处理节点100A的未完成的工作,而当处理器110B发生故障时,BMC 150B可以处理节点100B的未完成的工作,但本发明不限于此。依据某些实施例,BMC 150A和150B可用以分别接管(take over)节点100A和100B,以进行紧急处理操作来减少数据遗失的机率。

依据本实施例,AFA伺服器100可以被配置为由多种类型的电源供电。节点100A和100B的每一节点可以包括至少一主电源(例如至少一电源供应器),用以于主电源处于正常电源状况下提供电力给该节点的其他组件。举例来说,节点100A的主电源可以供电给节点100A的主电路板,并且节点100B的主电源可以供电给节点100B的主电路板。当检测到一个或多个节点(例如节点100A及/或节点100B)的异常电源状况时,AFA伺服器100中的一个或多个相关的备用电源(例如备用电源单元170A及/或备用电源单元170B)可用以提供备用电力。举例来说,当节点100A的主电源发生电源故障时,备用电源单元170A可以供电给节点100A的主电路板(例如处理器110A、DRAM 120A、C2F SSD 122A、NTB通信电路140A、BMC150A、暂存器电路152A等),当节点100B的主电源发生电源故障时,备用电源单元170B可以供电给节点100B的主电路板(例如处理器110B、DRAM 120B、C2F SSD 122B、NTB通信电路140B、BMC150B、暂存器电路152B等)。

依据某些实施例,节点100A和100B的每一节点(例如节点100A和100B的各自的主电路板中的每一节点)可以更包含多个感测器(sensor)/检测器(detector)用以至少对该节点的组件进行检测以产生检测结果(例如从这些传感器/检测器中的任一个所获得的状态信息)。举例来说,这些检测结果中的一功率检测结果可以表示该节点的主电源的功率状态,尤其,可以指出该节点是否发生异常电源状况,以供触发该节点启动备用电源(例如备用电源单元170A或备用电源单元170B)以提供备用电力。

图2依据本发明一实施例绘示图1所示的AFA伺服器100的某些实施细节,其中,可以将SSD 100S作为图1所示实施例中提到的多个SSD的例子。除了节点100A和100B以及SSD100S,AFA伺服器100可还包含一背板(backplane)电路100R。背板电路100R可用以将诸如SSD群组12A和12B的SSD 100S电气连接到节点100A和100B。举例来说,背板电路100R可以藉由具有相关连接器等的背板电路板来实现。另外,可以在背板电路100R内实现NTB通信电路140A和140B之间的该NTB路径的局部(partial)路径,以及BMC 150A和150B之间的该BMC路径的局部路径。由于该BMC路径和该NTB路径中的每一路径都不通过可能易于损坏的任何电缆,所以节点100A和100B之间的通信路径很稳健,且因此节点100A和100B可以保持有效的通信以及相关的控制,以确保AFA伺服器100的整体效能及正常运行。

依据某些实施例,SSD 100S中的每一SSD可以是一单埠(single port)SSD,尤其,可以是一单埠的基于装置的(device-based)SSD。另外,藉助于背板电路100R,AFA伺服器100可以支援SSD 100S中的每一SSD的热插拔。

依据某些实施例,两个节点100A和100B中的一个可以在AFA伺服器100的高可用性(High Availability简称HA)架构中用来作为一现用节点(active node),也就是扮演该现用节点的角色,并且两个节点100A和100B中的另一个可在AFA伺服器100的该HA架构中用来作为一待命节点(standby node),也就是扮演该待命节点的角色。诸如现用节点和待命节点的两个节点100A和100B可以彼此互动,尤其,可以藉由至少两条通信路径(诸如NTB通信电路140A和140B之间的NTB路径以及BMC 150A和150B之间的BMC路径)来交换节点信息,并且可以藉由NTB路径来同步数据,但本发明不限于此。依据某些实施例,AFA伺服器100可以配备有超过两个的节点间(inter-node)通信路径(例如节点之间的超过两个的相互通信路径)。

图3是依据本发明一实施例所绘示的如图所示的AFA伺服器100的一双节点架构的示意图。依据本实施例,节点100A和100B可以被分别配置为该现用节点和该待命节点,但本发明不限于此。举例来说,节点100A和100B可以在需要时交换它们所扮演的角色。如图3所示,除了某些硬体(hardware,HW)组件诸如图1或图2所示的架构中的部分组件外,还可绘示某些软件(software,SW)程式/程序,例如HA框架程式、网络(Web)伺服器程式、数据库(database)程式、操作于一服务模式的储存控制模块程式以及操作于一待机模式的储存控制模块程式(分别标示为“HA框架”、“Web伺服器”、“数据库”、“于服务模式下的储存控制模块”以及“于待机模式下的储存控制模块”以求简明)以指出AFA伺服器100中的关联互动,其中,上述程式的名称分别代表其相关功能。

运行于节点100A上的软件程式(例如,HA框架程式,Web伺服器程式,数据库程式和操作于该服务模式的储存控制模块程式)可作为程式模块112A的例子,并且运行于节点100B上的软件程式(例如,HA框架程式,Web伺服器程式,数据库程式和操作于该待机模式的储存控制模块程式)可作为程式模块112B的例子,但本发明不限于此。另外,网络接口模块130A的该一个或多个网络接口电路可更包含网络接口电路136A,并且网络接口模块130B的该一个或多个网络接口电路可还包含网络接口电路136B。因此,AFA伺服器100可以配备有至少三个节点间(inter-node)通信路径(例如节点之间的至少三个相互通信路径),诸如NTB路径、BMC路径以及网络接口电路136A和136B之间的网络路径。举例来说,节点100A和100B可用以藉由NTB路径进行快取镜像(cache mirroring)操作,并透过BMC路径检查本地/远端控制器状态,以及藉由网络接口电路136A和136B之间的网络路径进行额外的通信操作。

图4是依据本发明一实施例所绘示的如图1所示的多个节点100A与100B的任一(例如每一)节点中的程式模块112的示意图。例如,程式模块112可以代表运行在节点100A的处理器110A上的程式模块112A或运行在节点100B的处理器110B上的程式模块112B。如图4所示,程式模块112可以包含某些主程式模块,例如储存协定及区块输入/输出(IO)接口模块、储存快取模块、储存池模块、储存服务连续HA模块、储存功能模块以及储存管理模块(分别标示为“储存协定及区块IO接口”、“储存快取”、“储存池”、“储存服务连续HA”、“储存功能”以及“储存管理”以求简明),其中这些主程式模块中的任一程式模块可以包括一个或多个子模块。另外,程式模块112中的某些程式模块之间的箭头指出这些程式模块可以彼此在各自所属的多个层的程式模块之间互动。举例来说,储存协定及区块IO接口模块可以被视为储存快取模块上方的一上层(例如一上层程式模块),储存池模块可以被视为储存快取模块下方一下层(例如一下层程式模块),储存功能模块和储存快取模块可被安排在一中间层以作为中间层程式模块,其中储存协定及区块IO接口模块以及储存池模块可用以与客户端装置和SSD群组互动,但本发明不限于此。当需要时,该节点可以触发其他程式模块与这些程式模块中的一个或多个进行互动。

储存协定及区块IO接口模块可以包含某些子模块诸如小型计算机系统接口(Small Computer System Interface,简称SCSI)模块、互联网SCSI(Internet SCSI,简称iSCSI)模块和区块装置(Block Device)模块(分别标示为“SCSI”、“iSCSI”和“区块装置”以求简明)。储存快取模块可以包含某些子模块诸如使用软件实现的永久存储器(PersistentMemory using SW implementation)模块和写入缓冲模块(Write Buffer module;也可称为“写入缓冲器模块”),于图中分别标示为“永久存储器(软件实现)”和“写入缓冲”以求简明。储存池模块可以包含一子模块诸如快闪存储器阵列(Flash Array)模块(为简便起见标示为“快闪存储器阵列”)。储存服务连续HA模块可以包含一子模块诸如HA框架模块(标示为“HA框架”以求简明)。储存功能模块可以包含某些子模块诸如卷管理器(Volume Manager)模块和数据减少模块(分别标示为“卷管理器”和“数据减少”以求简明),其中数据减少模块可以包含某些子模块诸如压缩引擎(Compression Engine)模块和重复数据删除引擎(Deduplication Engine)模块,可以分别称为“压缩引擎”和“重复数据删除引擎”。储存管理模块可以包含某些子模块诸如网络(Web)用户界面(User Interface,UI)模块、应用程式编程接口(Application Programming Interface,API)伺服器模块、请求代理(RequestBroker)模块和数据库模块(分别标示为“网络UI”、“API伺服器”、“请求代理”和“数据库”以求简明)。上列模块的名称分别指出其相关功能。为了便于理解,对某一模块诸如卷管理器模块、压缩引擎模块、重复数据删除引擎模块等而言,某些实施例中所提到的咨询(consult)该模块的操作可包含对这个模块进行呼叫、查询等操作以从它取得对应的处理结果,但本发明不限于此。

依据某些实施例,AFA伺服器100(例如,该现用节点,诸如节点100A和100B的其中之一)可用以从AFA伺服器100外部的客户端装置接收请求诸如写入请求、读取请求等,并分别因应这些请求来操作。

对于来自AFA伺服器100外部的客户端装置的写入请求,处理器110A可以在DRAM120A内分配写入缓冲区,其用来暂时储存来自客户端装置的数据。图5为根据本发明一个实施例之写入缓冲器500的示意图。如图5所示,写入缓冲器500包含N个区段(sector),其中写入缓冲器500为一环形缓冲器(ring buffer),其第N个区段连接到第一区段,亦即写入缓冲器500没有实际上的终点。写入缓冲器500具有写入指标,用于指示最后写入之区段的终点或是空白区段的起始点。具体来说,写入缓冲器500经由TOR交换机10A/10B以依序地储存来自客户端装置的数据,而假设目前写入指标指示第五区段的终点,则若是第六区段为空白区段,处理器110A可以将数据写入至第六区段。在处理器110A将数据写入至第六区段之后,写入指标移动到第六区段的终点。需注意的是,如果写入缓冲器内的所有区段都是空白的,则写入指标仅用于指示空白区段的起始点(亦即,用来储存下一笔数据的区段);如果写入缓冲区中的所有区段都写入了数据,则写入指标仅用于指示最后写入之区段的终点。另外,写入缓冲器500另包含了刷新(flush)指标,该刷新指标指示其区段内的数据已经准备好被搬移至SSD100S。举例来说,如果刷新指标指示第八区段并且在第八区段中储存了数据,则表示处理器110A可以在适当的时间将储存在第八区段中的数据移动到SSD 100S中。在第八区段的数据移动到SSD 100S之后,刷新指标移动到第九区段。需注意,刷新指标系逐步移动(step by step)。

在本实施例中,写入缓冲器500之每个区段的大小等于写入单位,例如每个区段的大小可以是4kB。另外,储存在相同区段中的数据系对应到客户端装置的同一个逻辑地址,亦即,储存在同一个区段中的数据仅会对应到一个逻辑地址。

传统上写入指标与刷新指标系逐步移动,而本发明之实施例提供了一种写入机制,以改善数据写入的效率。

在本实施例中,每个区段被分配为具有多个状态中的其一。图6是根据本发明的一个实施例之状态机的示意图。如图6所示,一区段可以具有空白状态(empty state),分配状态(allocation state),部分状态(partial state),合并状态(merging state),需要刷新状态(need-flush state),刷新状态(flush state),覆写状态(overwritten state)和刷新结束状态(flush-done state)。空白状态指示该区段中没有储存任何数据,亦即,该区段允许储存来自客户端装置的数据。分配状态指示该区段正在储存来自客户端装置的数据。部分状态指示储存在区段中的有效数据小于写入单位(例如4KB),具体来说,假设节点100A从客户端装置接收到512位元的数据,则处理器110A参考写入指标以将512位元的数据和虚拟数据(dummy data)写入到区段中,而此时该区段便具有部分状态。合并状态指示储存在区段中的数据与从SSD 100S所载入的数据进行组合,具体来说,假设节点100A从客户端装置接收到512位元的数据,并且区段正在从客户端装置储存512位元的数据,则处理器110A检查SSD 100S中是否有数据的逻辑地址相同于从客户端装置所接收的512位元数据的逻辑地址。如果SSD 100S具有逻辑地址与客户端装置的512位元数据的逻辑地址相同的数据,则处理器110A从SSD 100S载入此数据,并且处理器110A进一步地将所载入的数据写入至具有上述512位元数据的区段,亦即,来自客户端装置的数据和从SSD100S所载入的数据被合并并储存在一个区段中。如果客户端装置的512位元数据的逻辑地址未出现在SSD 100S中,则该区段直接进入需要刷新状态。需要刷新状态指示可以将储存在区段中的数据移动到SSD100S。刷新状态指示处理器110A正在将数据从区段搬移至SSD 100S。覆写状态指示在将数据写入SSD 100S的过程中,节点100A刚从客户端接收更新后的数据,其中更新后的数据的逻辑地址与正在写入至SSD 100S的数据的逻辑地址相同。刷新结束状态指示该区段的刷新操作已经完成。

透过将区段设计为具有前述状态,处理器100A可以参考区段的状态以决定写入指标的移动,以使用写入缓冲器来有效率地存取SSD 100S。

图7为根据本发明一实施例之刷新指标的移动示意图。如图7所示,第k个区段、第(k+1)个区段、第(k+2)个区段具有需要刷新状态,并且刷新指标位于第k个区段的起始点。接着,处理器110A将第k个区段和第(k+1)个区段的数据依序移动到SSD,并且将第k个区段和第(k+1)个区段更改为刷新状态。需注意的是,第k个区段的数据和第(k+1)个区段的数据可以储存到不同的SSD中,因此数据写入的速度可以不同,故第(k+1)个区段可以比第k个区段更早进入刷新结束状态。

图8为根据本发明一实施例之写入指标的移动示意图。如图8所示,第m个区段、第(m+1)个区段、第(m+2)个区段具有刷新状态,且写入指标位于第m个区段的起始点。接着,如果第(m+1)个区段的数据和第(m+2)个区段的数据已经完全移动到SSD 100S,且第(m+1)个区段和第(m+2)个区段已经改变为空白状态,但是第m个区段仍然处于刷新状态,则写入指标可以忽略具有刷新状态的第m个区段而直接移动到下一个区段,并且处理器110A可以准备将第(m+1)个区段的数据搬移至SSD 100S,而使得第(m+1)个区段变为需要刷新状态。

在图8所示的实施例中,如果处理器110A判断写入指标在具有刷新状态的区段处,则处理器110A将检查下一个区段是否具有空白状态。如果下一区段具有空白状态,则处理器110A可以直接处理下一区段以将下一区段的数据移动到SSD100S,而无需等待目前区段的操作完成,因此,写入缓冲器500在使用上将更加有效率。在另一实施例中,如果处理器110A判断写入指标处于具有刷新状态的区段,则处理器110A将检查写入指标和刷新指标之间的任何区段是否具有空白状态,如果是,则处理器110A可以忽略目前区段,并且直接处理具有空白状态的区段以将数据移动到SSD 100S。举例来说,如果第(m+2)个区段变为空白状态,但是第m个区段和第(m+1)个区段仍然处于刷新状态,则处理器110A可以忽略第m个区段和第(m+1)个区段并直接处理第(m+2)个区段。

在一实施例中,处理器110A可以忽略不具有合并状态的任何区段。亦即,如果图8所示的第m个区段具有合并状态,则即使第(m+1)个区段和第(m+2)个区段具有空白状态,处理器110A也不能忽略第m个区段。具体来说,如果图8所示的第m个区段处于合并状态,则写入指标必须停留在第m个区段,直到第m个区段进入需要刷新状态为止。

图9为根据本发明的一实施例之写入缓冲器500的控制机制的流程图。参考本发明的上述实施例,流程描述如下。

步骤900:流程开始。

步骤902:自客户端装置接收数据。

步骤904:检查写入指标是否处于具有空白状态的区段,若是,则流程进入步骤906;若否,流程进入步骤908。

步骤906:将数据写入由写入指标所指示的区段。

步骤908:检查写入指标是否在具有合并状态的区段,若是,则流程停留在步骤908,直到写入指标指示的区段具有需要刷新状态为止;若否,则流程进入步骤910。

步骤910:检查写入指标和刷新指标之间的是否有任何区段具有空白状态,若是,则流程进入步骤912;若否,流程返回到步骤904。

步骤912:忽略目前区段并将数据写入状态为空白的下一个区段。

以上所述仅为本发明的较佳实施例,凡依本发明申请专利范围所做的均等变化与修饰,皆应属本发明的涵盖范围。

- 伺服器及相关的控制方法

- 伺服器与应用于伺服器的控制方法