一种基于SOI和TSV技术的新型垂直MOSFET结构

文献发布时间:2023-06-19 13:26:15

技术领域

本发明涉及三维集成电路技术领域,尤其涉及一种基于SOI和TSV技术的新型垂直MOSFET结构。

背景技术

随着科技不断的发展,对于半导体性能的要求不断提高。以场效应管为例,为了满足现代科技的需求,其尺寸在不断缩小。但是,传统的平面金属-氧化物半导体场效应晶体管MOSFET的缩放程度已经达到了极限,为了克服缩放带来的种种缺点,例如短沟道效应,垂直MOSFET作为一种新型的结构的MOSFET正逐渐取代平面MOSFET。垂直MOSFET不仅可以很好的克服缩放遇到的问题,并且可以制作成双栅以及栅环绕结构提高栅控能力和电流驱动能力(以增加器件电容为代价)。另一方面,硅技术SOI可以有效的降低寄生电容,漏电流和功耗,并且可以有效抑制衬底的脉冲电流干扰。然而目前关于SOI的研究主要集中在平面MOSFET上。

如公开号为CN109659223A的专利公开了一种改进型SiC平面MOSFET器件的制备方法,该专利在传统MOSFET外延表面生长了一层几十纳米的低掺杂外延层,掺杂浓度在1e14cm

在三维集成电路领域中,芯片相互堆叠,以增强集成的功能,并缩短信号路径,从而提高整体通信速度,其中硅通孔技术(TSV)是工业界公认的3D芯片集成的选择,此外垂直MOSFET因其占用面积小,性能良好得到了广泛的研究。

发明内容

本发明的目的是针对现有技术的缺陷,提供一种基于SOI和TSV技术的新型垂直MOSFET结构。

为了实现以上目的,本发明采用以下技术方案:

一种基于SOI和TSV技术的新型垂直MOSFET结构,包括自下而上的衬底Si、埋氧化层SiO

进一步的,所述栅极区域设置于多晶硅p-Si硅通孔的侧壁中央是通过超高分辨率电子束负胶HSQ固定的。

进一步的,在漏极区域和栅极区域施加一定电压,漏极区域和源极区域之间形成垂直沟道,并且栅极区域环绕于形成的沟道。

进一步的,所述漏极区域的电压为0V-5V;栅极区域的电压大于0.45V。

进一步的,垂直MOSFET结构的掺杂浓度为1×10

与现有技术相比,本发明将垂直MOSFET与SOI技术相结合,具有较大的漏极饱和电流,接近极限值的亚阈值斜率(SS)以及优秀的开关比(I

附图说明

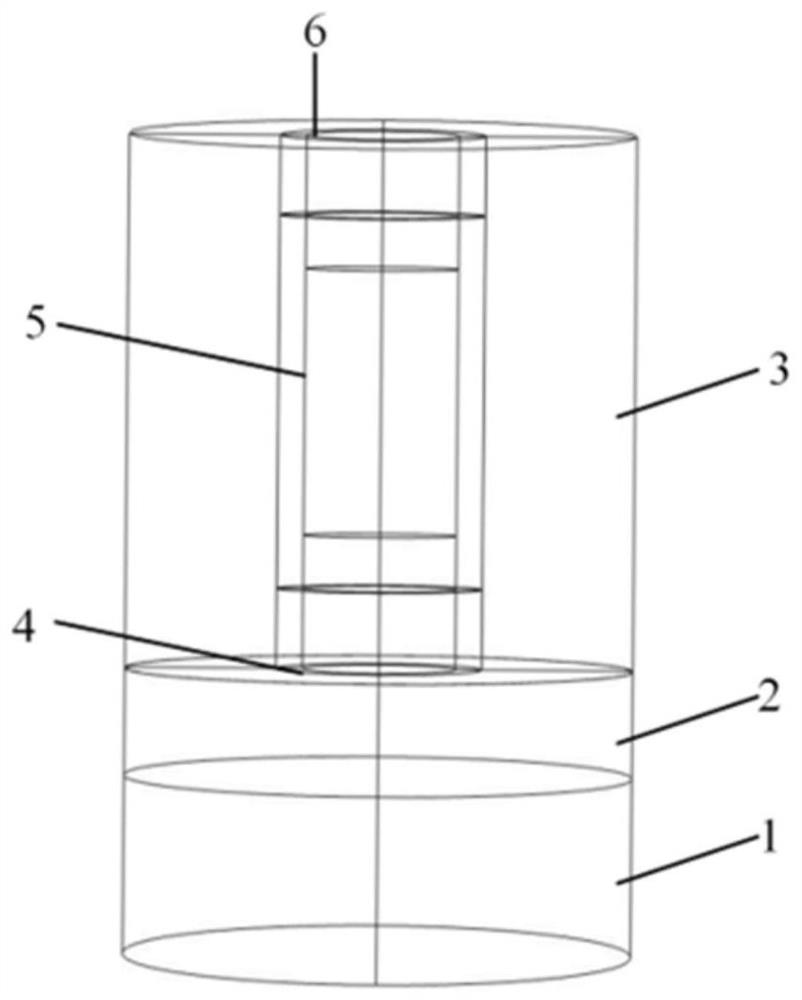

图1是本实施例一提供的垂直MOSFET的正视图;

图2是本实施例一提供的垂直MOSFET俯视图;

图3是本实施例一提供的垂直MOSFET n型离子掺杂截面示意图;

图4是本实施例一提供的垂直MOSFET沟道形成图;

图5是本实施例二提供的垂直MOSFET输出特性曲线图;

图6是本实施例二提供的垂直MOSFET转移特性曲线图;

图7是本实施例二提供的垂直MOSFET转移特性曲线图。

具体实施方式

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

本发明的目的是针对现有技术的缺陷,提供了一种基于SOI和TSV技术的新型垂直MOSFET结构。

实施例一

本实施例提供一种基于SOI和TSV技术的新型垂直MOSFET结构,如图1-2所示,包括自下而上的衬底Si1、埋氧化层SiO

埋氧化层SiO

多晶硅p-Si3叠置于埋氧化层SiO

源极区域4设置于埋氧化层SiO

栅极区域5设置于多晶硅p-Si3硅通孔的侧壁中央,栅极区域5环绕于硅通孔的侧壁,且使用超高分辨率电子束负胶HSQ作为栅极垫板,将栅极区域固定在硅通孔侧壁中央位置。

漏极区域处于多晶硅p-Si的顶部。

在垂直MOSFET开启工作状态下,即在漏极区域和栅极区域施加一定电压,源极区域和漏极区域之间会形成垂直沟道,而栅极区域环绕于这一垂直沟道从而有效提高栅控能力。

如图3所示为垂直MOSFET n型离子掺杂截面示意图,其中掺杂浓度为1×10

如图4所示为垂直MOSFET在开启状态下的沟道状态:在漏极电压为0V-5V(本实施例设为0.01V),栅极电压大于0.45V时,垂直沟道形成。

与现有技术相比,本实施例将垂直MOSFET与SOI技术相结合,具有较大的漏极饱和电流,接近极限值的亚阈值斜率(SS)以及优秀的开关比(I

实施例二

本实施例提供的一种基于SOI和TSV技术的新型垂直MOSFET结构与实施例一的不同之处在于:

本实施例使用商业多物理场仿真软件来模拟其工作状态,通过仿真结果对其相关电学性能进行评估。

如图5所示为垂直MOSFET的输出特性曲线图,栅极的电压分别设定为2V、3V和4V,漏极的电压设为0V-5V,垂直MOSFET在栅极电压为4V和漏极电压为5V时其漏极饱和电流可以达到1600μA,具有优秀的电路驱动能力;

如图6所示为垂直MOSFET的转移特性曲线图,图6中所示该垂直MOSFET的阈值电压在0.45V左右;

如图7所示为垂直MOSFET转移特性曲线图(y轴采用对数坐标),测试了三种不同漏极电压(0.01V,0.1V,2V)下的开关比以及SS,最大的I

本实施例应用于三维集成电路领域中一种新型垂直MOSFET的结构设计,特别是应用于现代三维集成电路领域中的开关器件。本实施例的优势在于:首先,在结构方面,将垂直MOSFET结构与SOI技术相结合,进一步提高MOSFET的性能,其高漏极饱和电流具有优秀的电路驱动能力,其高达1.28×10

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

- 一种基于SOI和TSV技术的新型垂直MOSFET结构

- 基于SOI衬底的TSV通孔绝缘层测试结构