基于忆阻器的平衡三值译码器电路

文献发布时间:2023-06-19 13:45:04

技术领域

本发明属于电路设计技术领域,涉及一种三值数字逻辑电路结构,具体涉及一种物理可实现的基于忆阻器的平衡三值译码器电路的设计与实现。

背景技术

随着现代信息技术的进一步发展,数字系统的集成度不断提高,在纳米级电路设计中二值逻辑实现的关键问题——互联限制日益凸显,用于集成电路设计的互联线增大了系统的延迟、噪声以及功耗。与二值逻辑相比,三值逻辑作为一种多值逻辑,其具有单线信息携带量更高,电路的处理能力更强,电路复杂度更低等优点,使得三值逻辑可成为替代二值逻辑实现高密度信息逻辑系统的一种有效方案。

在三值逻辑电路的设计方案中,学术界已经基于不同技术提出了较多设计方案,如CMOS、碳纳米管场效应管(Carbon Nanotube Field Effect Transistor,CNTFET)等,但其中一些电路结构较为复杂且难以集成,未能体现三值逻辑电路的显著优势。1971年,蔡少棠教授基于电路理论的完备性首次预测了忆阻器的存在。直到2008年,惠普实验室成功研制出第一个忆阻器的物理器件,由此引发了全球范围内的忆阻器研究热潮。发展至今,忆阻器已广泛应用于非易失型存储、神经形态网络、数字逻辑运算等领域的研究。忆阻器凭借其纳米尺寸、功耗低且与CMOS技术相兼容等特点,为三值逻辑电路的发展提供了一条崭新的思路。

三值逻辑的表示方法主要分为两类:非平衡型和平衡型。非平衡型三值又包括正三值{0,1,2}和负三值{0,-1,-2},二者在逻辑符号的方向上是相对的;平衡型三值则采用{-1,0,1}来表示。其中,平衡三值无需设置符号位即可表示全体整数范围,此外,平衡三值的乘法操作不产生进位,加法操作在9种所有输入情况下也仅有2种有进位产生。因此,平衡三值逻辑在算术运算中较非平衡型三值有一定优势。由于忆阻器与CMOS技术相兼容且尺寸较小,更有利于电路集成度的进一步提高,因此,研究忆阻平衡三值逻辑电路有望提高信息存储密度、信息传输效率,对改善现有计算机的体系架构具有一定的促进作用。

发明内容

针对现有技术的不足,本发明提出了一种基于忆阻器的平衡三值译码器电路。

本发明解决技术问题所采取的技术方案如下:

所述基于忆阻器的平衡三值译码器电路,包括第一输出电路、第二输出电路、第三输出电路,形成了一个输入端和三个输出端的电路结构。

所述第一输出电路由第一忆阻器M

所述第一NMOS管T

所述第一忆阻器M

所述第二忆阻器M

所述第四NMOS管T

所述基于忆阻器的平衡三值译码器电路的一个输入端与三个输出端遵循以下关系:

当输入端为逻辑-1时,第一输出端X

进一步的,所述第一NMOS管T

进一步的,所述第二NMOS管T

进一步的,所述第四NMOS管T

本发明的有益效果是:基于忆阻器的平衡三值译码器电路,电路模型结构清晰简单、易于实现,对多值数字逻辑电路设计等诸多领域中的应用研究具有重要意义。

附图说明

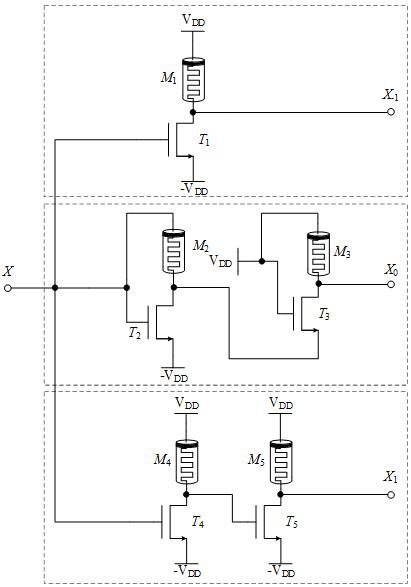

图1是本发明的基于忆阻器的平衡三值译码器电路结构图。

具体实施方式

下面结合附图对本发明优选实施例作详细说明。

本发明的基于忆阻器的平衡三值译码器电路结构如图1所示,由五个忆阻器和五个NMOS晶体管所构成,利用忆阻器的阻值切换特性和记忆特性加以实现。

所述基于忆阻器的平衡三值译码器电路结构包括第一输出电路、第二输出电路、第三输出电路三个部分,形成了一路输入三路输出的结构。其中,第一输出电路由第一忆阻器M

所述第一忆阻器M

基于忆阻器的平衡三值译码器电路中的逻辑状态为电压值,其中,定义电压V

对于第一输出电路部分,第一NMOS管T

对于第二输出电路部分,第二NMOS管T

即输出为逻辑“-1”。

当输入端X接地时,即输入为逻辑“0”,第二NMOS管T

对于第三输出电路部分,第四NMOS管T

本领域的普通技术人员应当认识到,以上实施例仅是用来验证本发明,而并非作为对本发明的限定,只要是在本发明的范围内,对以上实施例的变化、变形都将落在本发明的保护范围内。

- 基于忆阻器的平衡三值译码器电路

- 基于忆阻器的1-3线三值译码器电路