时钟生成方法、装置、芯片及电子设备

文献发布时间:2023-06-19 13:45:04

技术领域

本申请涉及集成电路设计领域,尤其涉及一种时钟生成方法、装置、芯片及电子设备。

背景技术

在通用微控制单元(Microcontroller Unit,简称MCU)设计中,通常要使用到串口通信,例如通用异步接收/发送装置(Universal Asynchronous Receiver/Transmitte,简称UART)接口。芯片UART接口采用一定的波特率并按照固定的协议与上位机进行通信。为了防止通信出错,对UART的波特率提出了一定的精度要求,即波特率频率偏差不能大于±2%。

一般MCU采用的方法是,设计一个高精度的RC振荡器,保证其频率在全温度和全电压范围内误差小于±2%,然后用这个RC振荡器进行分频,产生UART通信所需的各种波特率。这就对内部高频RC振荡器电路设计提出很高的要求,既要保证全温度和全电压下时钟的精度,又要保证大批量生产下芯片的一致性和稳定性,因此会带来一定程度的良率损失。

发明内容

本申请旨在至少在一定程度上解决相关技术中的技术问题之一。

为此,本申请的第一个目的在于提出一种时钟生成方法,可以实现不依赖于芯片内部振荡器的高精确性、一致性和稳定性,仅利用外接振荡器便可生成满足串口通信所需的时钟信号,可适用于内部振荡器频率精度不够的芯片,适用性更广,避免了良率损失。

本申请的第二个目的在于提出一种时钟生成装置。

本申请的第三个目的在于提出一种芯片。

本申请的第四个目的在于提出一种电子设备。

本申请的第五个目的在于提出一种计算机可读存储介质。

为达上述目的,本申请第一方面实施例提出了一种时钟生成方法,包括:对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,所述第二频率低于所述第一频率;对所述芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,所述第四频率低于所述第三频率;采用所述第四信号作为时钟对所述第二信号进行计数,得到第一计数结果;根据所述第一计数结果对所述分频系数进行调整,以使所述第一计数结果等于第一设定计数结果,并将所述第一计数结果等于所述第一设定计数结果时的所述分频系数确定为目标分频系数,将所述第一计数结果等于所述第一设定计数结果时的所述第四频率的第四信号确定为目标频率的目标信号;根据所述目标分频系数在所述目标信号的周期内生成目标倍频的时钟,所述目标倍频为2

本申请实施例提出的时钟生成方法,对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,采用第四信号作为时钟对第二信号进行计数,得到第一计数结果,根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果,并将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号,根据目标分频系数在目标信号的周期内生成目标倍频的时钟。以外接的第一振荡器的第一信号的第一频率为基准,通过动态检测和动态调整分频系数,将芯片内部的第二振荡器产生的第三信号分频为目标频率的目标信号,在此基础上通过倍频处理生成所需的时钟信号,本申请不依赖于芯片内部振荡器的高精确性、一致性和稳定性,仅利用外接振荡器便可生成满足串口通信所需的时钟信号,可适用于内部振荡器频率精度不够的芯片,适用性更广,避免了良率损失。

根据本申请的一个实施例,所述第一频率低于所述第三频率。

根据本申请的一个实施例,所述分频系数的初始值根据所述第三信号的额定频率和所述目标频率确定。

根据本申请的一个实施例,所述根据所述第一计数结果对所述分频系数进行调整,以使所述第一计数结果等于第一设定计数结果,包括:所述第一计数结果高于所述第一设定计数结果,则增大所述分频系数;所述第一计数结果低于所述第一设定计数结果,则减小所述分频系数。

根据本申请的一个实施例,所述增大所述分频系数和/或所述减小所述分频系数时的步长根据所述第一计数结果和所述第一设定计数结果的差值确定。

根据本申请的一个实施例,所述根据所述目标分频系数在所述目标信号的周期内生成目标倍频的时钟,包括:根据所述目标分频系数和所述目标倍频确定基础计数溢出值N和计数溢出值需要加一的周期数M,所述N和所述M为自然数;采用所述第三信号作为时钟从零进行计数,得到第二计数结果;所述第二计数结果等于N,则输出一个高电平脉冲,并重复M次;所述第二计数结果等于N-1,则输出一个高电平脉冲,并重复(2

为达上述目的,本申请第二方面实施例提出了一种时钟生成装置,包括:第一分频模块,用于对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,所述第二频率低于所述第一频率;第二分频模块,用于对所述芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,所述第四频率低于所述第三频率;计数模块,用于采用所述第四信号作为时钟对所述第二信号进行计数,得到第一计数结果;调整模块,用于根据所述第一计数结果对所述分频系数进行调整,以使所述第一计数结果等于第一设定计数结果,并将所述第一计数结果等于所述第一设定计数结果时的所述分频系数确定为目标分频系数,将所述第一计数结果等于所述第一设定计数结果时的所述第四频率的第四信号确定为目标频率的目标信号;时钟生成模块,用于根据所述目标分频系数在所述目标信号的周期内生成目标倍频的时钟,所述目标倍频为2

本申请实施例提出的时钟生成装置,对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,采用第四信号作为时钟对第二信号进行计数,得到第一计数结果,根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果,并将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号,根据目标分频系数在目标信号的周期内生成目标倍频的时钟。以外接的第一振荡器的第一信号的第一频率为基准,通过动态检测和动态调整分频系数,将芯片内部的第二振荡器产生的第三信号分频为目标频率的目标信号,在此基础上通过倍频处理生成所需的时钟信号,本申请不依赖于芯片内部振荡器的高精确性、一致性和稳定性,仅利用外接振荡器便可生成满足串口通信所需的时钟信号,可适用于内部振荡器频率精度不够的芯片,适用性更广,避免了良率损失。

根据本申请的一个实施例,所述第一频率低于所述第三频率。

根据本申请的一个实施例,所述分频系数的初始值根据所述第三信号的额定频率和所述目标频率确定。

根据本申请的一个实施例,所述调整模块具体用于:所述第一计数结果高于所述第一设定计数结果,则增大所述分频系数;所述第一计数结果低于所述第一设定计数结果,则减小所述分频系数。

根据本申请的一个实施例,所述增大所述分频系数和/或所述减小所述分频系数时的步长根据所述第一计数结果和所述第一设定计数结果的差值确定。

根据本申请的一个实施例,所述时钟生成模块具体用于:根据所述目标分频系数和所述目标倍频确定基础计数溢出值N和计数溢出值需要加一的周期数M,所述N和所述M为自然数;采用所述第三信号作为时钟从零进行计数,得到第二计数结果;所述第二计数结果等于N,则输出一个高电平脉冲,并重复M次;所述第二计数结果等于N-1,则输出一个高电平脉冲,并重复(2

为达上述目的,本申请第三方面实施例提出了一种芯片,包括:第二振荡器和如本申请第二方面所述的时钟生成装置。

为达上述目的,本申请第四方面实施例提出了一种电子设备,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述程序时,实现如本申请第一方面实施例所述的时钟生成方法。

为达上述目的,本申请第五方面实施例提出了一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现如本申请第一方面实施例所述的时钟生成方法。

附图说明

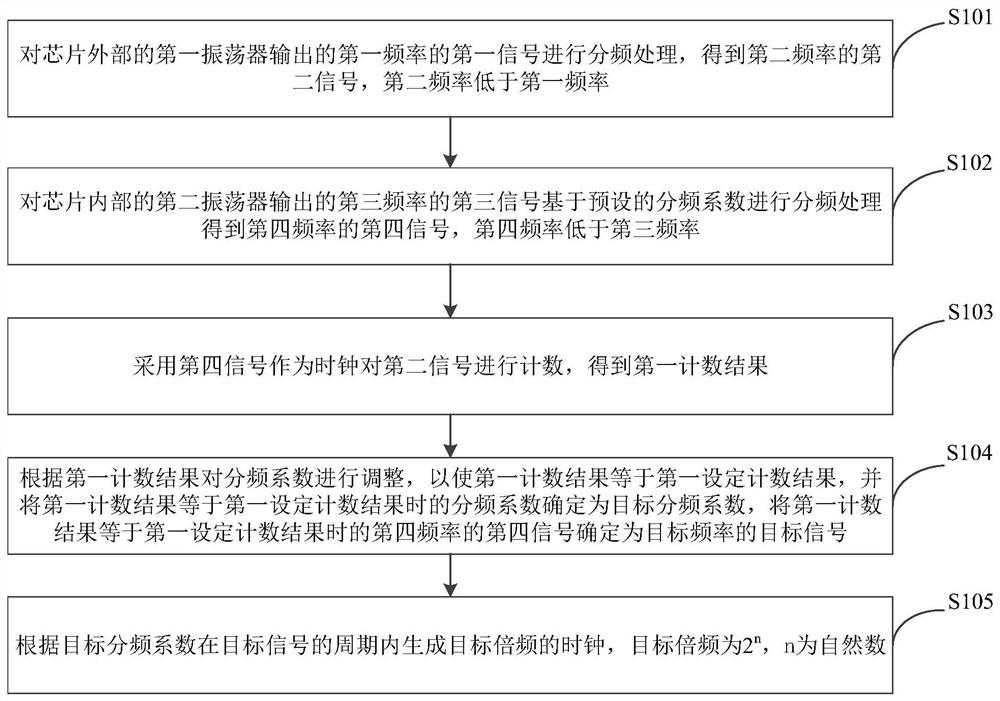

图1是根据本申请一个实施例的时钟生成方法的流程示意图;

图2是根据本申请一个实施例的时钟生成方法对第一信号进行分频处理的脉冲示意图;

图3是根据本申请一个实施例的时钟生成方法对第三信号进行分频处理的脉冲示意图;

图4是根据本申请另一个实施例的时钟生成方法的流程示意图;

图5是根据本申请另一个实施例的时钟生成方法生成目标信号的脉冲示意图;

图6是根据本申请另一个实施例的时钟生成方法生成目标信号的脉冲示意图;

图7是根据本申请一个实施例的时钟生成方法的原理示意图;

图8是根据本申请一个实施例的时钟生成方法的整体流程示意图;

图9是根据本申请一个实施例的时钟生成装置的框图;

图10是根据本申请一个实施例的芯片的示意图;

图11是根据本申请一个实施例的电子设备的示意图。

具体实施方式

下面详细描述本申请的实施例,实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本申请,而不能理解为对本申请的限制。

下面结合附图来描述本申请实施例的时钟生成方法、装置、芯片及电子设备。

图1是根据本申请一个实施例的时钟生成方法的流程示意图。本申请实施例的时钟生成方法,可由本申请实施例提供的时钟生成装置执行,时钟生成装置可以设置在芯片等电子设备上。如图1所示,本申请实施例的时钟生成方法具体可包括以下步骤:

S101,对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,第二频率低于第一频率。

本申请实施例中,芯片可用于产生串口通信所需的时钟,芯片外接第一振荡器,利用芯片内部的时钟生成装置对第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,其中第二频率低于第一频率。例如,如图2所示,第一振荡器输出第一频率为32768赫兹(Hz)的第一信号,经过256分频得到第二频率为128Hz(128Hz=32768Hz/256)的第二信号。

S102,对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,第四频率低于第三频率。

本申请实施例中,芯片内部存在第二振荡器,用于输出第三频率的第三信号,例如第二振荡器可以为高频电阻-电容(Resistor-Capacitance,简称RC)振荡器。对第二振荡器输出的第三频率的第三信号进行分频处理,得到第四频率的第四信号,其中可以预先设置分频系数D,基于分频系数D进行分频以获取所需频率的信号,分频系数D的数值可根据需要设置,本申请不做限定。其中分频后得到的第四频率低于第二振荡器输出的第三频率。

S103,采用第四信号作为时钟对第二信号进行计数,得到第一计数结果。

本申请实施例中,采用步骤S102获得的第四信号作为时钟对步骤S101获得的第二信号进行计数,例如对第二信号的周期进行计数,得到第一计数结果C。

S104,根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果,并将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号。

本申请实施例中,根据步骤S103获得的第一计数结果C对步骤S102中的分频系数D进行调整,如图3所示,基于调整后的分频系数D对第三频率的第三信号进行分频处理,得到第四频率的第四信号,基于调整分频系数后得到的第四频率的第四信号对第二信号进行计数,使得第一计数结果C等于第一设定计数结果,其中,第一设定计数结果可根据需要预先设置。

通过对分频系数D的调整,当第一计数结果C等于第一设定计数结果时,将此时对应的分频系数D确定为目标分频系数,将此时对应的第四频率的第四信号确定为目标频率的目标信号。其中,目标频率为预先设定的,第一设定计数结果=目标频率/第二信号的第二频率。

例如,第二振荡器输出的第三信号的额定频率为32兆赫兹(MHz),由于第二振荡器频率精度可能不够准确,所以第二振荡器实际输出第三频率约为32MHz的第三信号,通过调整分频系数D,得到第四频率为57600Hz的第四信号,使得基于57600Hz的第四信号对128Hz的第二信号进行周期计数时得到的第一计数结果C等于第一设定计数结果450,则可以将此时的分频系数D确定为目标分频系数,将第四频率为57600Hz的第四信号确定为目标信号,57600Hz为目标频率,其中,第一设定计数结果450=目标频率57600Hz/第二信号的第二频率128Hz。

此处需要说明的是,分频系数可以自初始值开始调整,其中初始值根据第三信号的额定频率和目标频率确定。例如,第三信号的额定频率为32MHz,所需要的目标频率为57600Hz,计算额定频率与目标频率的比值即32MHz/57600Hz约等于555,则分频系数的初始值可以设置为555,以便能够更加快速地通过对分频系数的调整确定满足条件的目标分频系数。

S105,根据目标分频系数在目标信号的周期内生成目标倍频的时钟,目标倍频为2

本申请实施例中,目标分频系数确定后,目标信号被锁定,根据步骤S104确定的目标分频系数在目标信号的周期内生成目标倍频的时钟,其中目标倍频可以为2

本领域技术人员可以理解,本申请实施例中的第一振荡器和第二振荡器具体可以为晶体振荡器。本申请实施例生成的目标倍频的时钟,可以作为UART接口输入信号的采样时钟和/或UART接口发送信号的源头时钟。

本申请实施例的时钟生成方法,对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,采用第四信号作为时钟对第二信号进行计数,得到第一计数结果,根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果,并将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号,根据目标分频系数在目标信号的周期内生成目标倍频的时钟。以外接的第一振荡器的第一信号的第一频率为基准,通过动态检测和动态调整分频系数,将芯片内部的第二振荡器产生的第三信号分频为目标频率的目标信号,在此基础上通过倍频处理生成所需的时钟信号,本申请不依赖于芯片内部振荡器的高精确性、一致性和稳定性,仅利用外接振荡器便可生成满足串口通信所需的时钟信号,可适用于内部振荡器频率精度不够的芯片,适用性更广,避免了良率损失。

图4为根据本申请另一个实施例的时钟生成方法的流程示意图。如图4所示,在上述图1所示实施例的基础之上,本申请实施例的时钟生成方法,具体可包括以下步骤:

S401,对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,第二频率低于第一频率。

S402,对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,第四频率低于第三频率。

S403,采用第四信号作为时钟对第二信号进行计数,得到第一计数结果。

S404,根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果,并将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号。

本申请实施例中,步骤S401-S404与上述实施例中的步骤S101-S104相同,具体过程此处不再赘述。

上述实施例中的步骤S105“根据目标分频系数在目标信号的周期内生成目标倍频的时钟”,具体可包括以下步骤S405-S408:

S405,根据目标分频系数和目标倍频确定基础计数溢出值N和计数溢出值需要加一的周期数M,N和M为自然数。

本申请实施例中,考虑到目标分频系数不一定是目标倍频2

S406,采用第三信号作为时钟从零进行计数,得到第二计数结果。

本申请实施例中,可以采用第三信号作为计数器的时钟信号,计数器从零开始计数,得到第二计数结果。

S407,第二计数结果等于N,则输出一个高电平脉冲,并重复M次。

本申请实施例中,当第二计数结果等于N时,输出一个高电平脉冲,并将第二计数结果重置为零后再次开始计数,重复M次,从而能够在一个目标频率周期内产生M个倍频时钟周期长度为(N+1)个第三信号周期的高电平脉冲。

S408,第二计数结果等于N-1,则输出一个高电平脉冲,并重复(2

本申请实施例中,当第二计数结果等于N-1时,输出一个高电平脉冲,并将第二计数结果重置为零后再次开始计数,重复(2

下面举例进行说明,以目标倍频为2

表1目标分频系数与生成的时钟的对应关系表

根据表1可知:

当D[3:0]=4’b0000,D[9:4]=6’b100010时,此时D能被16整除,确定出基础计数溢出值N=34,计数溢出值需要加一的周期数M=0,,如图5所述,计数器从0计数到第二计数结果(N-1)=33后返回0,产生一个高电平脉冲,重复进行(2

当D[3:0]=4’b1001,D[9:4]=6’b100010时,此时D不能被16整除,确定出基础计数溢出值N=34,计数溢出值需要加一的周期数M=9。如图6所示,计数器从0计数到第二计数结果N=34后返回0,产生一个高电平脉冲,重复进行9次;计数器从0计数到第二计数结果(N-1)=33后返回0,产生一个高电平脉冲,重复进行(2

当D[3:0]=4’b1111,D[9:4]=6’b100010时,此时D不能被16整除,确定出基础计数溢出值N=34,计数溢出值需要加一的周期数M=15。计数器从0计数到第二计数结果N=34后返回0,产生一个高电平脉冲,重复进行15次;计数器从0计数到第二计数结果(N-1)=33后返回0,产生一个高电平脉冲,重复进行(2

综上,通过本申请实施例的方法可以保证产生的2

作为一种可行的实施方式,上述实施例中第一频率低于第三频率即外接的第一振荡器为低频振荡器。

在本申请的一个实施例中,如图7所示,上述实施例中步骤S404“根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果”具体可包括以下两种情况:

情况一:第一计数结果高于第一设定计数结果,则增大分频系数。

情况二:第一计数结果低于第一设定计数结果,则减小分频系数。

其中,增大分频系数和/或减小所述分频系数时的步长可以根据第一计数结果和第一设定计数结果的差值确定,例如差值越大,步长越长,以尽量完成调整过程。

本申请实施例的时钟生成方法,对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,采用第四信号作为时钟对第二信号进行计数,得到第一计数结果,根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果,并将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号,根据目标分频系数在目标信号的周期内生成目标倍频的时钟。以外接的第一振荡器的第一信号的第一频率为基准,通过动态检测和动态调整分频系数,将芯片内部的第二振荡器产生的第三信号分频为目标频率的目标信号,在此基础上通过倍频处理生成所需的时钟信号,本申请不依赖于芯片内部振荡器的高精确性、一致性和稳定性,仅利用外接振荡器便可生成满足串口通信所需的时钟信号,可适用于内部振荡器频率精度不够的芯片,适用性更广,避免了良率损失。

为清楚说明本申请实施例的时钟生成方法,下面结合图7-图8对本申请实施例的时钟生成方法进行详细说明。图7为本申请一实施例的时钟生成方法的原理示意图,如图7所示,第一振荡器输出的第一信号经过分频得到第二信号,第二振荡器输出的第三信号经过分频系数D分频得到第四信号,采用第四信号作为时钟对第二信号进行计数,记录第一计数结果,对分频系数D进行调整,使得第一计数结果等于第一设定计数结果,将此时的分频系数确定为目标分频系数,对应的第四信号确定为目标信号,采用第三信号作为时钟,基于目标信号生成所需的倍频时钟信号。

图8为根据本申请另一个实施例的时钟生成方法的流程示意图。如图8所示,本申请实施的时钟生成方法具体可包括以下步骤:

S801,对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号。

S802,对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号。

S803,采用第四信号作为时钟对第二信号进行计数,得到第一计数结果。

S804,判断第一计数结果是否等于第一设定计数结果。

若是,则执行步骤S808,若否,则执行步骤S805。

S805,判断第一计数结果是否高于第一设定计数结果。

若是,则执行步骤S806,若否,则执行步骤S807。

S806,增大分频系数。并返回步骤S802。

S807,减小分频系数。并返回步骤S802。

S808,将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号。

S809,根据目标分频系数和目标倍频确定基础计数溢出值N和计数溢出值需要加一的周期数M。

S810,采用第三信号作为时钟从零进行计数,得到第二计数结果。

S811,第二计数结果等于N,则输出一个高电平脉冲,并重复M次。

S812,第二计数结果等于N-1,则输出一个高电平脉冲,并重复(2

为了实现上述实施例,本申请实施例还提出一种时钟生成装置,该时钟生成装置可实现上述任一实施例的时钟生成方法。图9是根据本申请一个实施例的时钟生成装置的结构示意图。如图9所示,本申请实施例的时钟生成装置90,具体可包括:第一分频模块91、第二分频模块92、计数模块93、调整模块94和时钟生成模块95。

第一分频模块91,用于对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,第二频率低于第一频率。

第二分频模块92,用于对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,第四频率低于第三频率。

计数模块93,用于采用第四信号作为时钟对第二信号进行计数,得到第一计数结果。

调整模块94,用于根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果,并将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号。

时钟生成模块95,用于根据目标分频系数在目标信号的周期内生成目标倍频的时钟,目标倍频为2

进一步的,在本申请实施例一种可能的实现方式中,第一频率低于第三频率。

进一步的,在本申请实施例一种可能的实现方式中,分频系数的初始值根据第三信号的额定频率和目标频率确定。

进一步的,在本申请实施例一种可能的实现方式中,调整模块94具体用于:第一计数结果高于第一设定计数结果,则增大分频系数;第一计数结果低于第一设定计数结果,则减小分频系数。

进一步的,在本申请实施例一种可能的实现方式中,增大分频系数和/或减小分频系数时的步长根据第一计数结果和第一设定计数结果的差值确定。

进一步的,在本申请实施例一种可能的实现方式中,时钟生成模块95具体用于:根据目标分频系数和目标倍频确定基础计数溢出值N和计数溢出值需要加一的周期数M,N和M为自然数;采用第三信号作为时钟从零进行计数,得到第二计数结果;第二计数结果等于N,则输出一个高电平脉冲,并重复M次;第二计数结果等于N-1,则输出一个高电平脉冲,并重复(2

需要说明的是,前述对时钟生成方法实施例的解释说明也适用于该实施例的时钟生成装置,此处不再赘述。

本申请实施例的时钟生成装置,对芯片外部的第一振荡器输出的第一频率的第一信号进行分频处理,得到第二频率的第二信号,对芯片内部的第二振荡器输出的第三频率的第三信号基于预设的分频系数进行分频处理,得到第四频率的第四信号,采用第四信号作为时钟对第二信号进行计数,得到第一计数结果,根据第一计数结果对分频系数进行调整,以使第一计数结果等于第一设定计数结果,并将第一计数结果等于第一设定计数结果时的分频系数确定为目标分频系数,将第一计数结果等于第一设定计数结果时的第四频率的第四信号确定为目标频率的目标信号,根据目标分频系数在目标信号的周期内生成目标倍频的时钟。以外接的第一振荡器的第一信号的第一频率为基准,通过动态检测和动态调整分频系数,将芯片内部的第二振荡器产生的第三信号分频为目标频率的目标信号,在此基础上通过倍频处理生成所需的时钟信号,本申请不依赖于芯片内部振荡器的高精确性、一致性和稳定性,仅利用外接振荡器便可生成满足串口通信所需的时钟信号,可适用于内部振荡器频率精度不够的芯片,适用性更广,避免了良率损失。

为了实现上述实施例,本申请实施例还提出一种芯片100,图10是根据本申请一个实施例的芯片的示意图。如图10所示,该芯片100具体可包括:第二振荡器101和如上述实施例所示的时钟生成装置90。

为了实现上述实施例,本申请实施例还提出一种电子设备110,如图11所示,该电子设备110具体可包括存储器111、处理器112及存储在存储器111上并可在处理器112上运行的计算机程序,处理器112执行程序时,实现如上述实施例所示的时钟生成方法。

为了实现上述实施例,本申请实施例还提出一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行,以实现如上述实施例所示的时钟生成方法。

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本申请的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

尽管上面已经示出和描述了本申请的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本申请的限制,本领域的普通技术人员在本申请的范围内可以对上述实施例进行变化、修改、替换和变型。

- 时钟生成方法、装置、芯片及电子设备

- 时钟生成装置、电子设备、移动体及时钟生成方法