液晶面板

文献发布时间:2023-06-19 13:45:04

技术领域

本发明的实施例涉及一种液晶面板。

背景技术

近年来,随着显示技术的不断进步,消费者对于显示器的显示品质的要求也越来越高。然而,为了制造高效能的显示器,显示装置需要具备足够高的解析度。

为了提升显示装置的解析度,许多厂商致力于研究缩小像素的尺寸的方法。一般而言,在液晶显示装置显示画面时,每个像素都会产生不同程度的暗纹,这些暗纹通常会出现在液晶分子较难控制的位置,例如电极的边缘。这些暗纹会影响显示画面的亮度,且可能会导致显示画面出现异常。

发明内容

本发明的目的在于提供一种液晶面板,能减少子像素内的暗纹对显示画面造成的影响。

本发明的至少一实施例提供一种液晶面板,包括第一基板、多条扫描线、多条数据线、多个子像素结构、第二基板以及液晶层。多条扫描线、多条数据线以及多个子像素结构位于第一基板上。各子像素结构包括有源元件、像素电极以及第一共用电极。有源元件电性连接至对应的一条扫描线以及对应的一条数据线。像素电极电性连接至有源元件。像素电极具有封闭图案。封闭图案包括至少一第一狭缝以及至少两个第二狭缝。第一狭缝沿着第一方向延伸。第二狭缝沿着实质上正交于第一方向的第二方向延伸。第二狭缝分别位于第一狭缝的两端。第一共用电极包围像素电极。第二基板重叠于第一基板。液晶层位于第一基板与第二基板之间。液晶层的厚度为CG,第一狭缝的宽度为Lm,第二狭缝的宽度为Ls,3≥Lm/CG≥2,且0.75≥Ls/CG≥0.4。本发明的至少一实施例提供一种液晶面板,包括第一基板、多条扫描线、多条数据线、多个子像素结构、第二基板以及液晶层。多条扫描线、多条数据线以及多个子像素结构位于第一基板上。各子像素结构包括有源元件、像素电极以及第一共用电极。有源元件电性连接至对应的一条扫描线以及对应的一条数据线。像素电极电性连接至有源元件。像素电极具有第一狭缝以及两个第二狭缝。第一狭缝沿着第一方向延伸。两个第二狭缝沿着实质上正交于第一方向的第二方向延伸。两个第二狭缝分别连接第一狭缝的两端。第一共用电极包围像素电极。第二基板重叠于第一基板。液晶层位于第一基板与第二基板之间。液晶层的厚度为CG,第一狭缝的宽度为Lm,两个第二狭缝的宽度为Ls,3≥Lm/CG≥2,且0.75≥Ls/CG≥0.4。

本发明的有益效果在于,通过第一狭缝以及第二狭缝的设置,能使子像素内的暗纹位置更稳定,由此降低暗纹对显示画面造成的影响。

附图说明

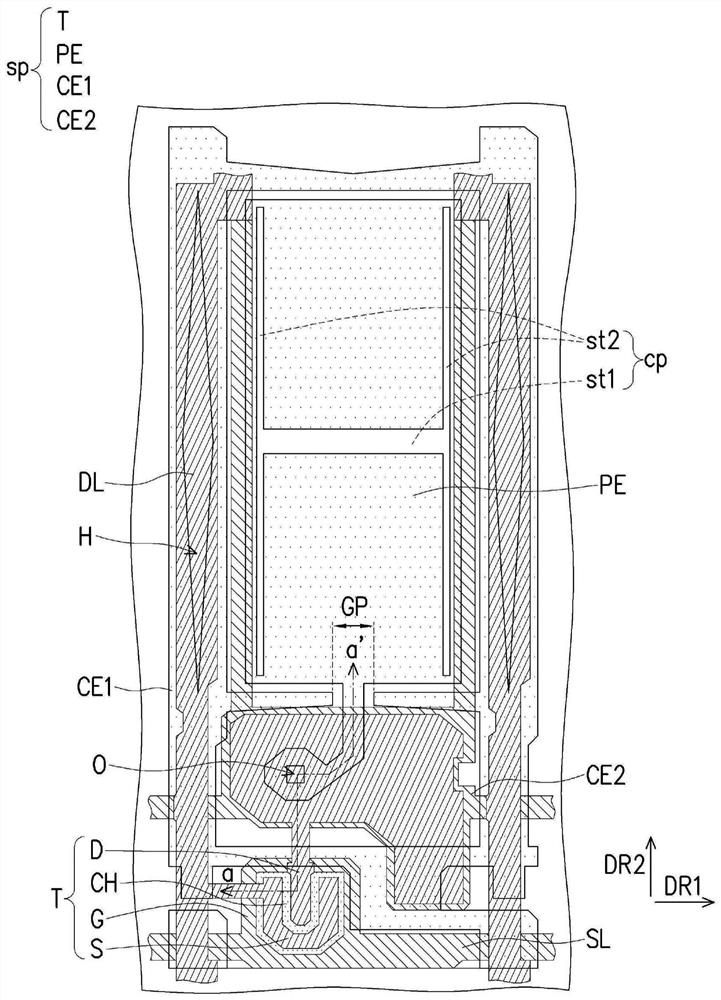

图1A为依照本发明的一实施例的一种液晶面板的剖面示意图。

图1B为图1A的一种液晶面板的俯视示意图。

图1C为图1B的像素电极以及第一共用电极的俯视示意图。

图2为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。

图3为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。

图4A为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。

图4B为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。

图5A为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。

图5B为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。

图6A为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。

图6B为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。

图7为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。

图8A为本发明的一实施例的一种液晶面板的俯视示意图。

图8B为图8A的像素电极以及第一共用电极的俯视示意图。

图8C为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。

图9为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。

附图标记如下:

10:液晶面板

100:第一基板

110:栅极绝缘层

120:平坦层

130:第一配向膜

140:第一偏光片

200:第二基板

210:黑矩阵

220:色彩转换元件

230:第二配向膜

240:第二偏光片

300:液晶层

a、b:间距

cp:封闭图案

CE1:第一共用电极

CE2:第二共用电极

CH:通道层

CG:厚度

D:漏极

DL:数据线

DP:缺陷点

DR1:第一方向

DR2:第二方向

DS1、DS2、DS3、DS4、DS5、DS6

EP:延伸部

G:栅极

GP:间隙

H、O:开口

Lm、Ls:宽度

N1、N2:节点

OP:开口区

OS:外框部

PA1:第一偏光轴

PA2:第二偏光轴

PE:像素电极

P1:第一部分

P2:第二部分

P3:第三部分

P4:第四部分

P5:连接部

R1:第一凸起

R2:第二凸起

st1:第一狭缝

st2:第二狭缝

S:源极

SL:扫描线

sp:子像素结构

T:有源元件

TH:通孔

具体实施方式

图1A为依照本发明的一实施例的一种液晶面板的剖面示意图。图1B为图1A的一种液晶面板的俯视示意图,其中图1A对应图1B的线a-a’。

请参考图1A与图1B,液晶面板10包括第一基板100、多条扫描线SL、多条数据线DL、多个子像素结构sp、第二基板200以及液晶层300。第二基板200重叠于第一基板100。液晶层300位于第一基板100与第二基板200之间。液晶层300的厚度为CG。在一些实施例中,液晶层300的厚度CG约为2.4微米至3.8微米。在本实施例中,液晶层300包括负型液晶。在本实施例中,液晶面板10还包括第一配向膜130、第一偏光片140、黑矩阵210、色彩转换元件220、第二配向膜230以及第二偏光片240。

第一基板100与第二基板200的材质可为玻璃、石英、有机聚合物或是其他可适用的材料。多条扫描线SL、多条数据线DL以及多个子像素结构sp位于第一基板100上。在本实施例中,多个子像素结构sp阵列于第一基板100上,图1A与图1B以液晶面板10中的其中一个子像素SP及其周围构件进行说明。

各子像素结构sp包括有源元件T、像素电极PE以及第一共用电极CE1。在本实施例中,各子像素结构sp还包括第二共用电极CE2。

有源元件T电性连接至对应的一条扫描线SL以及对应的一条数据线DL。有源元件T包括栅极G、通道层CH、源极S以及漏极D。

栅极G、扫描线SL以及第二共用电极CE2形成于第一基板100上。在本实施例中,栅极G、扫描线SL以及第二共用电极CE2属于相同导电膜层。举例来说,栅极G、扫描线SL以及第二共用电极CE2是由同一层导电材料图案化后所形成。在本实施例中,栅极G、扫描线SL以及第二共用电极CE2为单层或多层结构,且栅极G、扫描线SL以及第二共用电极CE2的材料包括金属、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或其他合适的材料、或是金属材料与其他导电材料的堆叠层。

栅极绝缘层110形成于栅极G、扫描线SL以及第二共用电极CE2上。栅极绝缘层110的材料包括有机绝缘层、无机绝缘层或其组合。通道层CH形成于栅极绝缘层110上,且通道层CH在垂直第一基板100的方向上重叠于栅极G。通道层CH为单层或多层结构,通道层CH的材料包括非晶硅、多晶硅、微晶硅、单晶硅、有机半导体材料、氧化物半导体材料(例如:铟锌氧化物、铟镓锌氧化物或是其他合适的材料、或上述的组合)或其他合适的材料或上述材料的组合。

数据线DL、源极S以及漏极D形成于栅极绝缘层110以及通道层CH上。源极S以及漏极D电性连接至通道层CH。在一些实施例中,源极S与通道层CH之间以及漏极D与通道层CH之间还包括欧姆接触层(附图中未绘出),但本发明不以此为限。源极S电性连接至数据线DL。在本实施例中,数据线DL、源极S以及漏极D属于相同导电膜层。举例来说,数据线DL、源极S以及漏极D是由同一层导电材料图案化后所形成。在本实施例中数据线DL、源极S以及漏极D为单层或多层结构,且数据线DL、源极S以及漏极D的材料包括金属、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或其他合适的材料、或是金属材料与其他导电材料的堆叠层。

平坦层120形成于数据线DL、源极S、漏极D以及栅极绝缘层110上。平坦层120覆盖数据线DL、源极S以及漏极D。平坦层120的材料包括有机绝缘层、无机绝缘层或其组合。在一些实施例中,平坦层120上还包括适用于超高开口技术(Ultra/Super High Aperture,UHA/SHA)的其他有机绝缘层,且所述有机绝缘层可以增加像素电极与金属导线之间的距离,由此减少电容效益并增加像素结构的开口率。

图1C为图1B的像素电极以及第一共用电极的俯视示意图。

请参考图1A至图1C,像素电极PE以及第一共用电极CE1形成于平坦层120上。像素电极PE通过平坦层120中的开口O而电性连接至有源元件T的漏极D。在本实施例中,像素电极PE以及第一共用电极CE1属于相同导电膜层。举例来说,像素电极PE以及第一共用电极CE1是由同一层导电材料图案化后所形成。像素电极PE以及第一共用电极CE1的材料包括透明导电材料,例如金属氧化物材料。

在本实施例中,像素电极PE具有封闭图案cp。封闭图案cp指的是未与像素电极PE的边缘连接的图案,即封闭图案cp与像素电极PE的边缘隔有一距离。封闭图案cp包括至少一第一狭缝st1以及至少两个第二狭缝st2。在本实施例中,封闭图案cp包括一个第一狭缝st1以及两个第二狭缝st2。第一狭缝st1沿着第一方向DR1延伸。第二狭缝st2沿着第二方向DR2延伸,第二方向DR2实质上正交于第一方向DR1。在本实施例中,扫描线SL沿着第一方向DR1延伸,且数据线DL沿着第二方向DR2延伸。换句话说,第一狭缝st1实质上平行于扫描线SL,且第二狭缝st2实质上平行于数据线DL,但本发明不以此为限。在其他实施例中,扫描线SL沿着第二方向DR2延伸,且数据线DL沿着第一方向DR1延伸。

两个第二狭缝st2分别位于第一狭缝st1的两端。在本实施例中,两个第二狭缝st2与第一狭缝st1的两端相连,并构成H形的封闭图案cp。在本实施例中,封闭图案cp为对称图案,且封闭图案cp的对称轴平行于第二方向DR2。

在本实施例中,第一狭缝st1的宽度为Lm,第二狭缝st2的宽度为Ls,3≥Lm/CG≥2,且0.75≥Ls/CG≥0.4。

在本实施例中,在第一方向DR1上封闭图案cp与像素电极PE的边缘(像素电极PE的左侧与右侧)之间的间距DS1介于3微米至4微米。在本实施例中,在第二方向DR2上第二狭缝st2与像素电极PE的下侧之间的间距DS2介于2.5微米至3.5微米。在本实施例中,在第二方向DR2上第二狭缝st2与像素电极PE的上侧之间的间距DS3介于2.5微米至3.5微米。

在本实施例中,像素电极PE包括的第一部分P1、第二部分P2、第三部分P3、第四部分P4以及连接部P5。第一部分P1在第二方向DR2上位于第一狭缝st1的一侧(上侧),且第二部分P2在第二方向DR2上位于第一狭缝st1的另一侧(下侧)。第三部分P3在第一方向DR1上位于第一狭缝st1以及第二狭缝st2的一侧(左侧),且第四部分P4在第一方向DR1上位于第一狭缝st1以及第二狭缝st2的另一侧(右侧)。连接部P5连接第二部分P2至有源元件T。在本实施例中,其中一个第二狭缝st2位于第一部分P1与第三部分P3之间以及第二部分P2与第三部分P3之间,且另外一个第二狭缝st2位于第一部分P1与第四部分P4之间以及第二部分P2与第四部分P4之间。在本实施例中,第三部分P3连接第一部分P1与第二部分P2,且第四部分P4连接第一部分P1与第二部分P2。

请参考图1C,第一共用电极CE1包围像素电极PE。子像素结构sp具有未重叠于黑矩阵210的开口区OP。在本实施例中,在子像素结构sp的开口区OP中,第一方向DR1上第一共用电极CE1与像素电极PE(像素电极PE的第三部分P3与第四部分P4)之间的间距为b,且在第二方向DR2上第一共用电极CE1与像素电极PE(像素电极PE的第一部分P1与第二部分P2)之间的间距为a,b/CG≥1.4,1.3≥a/CG≥1。

在本实施例中,第一共用电极CE1包括外框部OS以及两个延伸部EP。外框部OS环绕像素电极PE。两个延伸部连接该外框部OS,且自外框部OS朝向像素电极PE的第五部分P5延伸。像素电极PE的第五部分P5穿过两个延伸部EP之间的间隙GP。在本实施例中,外框部OS具有重叠于数据线DL的开口H。

请参考图1A与图1C,第一配向膜130位于第一共用电极CE1、像素电极PE以及平坦层120上,且第一配向膜130接触液晶层300。第一配向膜130例如为光固化后的材料及/或热固化后的材料。

第一偏光片140位于第一基板100上。第一偏光片140具有第一偏光轴PA1。第一偏光轴PA1约与第一方向DR1夹45度或135度。第一偏光轴PA1约与第二方向DR2夹45度或135度。

在本实施例中,黑矩阵210以及色彩转换元件220位于第二基板200上,但本发明不以此为限。在其他实施例中,黑矩阵210以及色彩转换元件220位于第一基板100上。色彩转换元件220例如包括红色滤光元件、绿色滤光元件以及蓝色滤光元件。

第二配向膜230位于第二基板200上,且第二配向膜230接触液晶层300。第二配向膜230例如为光固化后的材料及/或热固化后的材料。

第二偏光片240位于第二基板200上。第二偏光片240具有第二偏光轴PA2。第一偏光轴PA1约垂直于第二偏光轴PA2。第二偏光轴PA2约与第一方向DR1夹45度或135度。第二偏光轴PA2约与第二方向DR2夹45度或135度。

在本实施例中,在对液晶面板10进行配向之前,第一配向膜130与第二配向膜230尚未固化。在对液晶面板10进行配向时,对第一共用电极CE1施加第一电压,且对像素电极PE施加第二电压,第一电压高于第二电压。由于第一共用电极CE1与像素电极PE之间具有电位差,液晶层300中的液晶分子会倾倒。在液晶分子呈现预定排列及/或倾倒的状态下,可进行固化程序,例如光固化及/或热固化,以使第一配向膜130与第二配向膜230固化于液晶层300周边。在本实施例中,在像素电极PE的第一部分P1上的液晶层300的配向方向约平行于第一配向方向AD1,在像素电极PE的第二部分P2上的液晶层300的配向方向约平行于第二配向方向AD2,其中第一配向方向AD1与第二配向方向AD2指的是液晶分子在配向过程中的倾倒方向。

第一配向方向AD1与第二配向方向AD2约彼此相反,且第一配向方向AD1与第二配向方向AD2约平行于第二方向DR2。

在本实施例中,在配向过程中于第一狭缝st1上的液晶层300约朝向像素电极PE的左右两侧倾倒。换句话说,第一狭缝st1上的液晶层300的配向方向约平行于第三配向方向AD3与第四配向方向AD4,第三配向方向AD3与第四配向方向AD4约彼此相反,且第三配向方向AD3与第四配向方向AD4约平行于第一方向DR1。

基于上述,本实施例的像素电极PE具有封闭图案cp,封闭图案cp包括第一狭缝st1以及第二狭缝st2,通过第一狭缝st1以及第二狭缝st2的设置,能使子像素内的暗纹位置更稳定,由此降低暗纹对显示画面造成的影响。

图2为图1B的子像素结构对液晶层进行配向程序时的液晶效果的模拟图。

请参考图2,第一狭缝st1的边缘与像素电极PE上下两侧的边缘皆有暗纹产生。在本实施例中,第一狭缝st1上会有缺陷点(Defect point)DP产生,缺陷点DP例如是出现在暗纹交叉的位置。

通过第一狭缝st1以及第二狭缝st2的设置,能使子像素内的暗纹位置更稳定,由此降低暗纹对显示画面造成的影响。

图3为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。在此必须说明的是,图3的实施例沿用图1A至图1C的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

在图3中,箭头的指向代表的是液晶分子在配向过程中的倾倒方向。

图3的像素电极PE与图1C的像素电极PE的差异在于:图3的像素电极PE具有第一凸起R1、第二凸起R2以及通孔TH,且图3的像素电极PE的第二狭缝st2连接第一狭缝st1。

在本实施例中,像素电极PE具有两个第二狭缝st2以及一个第一狭缝st1,两个第二狭缝st2分别连接第一狭缝st1的两端,并构成H形的封闭图案cp。

在本实施例中,子像素结构在配向过程中会形成多个+1节点N1以及多个-1节点N2。沿着+1节点N1周围以顺时针方向绕一圈,液晶分子的倾倒方向也会以顺时针方向绕一圈。沿着-1节点N2周围以顺时针方向绕一圈,液晶分子的倾倒方向则会以逆时针方向绕一圈。

在本实施例中,第一狭缝st1中具有两个第一凸起R1。两个第一凸起R1位于第一狭缝st1的两侧,且两个第一凸起R1在第二方向DR2上互相对齐。通过第一凸起R1的设置,能增加第一狭缝st1上的缺陷点的数量,并使暗纹位置更稳定,并能降低暗纹对显示画面造成的影响。

在本实施例中,像素电极PE具有四个第二凸起R2。四个第二凸起R2分别位于像素电极PE的四个角落。第二凸起R2能使像素电极PE边缘的暗纹位置更稳定,并能降低暗纹对显示画面造成的影响。

在本实施例中,像素电极PE的连接部P5具有通孔TH。通孔TH位于第一共用电极CE1的两个延伸部EP之间。通孔TH能使连接部P5处的暗纹位置更稳定,并能降低暗纹对显示画面造成的影响。

在本实施例中,像素电极PE的第一部分P1的尺寸约等于第二部分P2的尺寸,但本发明不以此为限。在其他实施例中,像素电极PE的第一部分P1的尺寸不等于第二部分P2的尺寸。

图4A为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。图4B为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。在此必须说明的是,图4A与图4B的实施例沿用图3的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

图4A的像素电极PE与图3的像素电极PE的差异在于:图4A的像素电极PE的第一部分P1的尺寸不等于第二部分P2的尺寸。

请参考图4A与图4B,第一部分P1的面积与第二部分P2的面积的比例约为2:1。

在本实施例中,第一狭缝st1上的缺陷点DP的数量为3个。

图5A为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。图5B为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。在此必须说明的是,图5A与图5B的实施例沿用图3的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

图5A的像素电极PE与图3的像素电极PE的差异在于:图5A的像素电极PE的第一部分P1的尺寸不等于第二部分P2的尺寸。

请参考图5A与图5B,第一部分P1的面积与第二部分P2的面积的比例约为5:1。

在本实施例中,第一狭缝st1上的缺陷点DP的数量为3个。

图6A为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。图6B为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。在此必须说明的是,图6A与图6B的实施例沿用图3的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

图6A的像素电极PE与图3的像素电极PE的差异在于:图6A的像素电极PE的第一部分P1的尺寸不等于第二部分P2的尺寸。

请参考图6A与图6B,第一部分P1的面积与第二部分P2的面积的比例约为7:1。

在本实施例中,第一狭缝st1上的缺陷点的数量为3个。

图7为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。在此必须说明的是,图7的实施例沿用图4A的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

图7的像素电极PE与图4A的像素电极PE的差异在于:图7的像素电极PE包括两个第一狭缝st1。

在本实施例中,两个第二狭缝st2分别位于两个第一狭缝st1的两端,且两个第一狭缝st1在第一方向DR1上互相对齐。

图8A为本发明的一实施例的一种液晶面板的俯视示意图。图8B为图8A的像素电极以及第一共用电极的俯视示意图。图8C为本发明的一实施例的一种子像素结构对液晶层进行配向程序时的液晶效果的模拟图。在此必须说明的是,图8A与图8B的实施例沿用图1A至图1C的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

请参考图8A与图8B,像素电极PE具有封闭图案cp。封闭图案cp指的是未与像素电极PE的边缘连接的图案,即封闭图案cp与像素电极PE的边缘隔有一距离。封闭图案cp包括至少一第一狭缝st1以及至少两个第二狭缝st2。在本实施例中,封闭图案cp包括两个第一狭缝st1以及两个第二狭缝st2。两个第一狭缝st1沿着第一方向DR1延伸,且在第一方向DR1上彼此对齐。第二狭缝st2沿着第二方向DR2延伸,第二方向DR2实质上正交于第一方向DR1。

在本实施例中,数据线DL沿着第一方向DR1延伸,且扫描线SL沿着第二方向DR2延伸。换句话说,第一狭缝st1实质上平行于数据线DL,且第二狭缝st2实质上平行于扫描线SL。

第二狭缝st2分别位于第一狭缝st1的两端。在本实施例中,两个第二狭缝st2分别位于两个第一狭缝st1的两端,且第二狭缝st2与对应的第一狭缝st1相连。在本实施例中,第一狭缝st1的宽度为Lm,第二狭缝st2的宽度为Ls,3≥Lm/CG≥2,且0.75≥Ls/CG≥0.4,其中CG为液晶层的厚度。

在本实施例中,在第一方向DR1上第二狭缝st2与像素电极PE的上侧之间的间距DS4介于3微米至4微米。在本实施例中,在第一方向DR1上第二狭缝st2与像素电极PE的下侧之间的间距DS5介于3微米至4微米。在本实施例中,在第二方向DR2上第二狭缝st2与像素电极PE的边缘(像素电极PE的左侧与右侧)之间的间距DS6介于2.5微米至3.5微米。

在本实施例中,封闭图案cp为对称图案,且封闭图案cp的对称轴平行于第二方向DR2。

在本实施例中,像素电极PE包括的第一部分P1、第二部分P2、第三部分P3、第四部分P4以及连接部P5。第一部分P1在第二方向DR2上位于第一狭缝st1的一侧(左侧),且第二部分P2在第二方向DR2上位于第一狭缝st1的另一侧(右侧)。第三部分P3在第一方向DR1上位于第一狭缝st1以及第二狭缝st2的一侧(上侧),且第四部分P4在第一方向DR1上位于第一狭缝st1以及第二狭缝st2的另一侧(下侧)。连接部P5连接第四部分P4至有源元件T。在本实施例中,其中一个第二狭缝st2位于第一部分P1与第三部分P3之间以及第二部分P2与第三部分P3之间,且另外一个第二狭缝st2位于第一部分P1与第四部分P4之间以及第二部分P2与第四部分P4之间。在本实施例中,第三部分P3连接第一部分P1与第二部分P2,且第四部分P4连接第一部分P1与第二部分P2。

在本实施例中,像素电极PE的第一部分P1的尺寸约等于第二部分P2的尺寸,但本发明不以此为限。在其他实施例中,像素电极PE的第一部分P1的尺寸不等于第二部分P2的尺寸。

请参考图8B,第一共用电极CE1包围像素电极PE。子像素结构sp具有未重叠于黑矩阵的开口区OP。在本实施例中,在子像素结构sp的开口区OP中,在第一方向DR1上第一共用电极CE1与像素电极PE(像素电极PE的第三部分P3与第四部分P4)之间的间距为a,且在第二方向DR2上第一共用电极CE1与PE像素电极PE(像素电极PE的第一部分P1与第二部分P2)之间的间距为b,a/CG≥1.4,1.3≥b/CG≥1。

在本实施例中,第一共用电极CE1包括外框部OS以及两个延伸部EP。外框部OS环绕像素电极PE。两个延伸部连接该外框部OS,且自外框部OS朝向像素电极PE的第五部分P5延伸。像素电极PE的第五部分P5穿过两个延伸部EP之间的间隙GP。在本实施例中,外框部OS具有重叠于数据线DL的开口H。

请参考图8C,第一狭缝st1的边缘与像素电极PE左右两侧的边缘皆有暗纹产生。在本实施例中,第一狭缝st1上会有缺陷点(Defect point)DP产生,缺陷点DP例如是出现在暗纹交叉的位置。在本实施例中,第一狭缝st1上的缺陷点DP的数量为3个。

通过第一狭缝st1以及第二狭缝st2的设置,能使子像素内的暗纹位置更稳定,由此降低暗纹对显示画面造成的影响。

图9为本发明的一实施例的一种像素电极以及第一共用电极的俯视示意图。在此必须说明的是,图9的实施例沿用图8A至图8C的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

在图9中,箭头的指向代表的是液晶分子在配向过程中的倾倒方向。

图9的像素电极PE与图8B的像素电极PE的差异在于:图9的像素电极PE具有第二凸起R2以及通孔TH。

在本实施例中,在像素电极PE的第一部分P1上的液晶层300的配向方向约平行于第一配向方向AD1,在像素电极PE的第二部分P2上的液晶层300的配向方向约平行于第二配向方向AD2,其中第一配向方向AD1与第二配向方向AD2指的是液晶分子在配向过程中的倾倒方向。

本实施例中,在配向过程中于第一狭缝st1上的液晶层300约朝向像素电极PE的上下两侧倾倒。换句话说,第一狭缝st1上的液晶层300的配向方向约平行于第三配向方向AD3与第四配向方向AD4,第三配向方向AD3与第四配向方向AD4约彼此相反,且第三配向方向AD3与第四配向方向AD4约平行于第一方向DR1。

在本实施例中,子像素结构在配向过程中会形成多个+1节点N1以及多个-1节点N2。沿着+1节点N1周围以顺时针方向绕一圈,液晶分子的倾倒方向也会以顺时针方向绕一圈。沿着-1节点N2周围以顺时针方向绕一圈,液晶分子的倾倒方向则会以逆时针方向绕一圈。

在本实施例中,像素电极PE具有四个第二凸起R2。四个第二凸起R2分别位于像素电极PE的四个角落。第二凸起R2能使像素电极PE边缘的暗纹位置更稳定,并能降低暗纹对显示画面造成的影响。

在本实施例中,像素电极PE的连接部P5具有通孔TH。通孔TH位于第一共用电极CE1的两个延伸部EP之间。通孔TH能使连接部P5处的暗纹位置更稳定,并能降低暗纹对显示画面造成的影响。