一种多片FPGA系统及其时戳同步方法

文献发布时间:2023-06-19 13:48:08

技术领域

本发明涉及电力工程继电保护自动化技术领域,尤其涉及一种多片FPGA系统及其时戳同步方法。

背景技术

随着继电保护技术的不断发展,数据的处理量和处理算法复杂程度都显著增加;同时,为了确保芯片等元器件供应的稳定性,需要做多种平台的产品,某些FPGA芯片的片内资源较少,而资源丰富的芯片价格较高且供应有不确定性;在多种因素的制约下,提出了一个板卡上需要贴装多片FPGA的需求,而芯片之间的有些功能又是紧密联系,互为协作的;

在FPGA的研发过程中,时序尤为重要;当多片FPGA芯片协作时,同步问题需要特别考虑,包括:复位同步、时钟同步以及时间同步;在时间同步的基础上甚至需要做到时戳同步,即多个FPGA芯片内的时间计数器步调一致,Tick数相同。在继电保护领域,存在一些周期性的报文,例如ft3报文等,需要做预发机制:处理器读取主FPGA的当前时戳,加一定余量后将预发时刻写入描述符,告知从FPGA该报文的发送时刻,从FPGA芯片在时戳计数器计时到预发时刻后发送;一个业务的不同环节工作在多个FPGA芯片中,这种工况必须保证这些芯片中的时戳保持同步,否则会出现预发不成功等异常;在报文接收的工况中也存在这种需求,例如SV报文重采样:负责SV报文接收的从FPGA给报文打上当前时戳发送给处理器,处理器以调频秒脉冲为基准进行重采样,而调频秒脉冲是主FPGA根据自身的时戳计数器产生的,同样必须保证主从芯片中的时戳同步。

因此,如何严格的保证多FPGA芯片之间的时戳同步,成为此类应用场景中迫切需要解决的问题。

发明内容

基于现有技术的上述情况,本发明的目的在于提供一种多片FPGA系统及其时戳同步方法,通过将多片FPGA系统中多片FPGA芯片的信号相互联系,使得开发环境能够前后串联起来进行静态时序分析,同时考虑外部电磁干扰的影响,从而保证多片FPGA芯片之间的时戳同步。

为达到上述目的,根据本发明的一个方面,提供了一种多片FPGA系统,包括多片FPGA芯片和一个晶振;

所述多片FPGA芯片和晶振的布局采用星形结构;

所述晶振设置于该星形结构的中心,且至各片FPGA芯片的布线距离相同,以使所述晶振的时钟信号达到各片FPGA芯片的相位一致。

进一步的,所述多片FPGA芯片包括一片主FPGA芯片和多片从FPGA芯片。

根据本发明的另一个方面,提供了一种基于多片FPGA系统的时戳同步方法,所述多片FPGA系统包括如权利要求2所述的多片FPGA系统;

该同步方法包括由各从FPGA芯片执行如下步骤:

S1、计数器清零;

S2、计数器计数;

S3、判断是否收到主FPGA发送的同步脉冲,并根据判断结果来对时戳计数器进行同步调整。

进一步的,所述根据判断结果来对时戳计数器进行同步调整包括:

S31、判断是否收到主FPGA发送的第一同步脉冲,若是,则返回步骤S1;若否,则执行步骤S32;

S32、判断是否收到主FPGA发送的第二同步脉冲,若是,则执行步骤S33;若否,则返回步骤S2;

S33、判断时戳计数器的低30位是否大于或等于0X3FFFFF7,若是,则执行步骤S34;若否,则跳转至步骤S35;

S34、时戳计数器的高2位加1;

S35、时戳计数器的低30位清0,并返回步骤S2。

进一步的,在步骤S1之前,各从FPGA芯片根据主FPGA芯片发送的同步复位信号进行复位释放。

进一步的,主FPGA芯片根据各从FPGA芯片输出的加载完成信号生成该同步复位信号。

进一步的,所述主FPGA芯片根据各从FPGA芯片输出的加载完成信号生成该同步复位信号,包括根据以下公式生成该同步复位信号:

RST=DONE1 AND DONE2 AND…AND DONEn

其中,RST为同步复位信号,DONE1、DONE2、……、DONEn为n个从FPGA芯片输出的加载完成信号。

进一步的,所述第一同步脉冲的周期为2

进一步的,所述第二同步脉冲的周期为2

综上所述,本发明提供了一种多片FPGA系统及其时戳同步方法,通过使用单一时钟源及搭建一个星型结构,保证时钟相位一致、频偏为0;并且同时综合考虑加载完成信号,保证复位释放时间一致;通过对主芯片输出同步脉冲和从芯片输入同步脉冲进行约束,保证同步脉冲同步;通过同步脉冲的设计,保证对时戳计数器实时监视和同步。本发明的技术方案有效解决了多片FPGA协作的工况下时戳同步的问题,并且简单可靠容易实施。

附图说明

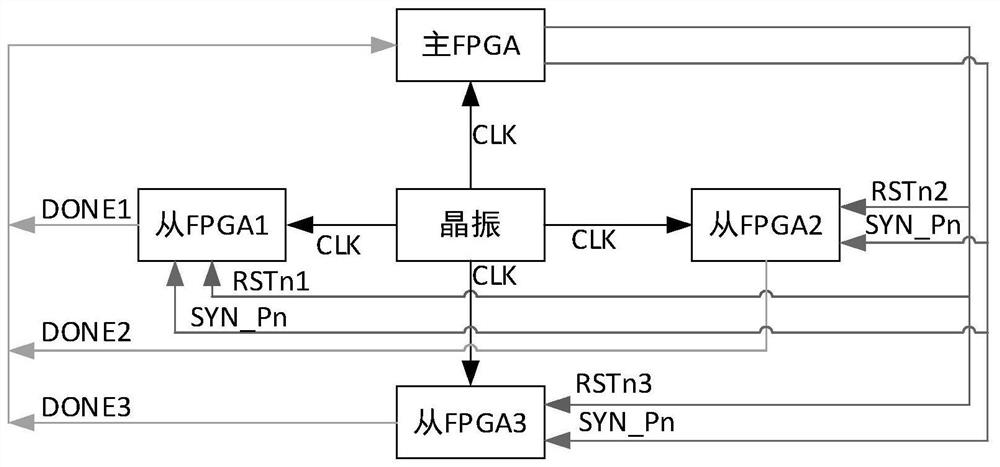

图1是本发明多片FPGA系统的构成示意图;

图2是本发明基于多片FPGA系统的时戳同步方法的流程图;

图3是m=3时的同步脉冲时序图;

图4是m=3时的随机变量X的概率分布及分布函数图;

图5是同步脉冲约束参数时序图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明了,下面结合具体实施方式并参照附图,对本发明进一步详细说明。应该理解,这些描述只是示例性的,而并非要限制本发明的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本发明的概念。

在FPGA芯片内部,信号处于同一主时钟域时,开发环境能够对其进行静态时序分析,且芯片内部不易受外部电磁环境干扰,所以各个模块使用的时戳是一致的。根据以上原理,本发明提供了一种多片FPGA系统及其时戳同步方法,通过将多个FPGA芯片的信号联系起来,使得开发环境同样能够前后串联起来进行静态时序分析,同时考虑外部电磁干扰的影响,从而保证多片FPGA芯片之间的时戳同步。

下面将结合附图对本发明的技术方案进行详细说明。根据本发明的一个实施例,提供了一种多片FPGA系统,该系统的构成示意图如图1所示,包括多片FPGA芯片和一个晶振;所述多片FPGA芯片和晶振的布局采用星形结构;所述晶振设置于该星形结构的中心,且至各片FPGA芯片的布线距离相同,以使所述晶振的时钟信号达到各片FPGA芯片的相位一致,并且所述多片FPGA芯片包括一片主FPGA芯片和多片从FPGA芯片。如图1所示,以共有4片FPGA芯片为例,其中有1片主FPGA芯片和3片从FPGA芯片,该4片FPGA芯片与位于中心的晶振共同构成星形结构,所述晶振设置于该星形结构的中心,且至各片FPGA芯片的布线距离相同,以使所述晶振的时钟信号达到各片FPGA芯片的相位一致。通过建立多片FPGA的系统同步关系,即外部使用同一个时钟源,保证没有频偏产生。

根据本发明的另一个实施例,提供了一种基于多片FPGA系统的时戳同步方法,所述多片FPGA系统包括如本发明第一个实施例所述的多片FPGA系统,该方法的流程图如图2所示,该同步方法包括由各从FPGA芯片执行如下步骤:

S1、计数器清零;

S2、计数器计数;

S3、判断是否收到主FPGA发送的同步脉冲,并根据判断结果来对时戳计数器进行同步调整。

其中,根据判断结果来对时戳计数器进行同步调整包括以下步骤:

S31、判断是否收到主FPGA发送的第一同步脉冲,若是,则返回步骤S1;若否,则执行步骤S32;所述第一同步脉冲的周期可以为2

S32、判断是否收到主FPGA发送的第二同步脉冲,若是,则执行步骤S33;若否,则返回步骤S2。所述第二同步脉冲的周期为2

S33、判断时戳计数器的低30位是否大于或等于0X3FFFFF7,若是,则执行步骤S34;若否,则跳转至步骤S35;

S34、时戳计数器的高2位加1;

S35、时戳计数器的低30位清0,并返回步骤S2。

进一步的,在步骤S1之前,各从FPGA芯片根据主FPGA芯片发送的同步复位信号进行复位释放。其中,主FPGA芯片根据各从FPGA芯片输出的加载完成信号生成该同步复位信号。各个从FPGA芯片的程序加载完成信号DONE(高有效)分别连接至主FPGA芯片,主FPGA芯片根据木桶效应,在所有芯片加载完成之后释放复位信号,并通过外部布线将该信号传输给各个从芯片,各个从芯片开始时戳计数器的计数;本实施例中,复位信号RSTn(低有效)例如可以按照VHDL语句获取最晚释放时刻:

RSTn<=DONE1 and DONE2 and DONE3 (1)

其中,DONE1、DONE2、DONE3分别为3个从FPGA芯片发出的程序加载完成信号。

根据本实施例所提供的时戳同步方法,多片FPGA系统中每一个FPGA芯片内部都进行时戳计数,由主FPGA芯片负责生成同步脉冲信号,并发送给从FPGA芯片;从FPGA芯片根据同步脉冲对时戳计数器进行监视和同步化。

每一个计数间隔内由于受到外部电磁环境对时钟信号的干扰,某一个FPGA芯片的计数器,相比正常环境下的时戳计数器会额外增加计数量X,X服从泊松分布X~P(λ);根据预发业务和重采样业务能够容忍的最大误差,以及快速瞬变试验中脉冲群的频率确定随机变量X的参数λ,以及一个计数周期内同步脉冲个数n的大小;通过特定约束告知开发环境同步脉冲信号的输出信号时延、输入信号时延等时延参数,外部布线时延由于距离很近不予考虑,以此保证同步脉冲信号同步。以下进行进一步说明。

在一个平稳的电磁环境中,若没有同步脉冲监视,一定时间内时戳计数器在随机干扰的作用下会产生累计X个tick数的误差,X服从均值为λ的泊松分布,其概率分布为:

本实施例中,时戳计数器位宽为32bit,自翻转,主时钟为50MHz;使用n个同步脉冲进行监视,令n=2

当m=3时,同步脉冲时序如图3所示,其中,SYN1为第一同步脉冲,SYN2为第一同步脉冲。根据GB/T 17626.4-2008/IEC 61000-4-4:2004,电快瞬脉冲群周期为300ms,假定每一次脉冲群随机造成平均0.5次的有效主时钟干扰,产生0.5tick的时戳计数器增加,即每300ms会平均累计产生0.5tick误差;则在相邻的两个同步脉冲之间,会随机产生X个计数的误差累积,其均值为,

其中,T为主时钟周期20ns;将公式(3)带入公式(2)可得X的概率分布,根据概率分布与分布函数的关系可得,

根据实际业务需求,预发业务能够容忍100us误差,重采样业务能够容忍1us误差;则该系统设计容忍误差最大为1us,即50个tick;令公式(4)中k=50;则有,

例如,将m∈{1,2,3,4,5,6}带入公式(5)取得结果如表1所示,

表1

根据表1概率,本实例选择m=3,同步脉冲信号如图3所示,此时随机变量X的概率分布及分布函数如图4所示,可以看出时戳计数器累积误差大部分落在区间[25,45];当k=45时,F(X=45)=0.92,即有0.08的概率时戳累积误差超过45;当k=50时,F(X=50)=0.99,有0.01的概率时戳累积误差超过50。

同步脉冲信号由主FPGA芯片生成,传输给从FPGA芯片。若不加输入输出约束,由于输出端相对主钟的时延不确定,经过外部布线之后有可能会在从芯片中产生亚稳态或者1个tick的时戳计数延迟;按照图5所示的参数对同步脉冲信号进行输入输出约束,由于多片芯片在一个板卡,布线设计中板上信号延迟需要在1ns以内,所以输入输出参数有1ns的余量;通过约束语句告知开发环境同步脉冲从主芯片到从芯片的时延参数,保证了从芯片的建立保持时间。至此从芯片接收到了符合时序要求同步脉冲,第一同步脉冲SYN1保证时戳计数器起始位置同步,第二SYN2监视同步计数器中间时刻的同步,减小累积误差;具体按照图2的流程进行时戳计数并同步:复位释放后,时戳计数器从0开始计数;接收到图3中第一同步脉冲SYN1时,计数器清零;接收到第二同步脉冲SYN2时,判定时戳计数器低30bit值;当大于0X3FFF FFF7时,判定需要进位,高2bit加1处理,低30bit清零;当时戳计数器为其他值时,直接清零计数器;其他情况计数器循环计数及判定同步脉冲是否到达。

综上所述,本发明涉及一种多片FPGA系统及其时戳同步方法,通过使用单一时钟源及搭建一个星型结构,保证时钟相位一致、频偏为0;并且同时综合考虑加载完成信号,保证复位释放时间一致;通过对主芯片输出同步脉冲和从芯片输入同步脉冲进行约束,保证同步脉冲同步;通过同步脉冲的设计,保证对时戳计数器实时监视和同步。本发明的技术方案有效解决了多片FPGA协作的工况下时戳同步的问题,并且简单可靠容易实施。

本领域内的技术人员应明白,本发明的实施例可提供为方法、系统、或计算机程序产品。因此,本发明可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本发明可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、CD-ROM、光学存储器等)上实施的计算机程序产品的形式。

本发明是参照根据本发明实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

最后应当说明的是:以上实施例仅用于说明本发明的技术方案而非对其保护范围的限制,尽管参照上述实施例对本发明进行了详细的说明,所属领域的普通技术人员应当理解:本领域技术人员阅读本发明后依然可对发明的具体实施方式进行种种变更、修改或者等同替换,但这些变更、修改或者等同替换,均在发明待批的权利要求保护范围之内。

- 一种多片FPGA系统及其时戳同步方法

- 分布式存储系统及其时间戳的实现方法